第28卷第12期 半导体学报 Vol.28 No.12 2007年12月 CHINESE JOURNAL OF SEMICONDUCTORS Dec.,2007 一种应用于频率综合器的高性能全差分电荷泵电路 杨振宇唐长文闵昊 (复旦大学专用集成电路与系统国家重点实验室,上海201203) 摘要:提出了一种应用于频率综合器的全差分电荷泵电路.该电荷泵结构可以很好地克服沟道长度调制效应的影 响,使充放电电流在宽输出电压范围内实现精确匹配,从而使频率综合器的压控电压纹波(ripple)很小,为了保证 电荷泵的宽输出摆幅不受限制,还设计了一种输入范围接近轨到轨的共模负反馈电路.整个电路在1.8 V SMIC 0.18 m CMOS混合信号工艺下设计实现,芯片面积约为450um×280m,直流功耗约为1mW,测试得到的参考杂 散的最差值为-73dBc,满足频率综合器的低杂散要求, 关键词:频率综合器:全差分电荷泵;电流匹配;电流复制:电压纹波:杂散 EEACC:1205:1280:2570D 中图分类号:TN4 文献标识码:A 文章编号:0253-4177(2007)12-1993-06 1引言 2 传统全差分电荷泵电路 为了克服单端电荷泵固有的输出动态范围小、 基于锁相环的频率综合器电路被广泛使用在射 充放电电流匹配性能差以及时钟馈通效应明显等缺 频收发机通信系统中.典型的频率综合器系统包括 点,高性能频率综合器普遍采用共源共栅(cascode) 鉴频鉴相器(PFD)、电荷泵(charge pump)、环路滤 的全差分电荷泵结构,该结构电路如图1所示. 波器(loop filter)、压控振荡器(VCO)以及分频器 管子M1~M20构成cascode电流镜,可以提 (divider)等模块.电荷泵电路是其中最关键的模块 高电荷泵的输出阻抗,降低管子漏端电压对电流的 之一,它的功能是将鉴频鉴相器输出的相差脉宽数 影响,使电荷泵充放电电流的匹配性能得到改善;管 字信号(up和dn)通过充放电电流(Ip和Iam)转化 子M21~M24是电荷泵的源极开关,可以使电荷泵 为电流信号,然后通过环路滤波器变为电压信号 以最快速度开启和关闭,降低参考时钟引入的馈通 V,从而对压控振荡器的工作频率进行调整.因 噪声;管子M25~M30匹配开关管使电荷泵 此,一旦电荷泵中的非理想因素使充电电流I和放 (charge pump)支路和偏置支路(bias)实现完全匹 电电流Ih之间存在不匹配,压控电压V上就会产 配;电容C1,C2减弱开关时钟馈通效应的影响.这种 生电压纹波(ripple),导致压控振荡器输出频谱上 电荷泵存在两个缺陷:(1)cascode全差分电荷泵的 产生杂散(spu),从而造成对临近信道的干扰[们. cascode管子限制了输出摆幅,这在低电源电压工作 为了提高电荷泵的电流匹配性能,全差分电荷 环境下是不利的;(2)当控制电压Vp和Vm差值较大 泵结构被广泛应用在频率综合器系统中.但是,传统 时,差分电荷泵的充放电电流匹配性能严重恶化, 的全差分电荷泵电路由于采用共源共栅(cascode) 假设控制电压Vp和Vm分别满足 结构2~],输出摆幅受到限制,而且由于沟道长度调 Va Vm+Viu,Va Vo Vau 2 2 (1) 制效应的影响,电荷泵差分电流的匹配性能被严重 恶化,甚至不如单端电流的匹配性能.本文提出了一 其中Vm是Vp和Vm的共模电压;Va是Vcn和 种全差分电荷泵电路,该电路在不降低输出电压摆 V的差模电压.当差模电压V不等于零时,由于 幅的前提下,采用电流复制(replica)技术使差分电 沟道长度调制效应的影响,图1中的电流源Ip, 荷泵的充放电电流的匹配性能得到很大改善,从而 In1,I2和I2的大小会发生变化.如图2所示,假 克服了传统电荷泵的缺陷, 设Im表示当差模电压Vr等于零(Vp=Vm= Vm)时电荷泵的充放电电流值。 t通信作者.Email:zwtang@fudan.cdu.cn 2007-06-04收到,2007-07-08定稿 ©2007中国电子学会

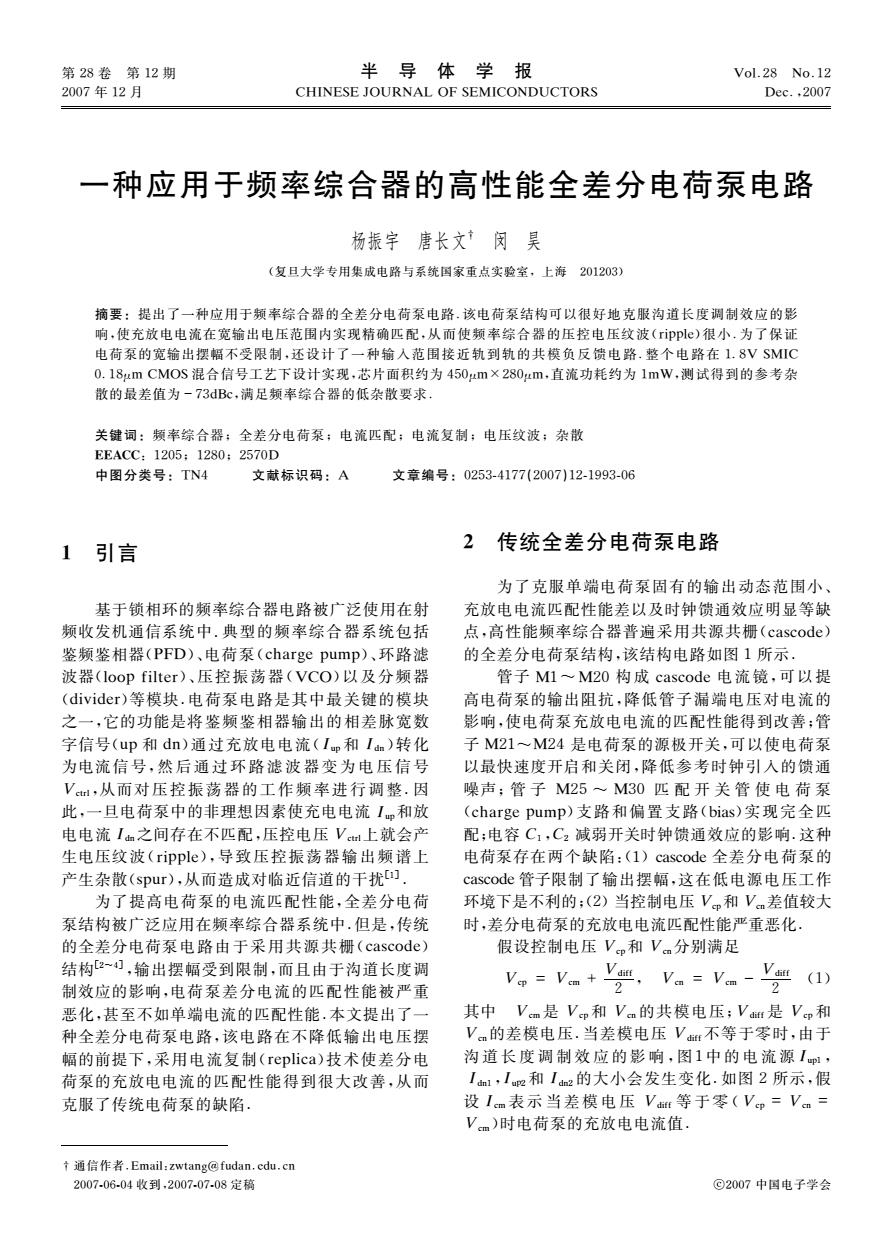

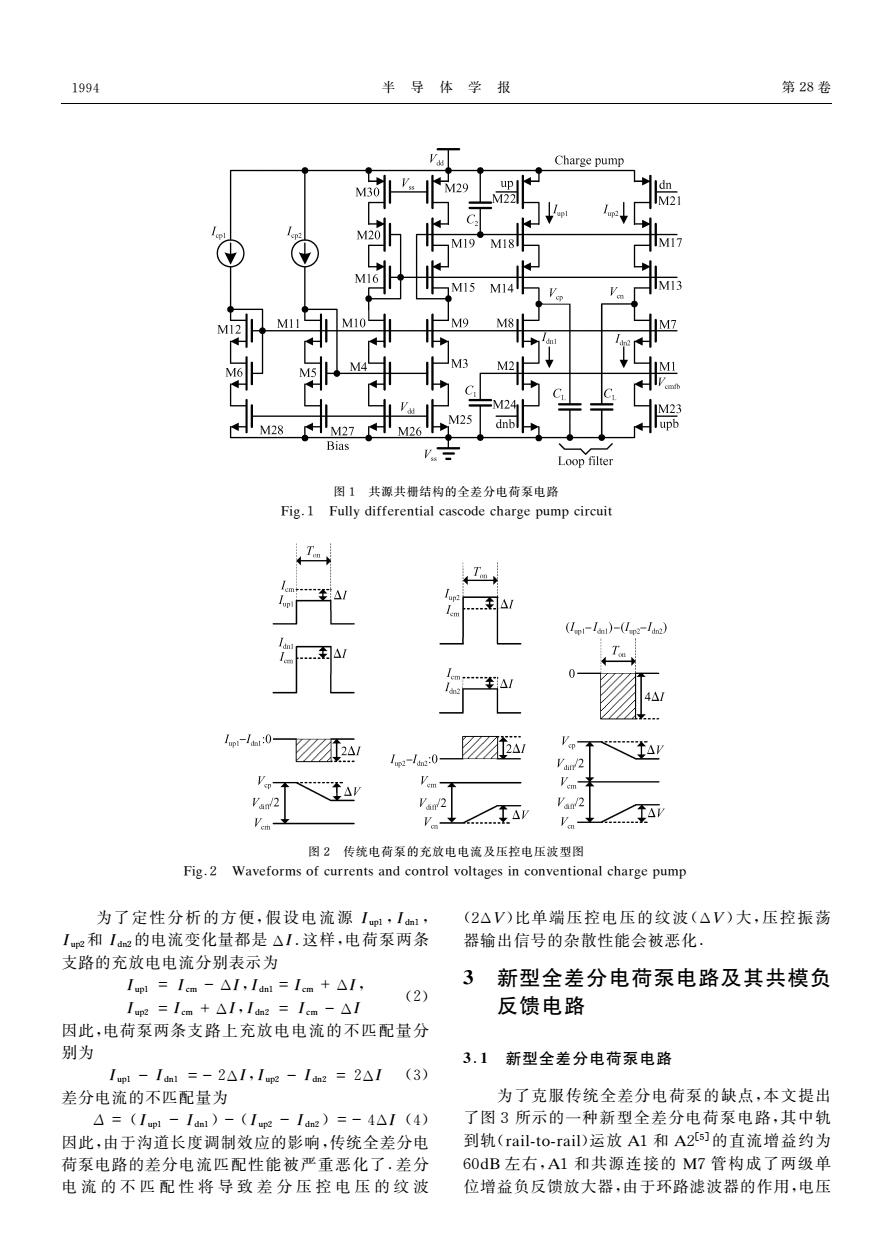

第28卷 第12期 2007年12月 半 导 体 学 报 犆犎犐犖犈犛犈犑犗犝犚犖犃犔犗犉犛犈犕犐犆犗犖犇犝犆犜犗犚犛 犞狅犾.28 犖狅.12 犇犲犮.,2007 通信作者.犈犿犪犻犾:狕狑狋犪狀犵@犳狌犱犪狀.犲犱狌.犮狀 20070604收到,20070708定稿 2007 中国电子学会 一种应用于频率综合器的高性能全差分电荷泵电路 杨振宇 唐长文 闵 昊 (复旦大学专用集成电路与系统国家重点实验室,上海 201203) 摘要:提出了一种应用于频率综合器的全差分电荷泵电路.该电荷泵结构可以很好地克服沟道长度调制效应的影 响,使充放电电流在宽输出电压范围内实现精确匹配,从而使频率综合器的压控电压纹波(狉犻狆狆犾犲)很小.为了保证 电荷泵的宽输出摆幅不受限制,还设计了一种输入范围接近轨到轨的共模负反馈电路.整个电路在18犞犛犕犐犆 018μ犿犆犕犗犛混合信号工艺下设计实现,芯片面积约为450μ犿×280μ犿,直流功耗约为1犿犠,测试得到的参考杂 散的最差值为-73犱犅犮,满足频率综合器的低杂散要求. 关键词:频率综合器;全差分电荷泵;电流匹配;电流复制;电压纹波;杂散 犈犈犃犆犆:1205;1280;2570犇 中图分类号:犜犖4 文献标识码:犃 文章编号:02534177(2007)12199306 1 引言 基于锁相环的频率综合器电路被广泛使用在射 频收发机通信系统中.典型的频率综合器系统包括 鉴频鉴相器(犘犉犇)、电荷泵(犮犺犪狉犵犲狆狌犿狆)、环路滤 波器(犾狅狅狆犳犻犾狋犲狉)、压控振荡器(犞犆犗)以及分频器 (犱犻狏犻犱犲狉)等模块.电荷泵电路是其中最关键的模块 之一,它的功能是将鉴频鉴相器输出的相差脉宽数 字信号(狌狆和犱狀)通过充放电电流(犐狌狆和犐犱狀)转化 为电流信 号,然 后 通 过 环 路 滤 波 器 变 为 电 压 信 号 犞犮狋狉犾,从而对压控振荡器的工作频率 进 行 调 整.因 此,一旦电荷泵中的非理想因素使充电电流犐狌狆和放 电电流犐犱狀之间存在不匹配,压控电压 犞犮狋狉犾上就会产 生电压纹波(狉犻狆狆犾犲),导致压控振荡器输出频谱上 产生杂散(狊狆狌狉),从而造成对临近信道的干扰[1] . 为了提高电荷泵的电流匹配性能,全差分电荷 泵结构被广泛应用在频率综合器系统中.但是,传统 的全差分电荷泵电路由于采用共源共栅(犮犪狊犮狅犱犲) 结构[2~4],输出摆幅受到限制,而且由于沟道长度调 制效应的影响,电荷泵差分电流的匹配性能被严重 恶化,甚至不如单端电流的匹配性能.本文提出了一 种全差分电荷泵电路,该电路在不降低输出电压摆 幅的前提下,采用电流复制(狉犲狆犾犻犮犪)技术使差分电 荷泵的充放电电流的匹配性能得到很大改善,从而 克服了传统电荷泵的缺陷. 2 传统全差分电荷泵电路 为了克服单端电荷泵固有的输出动态范围小、 充放电电流匹配性能差以及时钟馈通效应明显等缺 点,高性能频率综合器普遍采用共源共栅(犮犪狊犮狅犱犲) 的全差分电荷泵结构,该结构电路如图1所示. 管子 犕1~犕20 构成 犮犪狊犮狅犱犲电流镜,可以提 高电荷泵的输出阻抗,降低管子漏端电压对电流的 影响,使电荷泵充放电电流的匹配性能得到改善;管 子 犕21~犕24 是电荷泵的源极开关,可以使电荷泵 以最快速度开启和关闭,降低参考时钟引入的馈通 噪声;管 子 犕25~ 犕30 匹 配 开 关 管 使 电 荷 泵 (犮犺犪狉犵犲狆狌犿狆)支路和偏置支路(犫犻犪狊)实现完全匹 配;电容 犆1,犆2 减弱开关时钟馈通效应的影响.这种 电荷泵存在两个缺陷:(1)犮犪狊犮狅犱犲全差分电荷泵的 犮犪狊犮狅犱犲管子限制了输出摆幅,这在低电源电压工作 环境下是不利的;(2)当控制电压犞犮狆和犞犮狀差值较大 时,差分电荷泵的充放电电流匹配性能严重恶化. 假设控制电压 犞犮狆和 犞犮狀分别满足 犞犮狆 = 犞犮犿 +犞犱犻犳犳 2 , 犞犮狀 = 犞犮犿 -犞犱犻犳犳 2 (1) 其中 犞犮犿 是 犞犮狆和 犞犮狀的共模电压;犞犱犻犳犳是 犞犮狆和 犞犮狀的差模电压.当差模电压 犞犱犻犳犳不等于零时,由于 沟 道 长 度 调 制 效 应 的 影 响 ,图1中 的 电 流 源犐狌狆1, 犐犱狀1,犐狌狆2和犐犱狀2的大小会发生变化.如图2所示,假 设犐犮犿 表 示 当 差 模 电 压 犞犱犻犳犳 等 于 零 (犞犮狆 =犞犮狀 = 犞犮犿)时电荷泵的充放电电流值.

1994 半导体学报 第28卷 Charge pump up M22 1 M18 M14 M12 M1( M8 M7 M27 M26 Bias Loop filter 图1共源共栅结构的全差分电荷泵电路 Fig.1 Fully differential cascode charge pump circuit m em/ (I)-(Ip-I2) 2 -:0- s V 1p2-1he:0 Vem- T△ .... Va 图2传统电荷泵的充放电电流及压控电压波型图 Fig.2 Waveforms of currents and control voltages in conventional charge pump 为了定性分析的方便,假设电流源Ip1,I1, (2△V)比单端压控电压的纹波(△V)大,压控振荡 Ie和Ie的电流变化量都是△I.这样,电荷泵两条 器输出信号的杂散性能会被恶化 支路的充放电电流分别表示为 Ipl=Im-△I,Idhl=Iem+△I, 3 新型全差分电荷泵电路及其共模负 (2) Ip2=Icm+△I,Idh2=Im-△1 反馈电路 因此,电荷泵两条支路上充放电电流的不匹配量分 别为 3.1新型全差分电荷泵电路 Ipl-1hl=-2△1,Ipe-Ih2=2△1(3) 差分电流的不匹配量为 为了克服传统全差分电荷泵的缺点,本文提出 △=(Ip1-Idn1)-(Iupe-Idz)=-4△I(4) 了图3所示的一种新型全差分电荷泵电路,其中轨 因此,由于沟道长度调制效应的影响,传统全差分电 到轨(rail-to-rail)运放A1和A2s)的直流增益约为 荷泵电路的差分电流匹配性能被严重恶化了·差分 60dB左右,A1和共源连接的M7管构成了两级单 电流的不匹配性将导致差分压控电压的纹波 位增益负反馈放大器,由于环路滤波器的作用,电压

半 导 体 学 报 第28卷 图1 共源共栅结构的全差分电荷泵电路 犉犻犵.1 犉狌犾犾狔犱犻犳犳犲狉犲狀狋犻犪犾犮犪狊犮狅犱犲犮犺犪狉犵犲狆狌犿狆犮犻狉犮狌犻狋 图2 传统电荷泵的充放电电流及压控电压波型图 犉犻犵.2 犠犪狏犲犳狅狉犿狊狅犳犮狌狉狉犲狀狋狊犪狀犱犮狅狀狋狉狅犾狏狅犾狋犪犵犲狊犻狀犮狅狀狏犲狀狋犻狅狀犪犾犮犺犪狉犵犲狆狌犿狆 为了定性分析的方便,假设电流源 犐狌狆1,犐犱狀1, 犐狌狆2和犐犱狀2的电流变化量都是 Δ犐.这样,电荷泵两条 支路的充放电电流分别表示为 犐狌狆1 =犐犮犿 -Δ犐,犐犱狀1=犐犮犿 +Δ犐, 犐狌狆2 =犐犮犿 +Δ犐,犐犱狀2 =犐犮犿 -Δ犐 (2) 因此,电荷泵两条支路上充放电电流的不匹配量分 别为 犐狌狆1 -犐犱狀1 =-2Δ犐,犐狌狆2 -犐犱狀2 =2Δ犐 (3) 差分电流的不匹配量为 Δ = (犐狌狆1 -犐犱狀1)- (犐狌狆2 -犐犱狀2)=-4Δ犐 (4) 因此,由于沟道长度调制效应的影响,传统全差分电 荷泵电路的差分电流匹配性能被严重恶化了.差分 电 流 的 不 匹 配 性 将 导 致 差 分 压 控 电 压 的 纹 波 (2Δ犞)比单端压控电压的纹波(Δ犞)大,压控振荡 器输出信号的杂散性能会被恶化. 3 新型全差分电荷泵电路及其共模负 反馈电路 3.1 新型全差分电荷泵电路 为了克服传统全差分电荷泵的缺点,本文提出 了图3 所示的一种新型全差分电荷泵电路,其中轨 到轨(狉犪犻犾狋狅狉犪犻犾)运放 犃1和 犃2[5]的直流增益约为 60犱犅左右,犃1和共源连接的 犕7管构成了两级单 位增益负反馈放大器,由于环路滤波器的作用,电压 1994

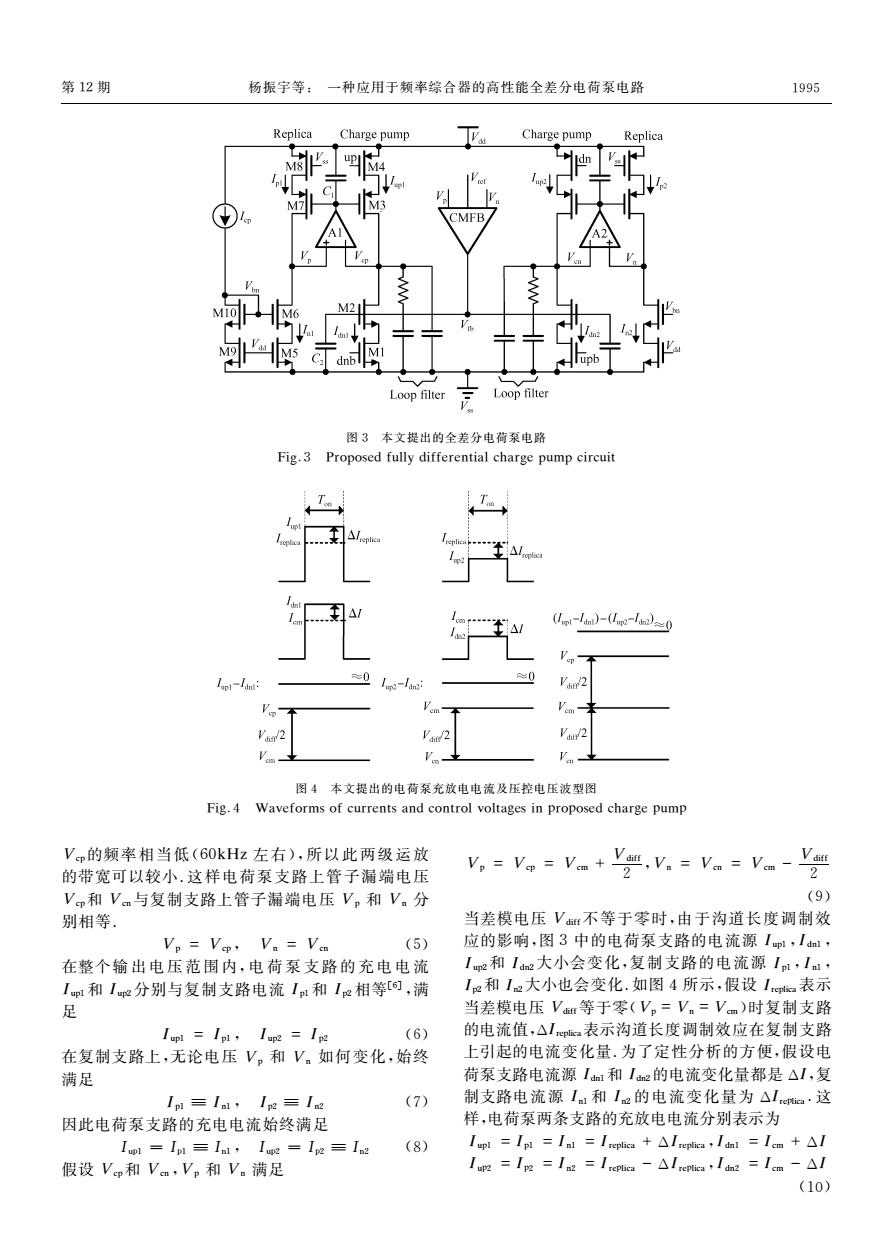

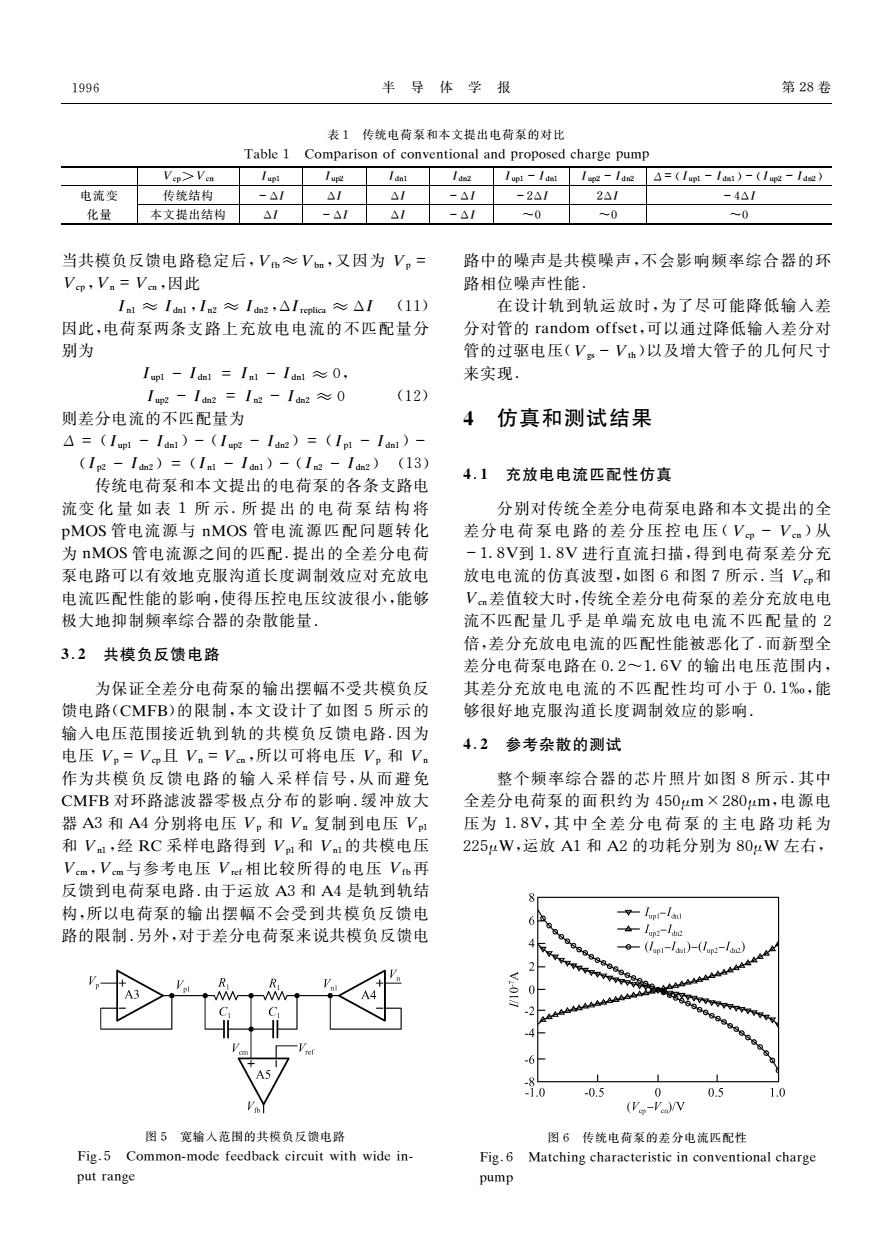

第12期 杨振宇等:一种应用于频率综合器的高性能全差分电荷泵电路 1995 Replica Charge pump Charge pump Replica M8 CMFB Loop filter Loop filter 图3本文提出的全差分电荷泵电路 Fig.3 Proposed fully differential charge pump circuit T A (m-luni)-(ne-lae≈0 Lpl-Jant: ≈0 Tun2-Targ: Van2 Van2 t2 Va2 V 图4本文提出的电荷泵充放电电流及压控电压波型图 Fig.4 Waveforms of currents and control voltages in proposed charge pump Vp的频率相当低(60kHz左右),所以此两级运放 的带宽可以较小.这样电荷泵支路上管子漏端电压 v,=V。=Vm+'要,=V。=Vm-'2 2 Vp和Vm与复制支路上管子漏端电压V。和V。分 (9) 别相等. 当差模电压V不等于零时,由于沟道长度调制效 Vp Ve,Vn =Ve (5) 应的影响,图3中的电荷泵支路的电流源Ip,I, 在整个输出电压范围内,电荷泵支路的充电电流 I和Iae大小会变化,复制支路的电流源Ip1,Im, Ip和Ipe分别与复制支路电流I和Ie相等[o,满 Ie和I2大小也会变化.如图4所示,假设Imia表示 足 当差模电压V等于零(V,=Vm=Vm)时复制支路 Iupl Ipl,Iupe Ipe (6) 的电流值,△Ip表示沟道长度调制效应在复制支路 在复制支路上,无论电压V。和V。如何变化,始终 上引起的电流变化量.为了定性分析的方便,假设电 满足 荷泵支路电流源In1和I2的电流变化量都是△I,复 Ip1=In1,Ip2=I配 (7) 制支路电流源I和I2的电流变化量为△Iea·这 因此电荷泵支路的充电电流始终满足 样,电荷泵两条支路的充放电电流分别表示为 I 01 =Ipl In1,Io02 =Ipe=In2 (8) Ipl=Ipn=Ina=I replica+△replica,Idhl=Icm+△I 假设Vp和Va,V。和V.满足 Ip2=Ipz=I2=I repica-△Ireplica,Idh2=Im-△I (10)

第12期 杨振宇等: 一种应用于频率综合器的高性能全差分电荷泵电路 图3 本文提出的全差分电荷泵电路 犉犻犵.3 犘狉狅狆狅狊犲犱犳狌犾犾狔犱犻犳犳犲狉犲狀狋犻犪犾犮犺犪狉犵犲狆狌犿狆犮犻狉犮狌犻狋 图4 本文提出的电荷泵充放电电流及压控电压波型图 犉犻犵.4 犠犪狏犲犳狅狉犿狊狅犳犮狌狉狉犲狀狋狊犪狀犱犮狅狀狋狉狅犾狏狅犾狋犪犵犲狊犻狀狆狉狅狆狅狊犲犱犮犺犪狉犵犲狆狌犿狆 犞犮狆的频率相当低(60犽犎狕左右),所以此两级运放 的带宽可以较小.这样电荷泵支路上管子漏端电压 犞犮狆和 犞犮狀与复制支路上管子漏端电压 犞狆 和 犞狀 分 别相等. 犞狆 = 犞犮狆, 犞狀 = 犞犮狀 (5) 在整个输 出 电 压 范 围 内,电 荷 泵 支 路 的 充 电 电 流 犐狌狆1和犐狌狆2分别与复制支路电流犐狆1和犐狆2相等[6],满 足 犐狌狆1 =犐狆1, 犐狌狆2 =犐狆2 (6) 在复制支路上,无论电压 犞狆 和 犞狀 如何变化,始终 满足 犐狆1 ≡犐狀1, 犐狆2 ≡犐狀2 (7) 因此电荷泵支路的充电电流始终满足 犐up1 =犐p1 ≡犐n1, 犐up2 =犐p2 ≡犐n2 (8) 假设 犞犮狆和 犞犮狀,犞狆 和 犞狀 满足 犞狆 = 犞犮狆 = 犞犮犿 +犞犱犻犳犳 2 ,犞狀 = 犞犮狀 = 犞犮犿 -犞犱犻犳犳 2 (9) 当差模电压 犞犱犻犳犳不等于零时,由于沟道长度调制效 应的影响,图3 中的电荷泵支路的电流源犐狌狆1,犐犱狀1, 犐狌狆2和犐犱狀2大小会变化,复制支路的电流源犐狆1,犐狀1, 犐狆2和犐狀2大小也会变化.如图4所示,假设犐狉犲狆犾犻犮犪表示 当差模电压 犞犱犻犳犳等于零(犞狆=犞狀=犞犮犿)时复制支路 的电流值,Δ犐狉犲狆犾犻犮犪表示沟道长度调制效应在复制支路 上引起的电流变化量.为了定性分析的方便,假设电 荷泵支路电流源犐犱狀1和犐犱狀2的电流变化量都是 Δ犐,复 制支路电流源犐狀1 和犐狀2 的电流变化量为 Δ犐狉犲狆犾犻犮犪.这 样,电荷泵两条支路的充放电电流分别表示为 犐狌狆1 =犐狆1 =犐狀1 =犐狉犲狆犾犻犮犪 +Δ犐狉犲狆犾犻犮犪,犐犱狀1 =犐犮犿 +Δ犐 犐狌狆2 =犐狆2 =犐狀2 =犐狉犲狆犾犻犮犪 -Δ犐狉犲狆犾犻犮犪,犐犱狀2 =犐犮犿 -Δ犐 (10) 1995

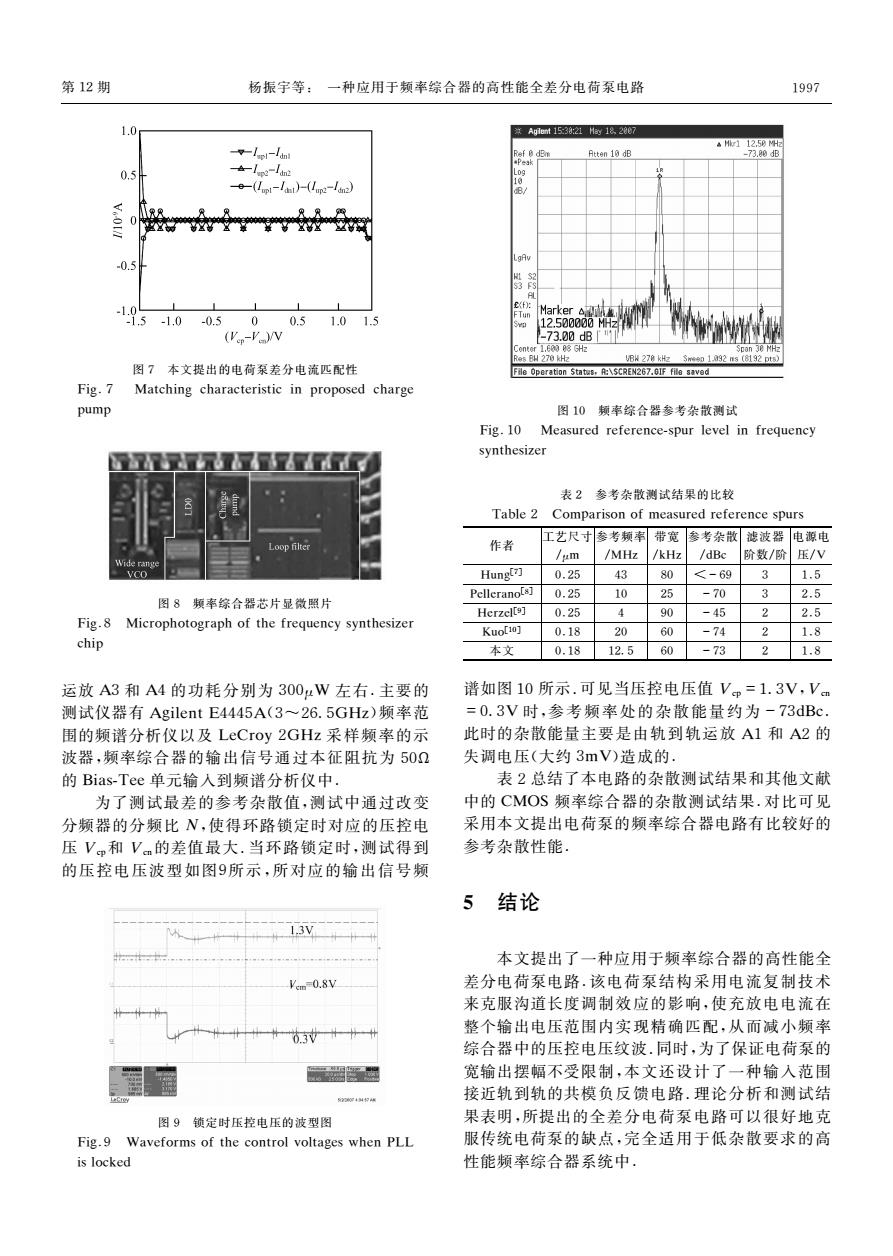

1996 半导体学报 第28卷 表1传统电荷泵和本文提出电荷泵的对比 Table 1 Comparison of conventional and proposed charge pump Vep>Ven Tupl Iug2 Ian1 Ide2 I upt -Idet Tup2-Ian2 △=(Iupl-Ida)-(Iup2-Id2) 电流变 传统结构 -41 AI △I -△I -2AI 2△I -44/ 化量 本文提出结构 4/ -△1 △I -△1 -0 -0 -0 当共模负反馈电路稳定后,Vo≈Vm,又因为V,= 路中的噪声是共模噪声,不会影响频率综合器的环 Vp,V。=Vm,因此 路相位噪声性能 Inl≈Idal,In2≈Idn2,△Ipia≈△I (11) 在设计轨到轨运放时,为了尽可能降低输入差 因此,电荷泵两条支路上充放电电流的不匹配量分 分对管的random offset,可以通过降低输入差分对 别为 管的过驱电压(V。-V山)以及增大管子的几何尺寸 Ipl-Idhl=Inl-Ianl≈0, 来实现 Iup2-Ih2=I2-Idh2≈0 (12) 则差分电流的不匹配量为 4 仿真和测试结果 △=(Ipl-Idn)-(Iupe-Iin2)=(Ipl-Idhl)- (1pe-Idh2)=(Inl-Id1)-(I2-Ih2)(13) 4.1 传统电荷泵和本文提出的电荷泵的各条支路电 充放电电流匹配性仿真 流变化量如表1所示.所提出的电荷泵结构将 分别对传统全差分电荷泵电路和本文提出的全 pMOS管电流源与nMOS管电流源匹配问题转化 差分电荷泵电路的差分压控电压(Vp-Vm)从 为nMOS管电流源之间的匹配.提出的全差分电荷 -1.8V到1.8V进行直流扫描,得到电荷泵差分充 泵电路可以有效地克服沟道长度调制效应对充放电 放电电流的仿真波型,如图6和图7所示.当V,和 电流匹配性能的影响,使得压控电压纹波很小,能够 V差值较大时,传统全差分电荷泵的差分充放电电 极大地抑制频率综合器的杂散能量. 流不匹配量几乎是单端充放电电流不匹配量的2 3.2共模负反馈电路 倍,差分充放电电流的匹配性能被恶化了.而新型全 差分电荷泵电路在0.2~1.6V的输出电压范围内, 为保证全差分电荷泵的输出摆幅不受共模负反 其差分充放电电流的不匹配性均可小于0.1%,能 馈电路(CMFB)的限制,本文设计了如图5所示的 够很好地克服沟道长度调制效应的影响. 输入电压范围接近轨到轨的共模负反馈电路.因为 电压V。=Vp且Vn=Vm,所以可将电压V。和Vn 4.2参考杂散的测试 作为共模负反馈电路的输入采样信号,从而避免 整个频率综合器的芯片照片如图8所示.其中 CMFB对环路滤波器零极点分布的影响.缓冲放大 全差分电荷泵的面积约为450μm×280μm,电源电 器A3和A4分别将电压V。和V.复制到电压V1 压为1.8V,其中全差分电荷泵的主电路功耗为 和Vm,经RC采样电路得到V和V的共模电压 225uW,运放A1和A2的功耗分别为80uW左右, Vm,Vm与参考电压Ve相比较所得的电压Vn再 反馈到电荷泵电路.由于运放A3和A4是轨到轨结 构,所以电荷泵的输出摆幅不会受到共模负反馈电 lopi-an 路的限制.另外,对于差分电荷泵来说共模负反馈电 lup2-ane -(upI-/d1)-(up2-1im2) -0.5 0. 0.5 1.0 ('p-'V 图5宽输人范围的共模负反馈电路 图6传统电荷泵的差分电流匹配性 Fig.5 Common-mode feedback circuit with wide in- Fig.6 Matching characteristic in conventional charge put range pump

半 导 体 学 报 第28卷 表1 传统电荷泵和本文提出电荷泵的对比 犜犪犫犾犲1 犆狅犿狆犪狉犻狊狅狀狅犳犮狅狀狏犲狀狋犻狅狀犪犾犪狀犱狆狉狅狆狅狊犲犱犮犺犪狉犵犲狆狌犿狆 犞犮狆>犞犮狀 犐狌狆1 犐狌狆2 犐犱狀1 犐犱狀2 犐狌狆1-犐犱狀1 犐狌狆2-犐犱狀2 Δ=(犐狌狆1-犐犱狀1)-(犐狌狆2-犐犱狀2) 电流变 化量 传统结构 -Δ犐 Δ犐 Δ犐 -Δ犐 -2Δ犐 2Δ犐 -4Δ犐 本文提出结构 Δ犐 -Δ犐 Δ犐 -Δ犐 ~0 ~0 ~0 当共模负反馈电路稳定后,犞犳犫≈犞犫狀,又因为 犞狆= 犞犮狆,犞狀=犞犮狀,因此 犐狀1 ≈犐犱狀1,犐狀2 ≈犐犱狀2,Δ犐狉犲狆犾犻犮犪 ≈ Δ犐 (11) 因此,电荷泵两条支路上充放电电流的不匹配量分 别为 犐狌狆1 -犐犱狀1 =犐狀1 -犐犱狀1 ≈0, 犐狌狆2 -犐犱狀2 =犐狀2 -犐犱狀2 ≈0 (12) 则差分电流的不匹配量为 Δ = (犐狌狆1 -犐犱狀1)- (犐狌狆2 -犐犱狀2)= (犐狆1 -犐犱狀1)- (犐狆2 -犐犱狀2)= (犐狀1 -犐犱狀1)- (犐狀2 -犐犱狀2) (13) 传统电荷泵和本文提出的电荷泵的各条支路电 流变 化 量 如 表 1 所 示.所 提 出 的 电 荷 泵 结 构 将 狆犕犗犛管电流源与 狀犕犗犛管电流源匹配问题转化 为狀犕犗犛管电流源之间的匹配.提出的全差分电荷 泵电路可以有效地克服沟道长度调制效应对充放电 电流匹配性能的影响,使得压控电压纹波很小,能够 极大地抑制频率综合器的杂散能量. 3.2 共模负反馈电路 为保证全差分电荷泵的输出摆幅不受共模负反 馈电路(犆犕犉犅)的限制,本文设计了如图5所示的 输入电压范围接近轨到轨的共模负反馈电路.因为 电压 犞狆=犞犮狆且 犞狀=犞犮狀,所以可将电压 犞狆 和 犞狀 作为共模 负 反 馈 电 路 的 输 入 采 样 信 号,从 而 避 免 犆犕犉犅对环路滤波器零极点分布的影响.缓冲放大 器 犃3和 犃4分别将电压 犞狆 和 犞狀 复制到电压 犞狆1 和 犞狀1,经 犚犆采样电路得到 犞狆1和 犞狀1的共模电压 犞犮犿,犞犮犿 与参考电压 犞狉犲犳相比较所得的电压 犞犳犫再 反馈到电荷泵电路.由于运放 犃3和 犃4是轨到轨结 构,所以电荷泵的输出摆幅不会受到共模负反馈电 路的限制.另外,对于差分电荷泵来说共模负反馈电 图5 宽输入范围的共模负反馈电路 犉犻犵.5 犆狅犿犿狅狀犿狅犱犲犳犲犲犱犫犪犮犽犮犻狉犮狌犻狋狑犻狋犺狑犻犱犲犻狀 狆狌狋狉犪狀犵犲 路中的噪声是共模噪声,不会影响频率综合器的环 路相位噪声性能. 在设计轨到轨运放时,为了尽可能降低输入差 分对管的狉犪狀犱狅犿狅犳犳狊犲狋,可以通过降低输入差分对 管的过驱电压(犞犵狊-犞狋犺)以及增大管子的几何尺寸 来实现. 4 仿真和测试结果 4.1 充放电电流匹配性仿真 分别对传统全差分电荷泵电路和本文提出的全 差分 电 荷 泵 电 路 的 差 分 压 控 电 压 (犞犮狆 -犞犮狀)从 -18犞到18犞 进行直流扫描,得到电荷泵差分充 放电电流的仿真波型,如图6和图7所示.当 犞犮狆和 犞犮狀差值较大时,传统全差分电荷泵的差分充放电电 流不匹配量几乎是单端充放电电流不匹配量的 2 倍,差分充放电电流的匹配性能被恶化了.而新型全 差分电荷泵电路在02~16犞 的输出电压范围内, 其差分充放电电流的不匹配性均可小于01‰,能 够很好地克服沟道长度调制效应的影响. 4.2 参考杂散的测试 整个频率综合器的芯片照片如图8所示.其中 全差分电荷泵的面积约为450μ犿×280μ犿,电源电 压为 18犞,其 中 全 差 分 电 荷 泵 的 主 电 路 功 耗 为 225μ犠,运放 犃1和 犃2的功耗分别为80μ犠 左右, 图6 传统电荷泵的差分电流匹配性 犉犻犵.6 犕犪狋犮犺犻狀犵犮犺犪狉犪犮狋犲狉犻狊狋犻犮犻狀犮狅狀狏犲狀狋犻狅狀犪犾犮犺犪狉犵犲 狆狌犿狆 1996

第12期 杨振宇等: 一种应用于频率综合器的高性能全差分电荷泵电路 1997 1.0m Agem1538:21H时120e7 H112,5MT pl-lant Atten 10 dB -73.00dB 0.5 p2-an2 e-(Lp-lhi)(Lpe-li) R LgAv -0.5 -1.0 (F): Marker△ .5-1.0 -0.500.51.01.5 FTun 2.500000 ('p-')V -73.00dB「 270 VBW 278 kHz meep 1.092 ns (8192 pts) 图7本文提出的电荷泵差分电流匹配性 File Operation Status.A:\SCREN267.6IF file saved Fig.7 Matching characteristic in proposed charge pump 图10频率综合器参考杂散测试 Fig.10 Measured reference-spur level in frequency synthesizer 表2参考杂散测试结果的比较 Table 2 Comparison of measured reference spurs 工艺尺寸参考频率带宽参考杂散滤波器电源电 Loop filter 作者 /um /MHz /kHz /dBe 阶数/阶压/V Hungt7] 0.25 43 80 <-69 3 1.5 Pelleranots] 0.25 10 25 -70 2.5 图8频率综合器芯片显微照片 Herzel[9] 0.25 4 90 -45 2 2.5 Fig.8 Microphotograph of the frequency synthesizer Kuo[10] 0.18 20 60 -74 2 1.8 chip 本文 0.18 12.5 60 -73 2 1.8 运放A3和A4的功耗分别为300μW左右.主要的 谱如图10所示.可见当压控电压值V中=1.3V,Vm 测试仪器有Agilent E4445A(3~26.5GHz)频率范 =0.3V时,参考频率处的杂散能量约为-73dBc. 围的频谱分析仪以及LeCroy2GHz采样频率的示 此时的杂散能量主要是由轨到轨运放A1和A2的 波器,频率综合器的输出信号通过本征阻抗为502 失调电压(大约3mV)造成的. 的Bias-Tee单元输入到频谱分析仪中. 表2总结了本电路的杂散测试结果和其他文献 为了测试最差的参考杂散值,测试中通过改变 中的CMOS频率综合器的杂散测试结果.对比可见 分频器的分频比N,使得环路锁定时对应的压控电 采用本文提出电荷泵的频率综合器电路有比较好的 压V和V的差值最大.当环路锁定时,测试得到 参考杂散性能. 的压控电压波型如图9所示,所对应的输出信号频 结论 本文提出了一种应用于频率综合器的高性能全 V-0.8V 差分电荷泵电路.该电荷泵结构采用电流复制技术 来克服沟道长度调制效应的影响,使充放电电流在 34+ 整个输出电压范围内实现精确匹配,从而减小频率 综合器中的压控电压纹波.同时,为了保证电荷泵的 因 宽输出摆幅不受限制,本文还设计了一种输入范围 2044村烟 接近轨到轨的共模负反馈电路.理论分析和测试结 图9锁定时压控电压的波型图 果表明,所提出的全差分电荷泵电路可以很好地克 Fig.9 Waveforms of the control voltages when PLL 服传统电荷泵的缺点,完全适用于低杂散要求的高 is locked 性能频率综合器系统中

第12期 杨振宇等: 一种应用于频率综合器的高性能全差分电荷泵电路 图7 本文提出的电荷泵差分电流匹配性 犉犻犵.7 犕犪狋犮犺犻狀犵犮犺犪狉犪犮狋犲狉犻狊狋犻犮犻狀 狆狉狅狆狅狊犲犱犮犺犪狉犵犲 狆狌犿狆 图8 频率综合器芯片显微照片 犉犻犵.8 犕犻犮狉狅狆犺狅狋狅犵狉犪狆犺狅犳狋犺犲犳狉犲狇狌犲狀犮狔狊狔狀狋犺犲狊犻狕犲狉 犮犺犻狆 运放 犃3和 犃4的功耗分别为300μ犠 左右.主要的 测试仪器有 犃犵犻犾犲狀狋犈4445犃(3~265犌犎狕)频率范 围的频谱分析仪以及 犔犲犆狉狅狔2犌犎狕采样频率的示 波器,频率综合器的输出信号通过本征阻抗为50Ω 的 犅犻犪狊犜犲犲单元输入到频谱分析仪中. 为了测试最差的参考杂散值,测试中通过改变 分频器的分频比 犖,使得环路锁定时对应的压控电 压 犞犮狆和 犞犮狀的差值最大.当环路锁定时,测试得到 的压控电压波型如图9所示,所对应的输出信号频 图9 锁定时压控电压的波型图 犉犻犵.9 犠犪狏犲犳狅狉犿狊狅犳狋犺犲犮狅狀狋狉狅犾狏狅犾狋犪犵犲狊狑犺犲狀犘犔犔 犻狊犾狅犮犽犲犱 图10 频率综合器参考杂散测试 犉犻犵.10 犕犲犪狊狌狉犲犱狉犲犳犲狉犲狀犮犲狊狆狌狉犾犲狏犲犾犻狀犳狉犲狇狌犲狀犮狔 狊狔狀狋犺犲狊犻狕犲狉 表2 参考杂散测试结果的比较 犜犪犫犾犲2 犆狅犿狆犪狉犻狊狅狀狅犳犿犲犪狊狌狉犲犱狉犲犳犲狉犲狀犮犲狊狆狌狉狊 作者 工艺尺寸 /μ犿 参考频率 /犕犎狕 带宽 /犽犎狕 参考杂散 /犱犅犮 滤波器 阶数/阶 电源电 压/犞 犎狌狀犵[7] 0.25 43 80 <-69 3 1.5 犘犲犾犾犲狉犪狀狅[8] 0.25 10 25 -70 3 2.5 犎犲狉狕犲犾[9] 0.25 4 90 -45 2 2.5 犓狌狅[10] 0.18 20 60 -74 2 1.8 本文 0.18 125 60 -73 2 1.8 谱如图10所示.可见当压控电压值 犞犮狆=13犞,犞犮狀 =03犞 时,参考频率处的杂散能量约为-73犱犅犮. 此时的杂散能量主要是由轨到轨运放 犃1和 犃2的 失调电压(大约3犿犞)造成的. 表2总结了本电路的杂散测试结果和其他文献 中的 犆犕犗犛频率综合器的杂散测试结果.对比可见 采用本文提出电荷泵的频率综合器电路有比较好的 参考杂散性能. 5 结论 本文提出了一种应用于频率综合器的高性能全 差分电荷泵电路.该电荷泵结构采用电流复制技术 来克服沟道长度调制效应的影响,使充放电电流在 整个输出电压范围内实现精确匹配,从而减小频率 综合器中的压控电压纹波.同时,为了保证电荷泵的 宽输出摆幅不受限制,本文还设计了一种输入范围 接近轨到轨的共模负反馈电路.理论分析和测试结 果表明,所提出的全差分电荷泵电路可以很好地克 服传统电荷泵的缺点,完全适用于低杂散要求的高 性能频率综合器系统中. 1997

1998 半导体学报 第28卷 Solid-State Circuits.1999.34(2):148 参考文献 [6]Temporiti E.Albasini G.Bictti I.ct al.A 700-kHz bandwidth AS fractional synthesizer with spurs compensation and lin- [1 Vaucher C S.Architectures for RF frequency synthesizers. earization techniques for WCDMA applications.IEEE J Sol- Kluwer Academic Publishers.2002 id-State Circuits,2004,39(9):1446 [2]Rhee W.Design of high-performance CMOS charge pumps [7]Hung C M,Kenneth K O.A fully integrated 1.5-V 5.5-GHz in phase-locked loops.IEEE Proccedings of the International CMOS phase-locked loop.IEEE J Solid-State Circuits,2002. Symposium on Circuits and Systems,1999,2:545 37(4):521 [3]Shu Zhinian.Lee K L,Lcung B H,ct al.A 2.4GHz ring-os- [8 Pellerano S,Laventino S.Samori C,ct al.A 13.5-mW 5-GHz cillator-based CMOS frequency synthesizer with a fractional frequency synthesizer with dynamic-logic frequency divider. divider dual-PLL architecture.IEEE J Solid-State Circuits. IEEE J Solid-State Circuits.2004,39:378 2004,39(3):452 [9 Herzel F.Fischer G.Gustat H.An integrated CMOS RF syn- [4] Maxim A.Low-voltage CMOS charge-pump PLL architec. thesizer for 802.11a wireless LAN.IEEE J Solid-State Cir- ture for low jitter operation.Proceedings of the 28th Europe- cuits,2003,38(10):1767 an Solid-State Circuit.2002:423 [10]Kuo C Y.Chang J Y.Liu S I.A spur-reduction techniquc for [5]Wang Minsheng.Terry L.Constant-gm rail-to-rail CMOS op- a 5-GHz frequency synthesizer.IEEE Trans Circuits and Sys- amp input stage with overlapped transition regions.IEEE J tems-I:Regular Papers.2006.53:526 A High-Performance Fully Differential Charge Pump for Frequency Synthesizer Applications Yang Zhenyu,Tang Zhangwen',and Min Hao (State Key Laboratory of ASIC&System.Fudan University.Shanghai 201203.China) Abstract:A fully differential charge pump for a frequency synthesizer is proposed.The pump eliminates the effect of chan- nel-length modulation and makes the charging and discharging currents match perfectly in a wide output range to minimize the ripple of the control voltage.A common-mode feedback circuit with rail-to-rail input range is employed to ensure a large unrestricted swing of the charge pump.The proposed fully differential charge pump is designed and fabricated in a 1.8V SMIC 0.18um CMOS mixed-signal process:the chip area is about 450um x 280um:and the power dissipation is 1mW.A refer- ence spur level of-73dBc is achieved in the worst case,satisfying the performance of the frequency synthesizer. Key words:frequency synthesizer;fully differential charge pump:current matching:replica:ripple;spur EEACC:1205:1280:2570D Article ID:0253-4177(2007)12-1993-06 f Corresponding author.Email:zwtang@fudan.edu.cn Received 4 June 2007.revised manuseript received 8 July 2007 2007 Chinese Institute of Electronics

半 导 体 学 报 第28卷 参考文献 [1] 犞犪狌犮犺犲狉犆犛.犃狉犮犺犻狋犲犮狋狌狉犲狊犳狅狉犚犉犳狉犲狇狌犲狀犮狔狊狔狀狋犺犲狊犻狕犲狉狊. 犓犾狌狑犲狉犃犮犪犱犲犿犻犮犘狌犫犾犻狊犺犲狉狊,2002 [2] 犚犺犲犲犠.犇犲狊犻犵狀狅犳犺犻犵犺狆犲狉犳狅狉犿犪狀犮犲犆犕犗犛犮犺犪狉犵犲狆狌犿狆狊 犻狀狆犺犪狊犲犾狅犮犽犲犱犾狅狅狆狊.犐犈犈犈犘狉狅犮犲犲犱犻狀犵狊狅犳狋犺犲犐狀狋犲狉狀犪狋犻狅狀犪犾 犛狔犿狆狅狊犻狌犿狅狀犆犻狉犮狌犻狋狊犪狀犱犛狔狊狋犲犿狊,1999,2:545 [3] 犛犺狌犣犺犻狀犻犪狀,犔犲犲犓犔,犔犲狌狀犵犅 犎,犲狋犪犾.犃24犌犎狕狉犻狀犵狅狊 犮犻犾犾犪狋狅狉犫犪狊犲犱犆犕犗犛犳狉犲狇狌犲狀犮狔狊狔狀狋犺犲狊犻狕犲狉狑犻狋犺犪犳狉犪犮狋犻狅狀犪犾 犱犻狏犻犱犲狉犱狌犪犾犘犔犔犪狉犮犺犻狋犲犮狋狌狉犲.犐犈犈犈犑犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊, 2004,39(3):452 [4] 犕犪狓犻犿 犃.犔狅狑狏狅犾狋犪犵犲犆犕犗犛犮犺犪狉犵犲狆狌犿狆犘犔犔犪狉犮犺犻狋犲犮 狋狌狉犲犳狅狉犾狅狑犼犻狋狋犲狉狅狆犲狉犪狋犻狅狀.犘狉狅犮犲犲犱犻狀犵狊狅犳狋犺犲28狋犺犈狌狉狅狆犲 犪狀犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋,2002:423 [5] 犠犪狀犵犕犻狀狊犺犲狀犵,犜犲狉狉狔犔.犆狅狀狊狋犪狀狋犵犿狉犪犻犾狋狅狉犪犻犾犆犕犗犛狅狆 犪犿狆犻狀狆狌狋狊狋犪犵犲狑犻狋犺狅狏犲狉犾犪狆狆犲犱狋狉犪狀狊犻狋犻狅狀狉犲犵犻狅狀狊.犐犈犈犈犑 犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊,1999,34(2):148 [6] 犜犲犿狆狅狉犻狋犻犈,犃犾犫犪狊犻狀犻犌,犅犻犲狋狋犻犐,犲狋犪犾.犃700犽犎狕犫犪狀犱狑犻犱狋犺 ΔΣ犳狉犪犮狋犻狅狀犪犾狊狔狀狋犺犲狊犻狕犲狉狑犻狋犺狊狆狌狉狊犮狅犿狆犲狀狊犪狋犻狅狀犪狀犱犾犻狀 犲犪狉犻狕犪狋犻狅狀狋犲犮犺狀犻狇狌犲狊犳狅狉犠犆犇犕犃犪狆狆犾犻犮犪狋犻狅狀狊.犐犈犈犈犑犛狅犾 犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊,2004,39(9):1446 [7] 犎狌狀犵犆 犕,犓犲狀狀犲狋犺犓犗.犃犳狌犾犾狔犻狀狋犲犵狉犪狋犲犱1.5犞5.5犌犎狕 犆犕犗犛狆犺犪狊犲犾狅犮犽犲犱犾狅狅狆.犐犈犈犈犑犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊,2002, 37(4):521 [8] 犘犲犾犾犲狉犪狀狅犛,犔犪狏犲狀狋犻狀狅犛,犛犪犿狅狉犻犆,犲狋犪犾.犃13.5犿犠5犌犎狕 犳狉犲狇狌犲狀犮狔狊狔狀狋犺犲狊犻狕犲狉狑犻狋犺犱狔狀犪犿犻犮犾狅犵犻犮犳狉犲狇狌犲狀犮狔犱犻狏犻犱犲狉. 犐犈犈犈犑犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊,2004,39:378 [9] 犎犲狉狕犲犾犉,犉犻狊犮犺犲狉犌,犌狌狊狋犪狋犎.犃狀犻狀狋犲犵狉犪狋犲犱犆犕犗犛犚犉狊狔狀 狋犺犲狊犻狕犲狉犳狅狉802.11犪狑犻狉犲犾犲狊狊犔犃犖.犐犈犈犈犑犛狅犾犻犱犛狋犪狋犲犆犻狉 犮狌犻狋狊,2003,38(10):1767 [10] 犓狌狅犆犢,犆犺犪狀犵犑犢,犔犻狌犛犐.犃狊狆狌狉狉犲犱狌犮狋犻狅狀狋犲犮犺狀犻狇狌犲犳狅狉 犪5犌犎狕犳狉犲狇狌犲狀犮狔狊狔狀狋犺犲狊犻狕犲狉.犐犈犈犈犜狉犪狀狊犆犻狉犮狌犻狋狊犪狀犱犛狔狊 狋犲犿狊犐:犚犲犵狌犾犪狉犘犪狆犲狉狊,2006,53:526 犃犎犻犵犺犘犲狉犳狅狉犿犪狀犮犲犉狌犾犾狔犇犻犳犳犲狉犲狀狋犻犪犾犆犺犪狉犵犲犘狌犿狆犳狅狉犉狉犲狇狌犲狀犮狔 犛狔狀狋犺犲狊犻狕犲狉犃狆狆犾犻犮犪狋犻狅狀狊 犢犪狀犵犣犺犲狀狔狌,犜犪狀犵犣犺犪狀犵狑犲狀,犪狀犱犕犻狀犎犪狅 (犛狋犪狋犲犓犲狔犔犪犫狅狉犪狋狅狉狔狅犳犃犛犐犆牔犛狔狊狋犲犿,犉狌犱犪狀犝狀犻狏犲狉狊犻狋狔,犛犺犪狀犵犺犪犻 201203,犆犺犻狀犪) 犃犫狊狋狉犪犮狋:犃犳狌犾犾狔犱犻犳犳犲狉犲狀狋犻犪犾犮犺犪狉犵犲狆狌犿狆犳狅狉犪犳狉犲狇狌犲狀犮狔狊狔狀狋犺犲狊犻狕犲狉犻狊狆狉狅狆狅狊犲犱.犜犺犲狆狌犿狆犲犾犻犿犻狀犪狋犲狊狋犺犲犲犳犳犲犮狋狅犳犮犺犪狀 狀犲犾犾犲狀犵狋犺犿狅犱狌犾犪狋犻狅狀犪狀犱犿犪犽犲狊狋犺犲犮犺犪狉犵犻狀犵犪狀犱犱犻狊犮犺犪狉犵犻狀犵犮狌狉狉犲狀狋狊犿犪狋犮犺狆犲狉犳犲犮狋犾狔犻狀犪狑犻犱犲狅狌狋狆狌狋狉犪狀犵犲狋狅犿犻狀犻犿犻狕犲 狋犺犲狉犻狆狆犾犲狅犳狋犺犲犮狅狀狋狉狅犾狏狅犾狋犪犵犲.犃犮狅犿犿狅狀犿狅犱犲犳犲犲犱犫犪犮犽犮犻狉犮狌犻狋狑犻狋犺狉犪犻犾狋狅狉犪犻犾犻狀狆狌狋狉犪狀犵犲犻狊犲犿狆犾狅狔犲犱狋狅犲狀狊狌狉犲犪犾犪狉犵犲 狌狀狉犲狊狋狉犻犮狋犲犱狊狑犻狀犵狅犳狋犺犲犮犺犪狉犵犲狆狌犿狆.犜犺犲狆狉狅狆狅狊犲犱犳狌犾犾狔犱犻犳犳犲狉犲狀狋犻犪犾犮犺犪狉犵犲狆狌犿狆犻狊犱犲狊犻犵狀犲犱犪狀犱犳犪犫狉犻犮犪狋犲犱犻狀犪18犞 犛犕犐犆018μ犿犆犕犗犛犿犻狓犲犱狊犻犵狀犪犾狆狉狅犮犲狊狊;狋犺犲犮犺犻狆犪狉犲犪犻狊犪犫狅狌狋450μ犿×280μ犿;犪狀犱狋犺犲狆狅狑犲狉犱犻狊狊犻狆犪狋犻狅狀犻狊1犿犠.犃狉犲犳犲狉 犲狀犮犲狊狆狌狉犾犲狏犲犾狅犳-73犱犅犮犻狊犪犮犺犻犲狏犲犱犻狀狋犺犲狑狅狉狊狋犮犪狊犲,狊犪狋犻狊犳狔犻狀犵狋犺犲狆犲狉犳狅狉犿犪狀犮犲狅犳狋犺犲犳狉犲狇狌犲狀犮狔狊狔狀狋犺犲狊犻狕犲狉. 犓犲狔狑狅狉犱狊:犳狉犲狇狌犲狀犮狔狊狔狀狋犺犲狊犻狕犲狉;犳狌犾犾狔犱犻犳犳犲狉犲狀狋犻犪犾犮犺犪狉犵犲狆狌犿狆;犮狌狉狉犲狀狋犿犪狋犮犺犻狀犵;狉犲狆犾犻犮犪;狉犻狆狆犾犲;狊狆狌狉 犈犈犃犆犆:1205;1280;2570犇 犃狉狋犻犮犾犲犐犇:02534177(2007)12199306 犆狅狉狉犲狊狆狅狀犱犻狀犵犪狌狋犺狅狉.犈犿犪犻犾:狕狑狋犪狀犵@犳狌犱犪狀.犲犱狌.犮狀 犚犲犮犲犻狏犲犱4犑狌狀犲2007,狉犲狏犻狊犲犱犿犪狀狌狊犮狉犻狆狋狉犲犮犲犻狏犲犱8犑狌犾狔2007 2007犆犺犻狀犲狊犲犐狀狊狋犻狋狌狋犲狅犳犈犾犲犮狋狉狅狀犻犮狊 1998