9B-3s An Accurate 1.08-GHz CMOS LC Voltage-Controlled Oscillator Zhangwen Tang,Jie He,Hongyan Jian,and Hao Min ASIC System State Key Laboratory,Fudan University,Shanghai 200433,P.R.China Tel:+86-21-65642765*819Fax:+86-21-65644158 E-mail:(zwtang,jiehe,hyjian,hmin)@fudan.edu.cn Abstract -An accurate 1.08-GHz CMOS LC voltage -controlled oscillator is implemented in a 0.35um standard 2P4M CMOS process.In this paper we present a new convenient method of calculation of oscillating period.With Mp2 this period calculation technique,the frequency tuning curves agree perfectly with the experiment.At a 3.3-V supply,the LC-VCO measures a phase noise of-82.2 dBc/Hz at a 10kHz 0Q00·一0Q00 frequency offset while dissipating 3.1mA current.Chip size is 0.86mm×0.82mm. I.INTRODUCTION Mn Mn2 The explosive growth in wireless communications has driven universities and companies to produce wireless transceivers at low-cost,low-power,and compact size. Recently,all of RF components,such as low-noise amplifiers (LNAs),mixer,local oscillators (LOs),and IF Filters.seem possible to be integrated in CMOS scaled technology. On-chip passive elements such as spiral inductors and varactors make on-chip implementation of LC-tank Fig.1. CMOS complementary cross-coupled LC-tank VCO voltage-controlled oscillators (VCOs)easy. A complementary cross-coupled negative-Gm LC-tank 5.780 1238 oscillator is shown in Fig.1,which employs both NMOS R Ls and PMOS cross-coupled pairs.Many published papers Portl O- WWQ0一WW Port2 [1]-[3],have employed this type of LC-tank VCO,but 479.5压 476.9 oscillator's tuning curves were obtained from SPICE simulations or measurements.The prediction of oscillator's tuning curves is quite challenging due to highly nonlinear 37.120 37.280 characteristics of varactors.A numerical method is shown in [3],but it is quite complex and time-consuming.The tuning curves must be numerically computed again if bias current changes. In this paper,we investigate the I-V locus of step-like MOS Fig.2.PI model of on-chip spiral inductor varactors in a LC-VCO and predict the tuning curves through the oscillating period calculation of a serial LC tank in time patterned ground shield (PGS)is employed to improve domain [4],[9].An accurate 1.08-GHz CMOS LC quality of inductors at low frequency (1-2GHz)[5].On-chip voltage-controlled oscillator is implemented in a 0.35um differential spiral inductor is 12.4nH,so the single-end standard 2P4M CMOS process.The theoretical analyses inductor features 6.2nH.The maximum Q arrives seven at agree perfectly with the simulation and measurement of a 1.1GHz.The compact equivalent pi model shown in Fig.2 is CMOS complementary LC-tank VCO. extracted with ASITIC [6]. The transconductances of cross-couple NMOS and PMOS II.CIRCUIT DESIGN devices are chosen to be equal so that DC voltage of LC-tank oscillator is maintained at approximately V2.First,the The complementary cross-coupled negative-Gm LC-tank oscillating waveform can have the maximum swing. voltage-controlled oscillator in Fig.I has been implemented Secondly,the VCO gain (Ky)can decrease and the in 0.35um 2P4M 3.3V CMOS process.On-chip spiral phase-noise performance can be improved.The MOS devices inductor is a symmetric differential multilayer inductor.Four are implemented using the minimum gate length (0.35um). metals are parallelly and serially connected with a lot of vias The open-drain NMOS devices are the output buffers,which to decrease the serial resistor of spiral inductor and increase is used to drive the off-chip Bias-T circuits.In order to the inductance in unit silicon area.And a center-connected decrease the Miller-effect capacitor,the length of open-drain NMOS devices is 60um.The lengths of current-mirror are larger than the minimum length so that the channel length This work was supported in part by the Shanghai Science modulation(CLM)is attenuated and 1/f noise is decreased. Technology Committee,P.R.China under System-Design-Chip (SDC)program (NO.037062019). 0-7803-8736-8/05/$20.00©2005IEEE. 889 ASP-DAC 2005

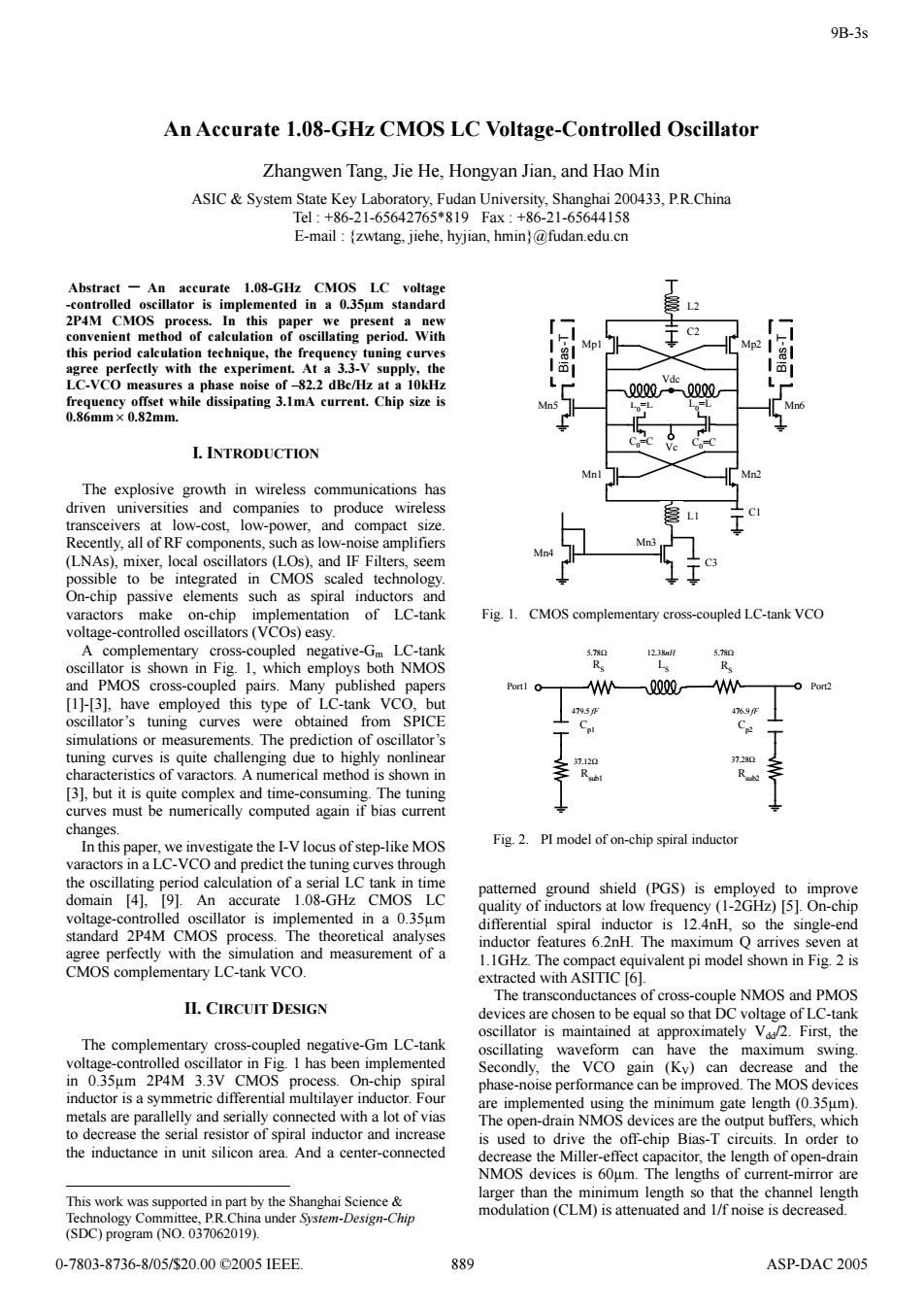

Abstract - An accurate 1.08-GHz CMOS LC voltage -controlled oscillator is implemented in a 0.35µm standard 2P4M CMOS process. In this paper we present a new convenient method of calculation of oscillating period. With this period calculation technique, the frequency tuning curves agree perfectly with the experiment. At a 3.3-V supply, the LC-VCO measures a phase noise of –82.2 dBc/Hz at a 10kHz frequency offset while dissipating 3.1mA current. Chip size is 0.86mm× 0.82mm. I. INTRODUCTION The explosive growth in wireless communications has driven universities and companies to produce wireless transceivers at low-cost, low-power, and compact size. Recently, all of RF components, such as low-noise amplifiers (LNAs), mixer, local oscillators (LOs), and IF Filters, seem possible to be integrated in CMOS scaled technology. On-chip passive elements such as spiral inductors and varactors make on-chip implementation of LC-tank voltage-controlled oscillators (VCOs) easy. A complementary cross-coupled negative-Gm LC-tank oscillator is shown in Fig. 1, which employs both NMOS and PMOS cross-coupled pairs. Many published papers [1]-[3], have employed this type of LC-tank VCO, but oscillator’s tuning curves were obtained from SPICE simulations or measurements. The prediction of oscillator’s tuning curves is quite challenging due to highly nonlinear characteristics of varactors. A numerical method is shown in [3], but it is quite complex and time-consuming. The tuning curves must be numerically computed again if bias current changes. In this paper, we investigate the I-V locus of step-like MOS varactors in a LC-VCO and predict the tuning curves through the oscillating period calculation of a serial LC tank in time domain [4], [9]. An accurate 1.08-GHz CMOS LC voltage-controlled oscillator is implemented in a 0.35µm standard 2P4M CMOS process. The theoretical analyses agree perfectly with the simulation and measurement of a CMOS complementary LC-tank VCO. II. CIRCUIT DESIGN The complementary cross-coupled negative-Gm LC-tank voltage-controlled oscillator in Fig. 1 has been implemented in 0.35µm 2P4M 3.3V CMOS process. On-chip spiral inductor is a symmetric differential multilayer inductor. Four metals are parallelly and serially connected with a lot of vias to decrease the serial resistor of spiral inductor and increase the inductance in unit silicon area. And a center-connected This work was supported in part by the Shanghai Science & Technology Committee, P.R.China under System-Design-Chip (SDC) program (NO. 037062019). patterned ground shield (PGS) is employed to improve quality of inductors at low frequency (1-2GHz) [5]. On-chip differential spiral inductor is 12.4nH, so the single-end inductor features 6.2nH. The maximum Q arrives seven at 1.1GHz. The compact equivalent pi model shown in Fig. 2 is extracted with ASITIC [6]. The transconductances of cross-couple NMOS and PMOS devices are chosen to be equal so that DC voltage of LC-tank oscillator is maintained at approximately Vdd/2. First, the oscillating waveform can have the maximum swing. Secondly, the VCO gain (KV) can decrease and the phase-noise performance can be improved. The MOS devices are implemented using the minimum gate length (0.35µm). The open-drain NMOS devices are the output buffers, which is used to drive the off-chip Bias-T circuits. In order to decrease the Miller-effect capacitor, the length of open-drain NMOS devices is 60µm. The lengths of current-mirror are larger than the minimum length so that the channel length modulation (CLM) is attenuated and 1/f noise is decreased. An Accurate 1.08-GHz CMOS LC Voltage-Controlled Oscillator Zhangwen Tang, Jie He, Hongyan Jian, and Hao Min ASIC & System State Key Laboratory, Fudan University, Shanghai 200433, P.R.China Tel : +86-21-65642765*819 Fax : +86-21-65644158 E-mail : {zwtang, jiehe, hyjian, hmin}@fudan.edu.cn L0 =L C0=C Vc Mn1 Mn2 Mp1 Mp2 Mn5 Mn6 Mn3 Mn4 Bias-T Bias-T L1 L2 C3 C2 C1 C0=C L0=L Vdc Fig. 1. CMOS complementary cross-coupled LC-tank VCO RS LS Cp1 Cp2 Rsub1 Rsub2 RS 5.78Ω 12.38nH 5.78Ω 479.5 fF 476.9 fF 37.12Ω 37.28Ω Port1 Port2 Fig. 2. PI model of on-chip spiral inductor 889 9B-3s 0-7803-8736-8/05/$20.00 ©2005 IEEE. ASP-DAC 2005

Vdd 复 C.(V) 2 Vctrl C.M sign(V) (a)Serial LC Tank (b)Step-like Varactor (c)Unit Step Function 2.4 Fig.3.Serial LC-tank and step-like varactor 23 20 Two additional inductors,LI L2,resonate at double frequency with the parasitic capacitors Cl C2 at each common-source node,to avoid Q-degradation by triode region MOS transistors in the stacked differential pairs [7]. The filtering capacitor C3 is used to low the 1/f noise and 0.5 10 effect of channel length modulation(CLM)[1]. Time(ns) III.FREQUENCY TUNING CHARACTERISTIC Fig.4.Voltage waveforms of a varactor at different ECV Most of varactors used in LC-tank VCO circuits are Inversion-MOS (I-MOS)and Accumulation-MOS (A-MOS) Their characteristics both are step-like,and have large nonlinearity.The tuning curves of an LC-VCO will substantially deviate from the ideal curve 1/LC when a step-like varactor is used [3].Both I-MOS and A-MOS are step-like capacitors (Fig3.(b)and (c)).The small-signal capacitance is given by, V≥' C(V)= (1) V<V .50 where V=V-Vin-Vi is effective control voltage (ECV). The presence of on-chip inductors in Fig.I imposes that 1.4 22 1428 25 the dc value of differential oscillating voltages has to be a Voltage(V) constant voltage Vae.Neglecting the tank losses in on-chip Fig.5.I-V locus of a varactor inductors and varactors,the half circuit of LC-tank VCO can be considered as a serial LC-tank structure (Fig.3(a)).The value of inductor is L,and the step-like varactors can be sinusoids joined at ECV.One is above Ver with the mathematically represented as below, amplitude 4(is another ESF)and frequency C.W)-(C+C)+(C-C)ign-V)) the other is below Ver with the amplitude Amx and Fig.4 shows the oscillating voltage waveforms of the frequency mr serial LC tank simulated in HSPICE.Each waveform The I-V locus of a step-like varactor in the serial LC-tank consists of two segmental sinusoids with different size circuit is shown in Fig.5.It is consists of two ellipses of which join at the effective control voltage (ECV).With the different size joined at the ECV.The above four regions ECV from low to high,there exist four regions as below, satisfy the following ellipses'equations: 1)When VensVde-Amin,the oscillating waveform is a sinusoid 1)When VensVde-Amin,the I-V locus holds with the minimum amplitude Amin and minimum frequency =1 @ain 、Am (3) 2)When Ven2Vde+Amax,a sinusoid with the maximum 2)When VenVde+Amax,it holds amplitude Amax and maximum frequency; 2 3)When Vde-AminsVensVdc,two partial sinusoids join at V-Vk =1 (4) ECV.One is over Verr with the amplitude Amin and A frequency the other is below Ve with the amplitude 3)When Vde-AminsVerr sVdc,two segmental sinusoids 6 A(is an ellipse similar factor.ESF)and frequency respectively hold 包s =1,forV≥'g 4)When VdesVensVde+Amax,it consists of two segmental 890

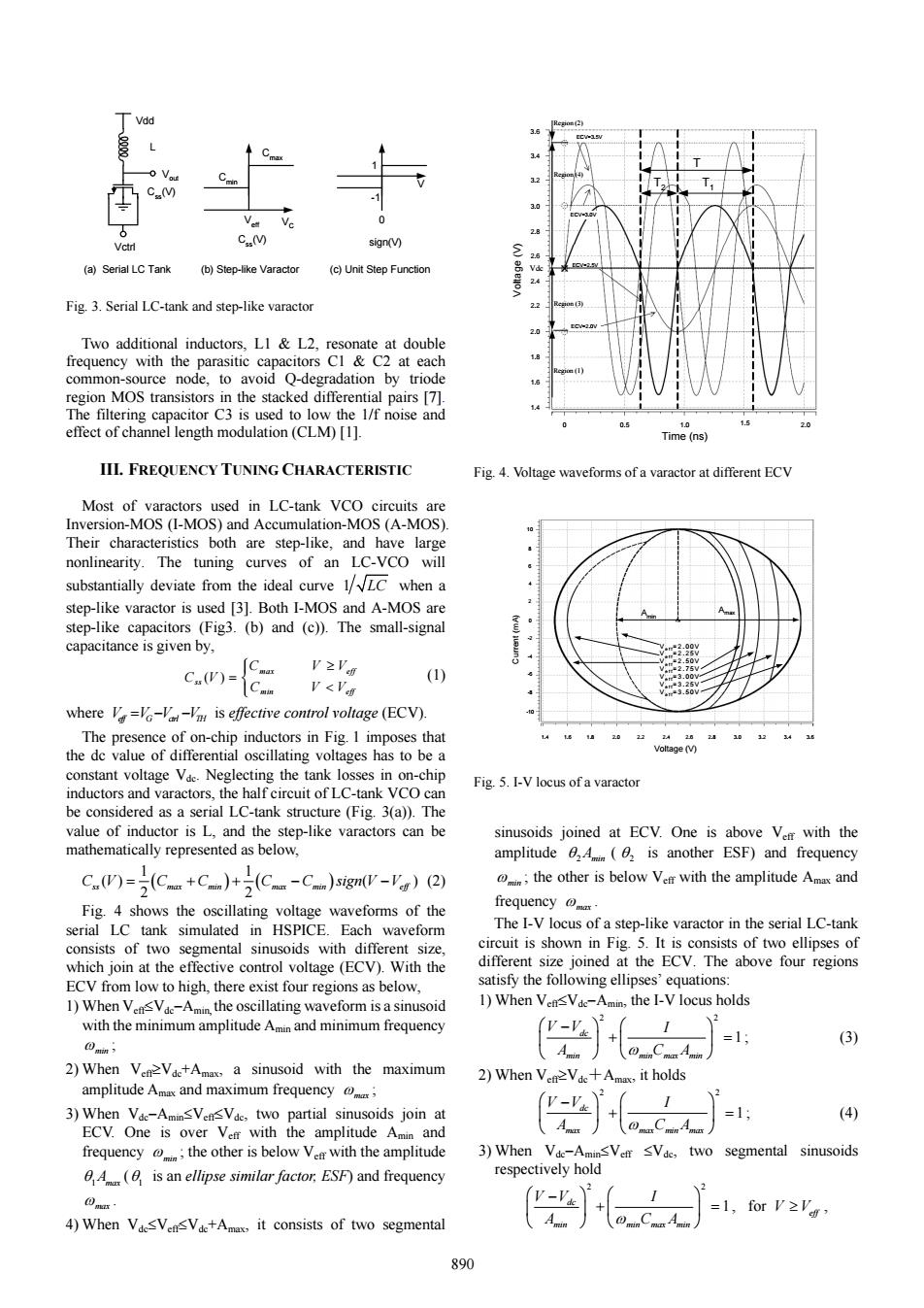

Two additional inductors, L1 & L2, resonate at double frequency with the parasitic capacitors C1 & C2 at each common-source node, to avoid Q-degradation by triode region MOS transistors in the stacked differential pairs [7]. The filtering capacitor C3 is used to low the 1/f noise and effect of channel length modulation (CLM) [1]. III. FREQUENCY TUNING CHARACTERISTIC Most of varactors used in LC-tank VCO circuits are Inversion-MOS (I-MOS) and Accumulation-MOS (A-MOS). Their characteristics both are step-like, and have large nonlinearity. The tuning curves of an LC-VCO will substantially deviate from the ideal curve 1 LC when a step-like varactor is used [3]. Both I-MOS and A-MOS are step-like capacitors (Fig3. (b) and (c)). The small-signal capacitance is given by, ( ) max eff ss min eff C VV C V C VV ⎧⎪ ≥ = ⎨ ⎪ < ⎩ (1) where V VV V eff G ctrl TH =− − is effective control voltage (ECV). The presence of on-chip inductors in Fig. 1 imposes that the dc value of differential oscillating voltages has to be a constant voltage Vdc. Neglecting the tank losses in on-chip inductors and varactors, the half circuit of LC-tank VCO can be considered as a serial LC-tank structure (Fig. 3(a)). The value of inductor is L, and the step-like varactors can be mathematically represented as below, ( ) ( ) 1 1 () ( ) 2 2 C V C C C C sign V V ss max min max min eff = ++ − − (2) Fig. 4 shows the oscillating voltage waveforms of the serial LC tank simulated in HSPICE. Each waveform consists of two segmental sinusoids with different size, which join at the effective control voltage (ECV). With the ECV from low to high, there exist four regions as below, 1) When Veff≤Vdc−Amin, the oscillating waveform is a sinusoid with the minimum amplitude Amin and minimum frequency ω min ; 2) When Veff≥Vdc+Amax, a sinusoid with the maximum amplitude Amax and maximum frequency ω max ; 3) When Vdc−Amin≤Veff≤Vdc, two partial sinusoids join at ECV. One is over Veff with the amplitude Amin and frequency ω min ; the other is below Veff with the amplitude θ1Amax (θ1 is an ellipse similar factor, ESF) and frequency ω max . 4) When Vdc≤Veff≤Vdc+Amax, it consists of two segmental sinusoids joined at ECV. One is above Veff with the amplitude θ 2Amin ( θ 2 is another ESF) and frequency ω min ; the other is below Veff with the amplitude Amax and frequency ω max . The I-V locus of a step-like varactor in the serial LC-tank circuit is shown in Fig. 5. It is consists of two ellipses of different size joined at the ECV. The above four regions satisfy the following ellipses’ equations: 1) When Veff≤Vdc−Amin, the I-V locus holds 2 2 1 ω ⎛ ⎞⎛ ⎞ − ⎜ ⎟⎜ ⎟ + = ⎝ ⎠⎝ ⎠ dc min min max min V V I A CA ; (3) 2) When Veff≥Vdc+Amax, it holds 2 2 1 ω ⎛ ⎞⎛ ⎞ − ⎜ ⎟⎜ ⎟ + = ⎝ ⎠⎝ ⎠ dc max max min max V V I A CA ; (4) 3) When Vdc−Amin≤Veff ≤Vdc, two segmental sinusoids respectively hold 2 2 1 ω ⎛ ⎞⎛ ⎞ − ⎜ ⎟⎜ ⎟ + = ⎝ ⎠⎝ ⎠ dc min min max min V V I A CA , for V V≥ eff , L Css(V) Vdd Vctrl Cmax Cmin Veff VC 1 -1 0 V Css(V) sign(V) (a) Serial LC Tank (b) Step-like Varactor (c) Unit Step Function Vout Fig. 3. Serial LC-tank and step-like varactor 3.6 3.4 3.2 3.0 2.8 2.6 2.2 2.0 1.8 2.4 1.6 1.4 Voltage (V) 0 0.5 1.0 1.5 2.0 Time (ns) T1 T2 T Vdc ECV=3.5V ECV=3.0V ECV=2.5V ECV=2.0V Region (1) Region (2) Region (3) Region (4) Fig. 4. Voltage waveforms of a varactor at different ECV Amin Amax V eff =2.00V V eff =2.25V V eff =2.50V V eff =2.75V V eff =3.00V V eff =3.25V V eff =3.50V 1.4 1.6 1.8 2.0 2.2 2.4 2.6 2.8 3.0 3.2 3.4 3.6 10 8 6 4 2 0 -4 -6 -8 -2 -10 Current (mA) Voltage (V) Fig. 5. I-V locus of a varactor 890

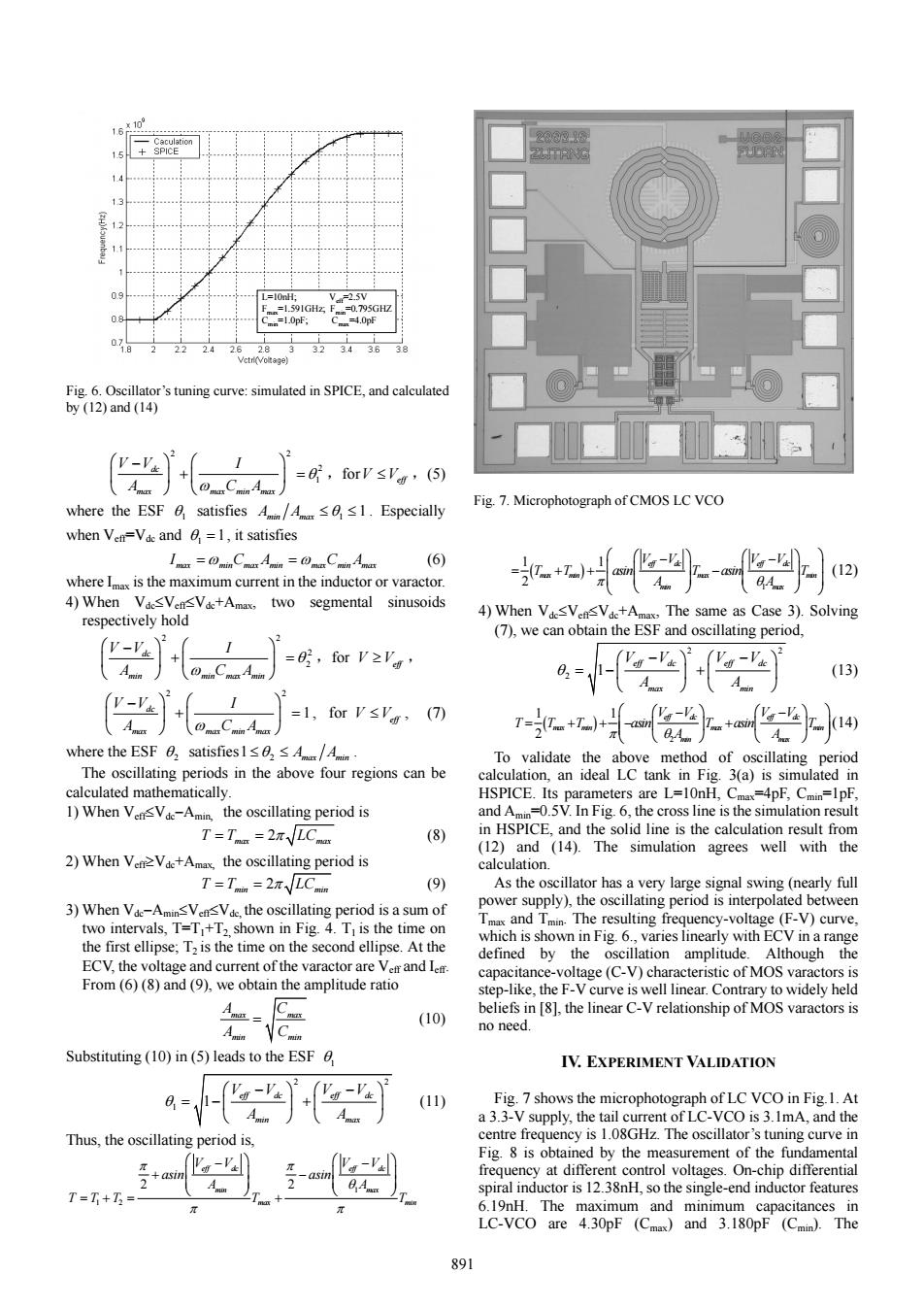

13 09 V SV =1.591GHz 0.795GHZ =10p, C=4.0pF 22 2.6 28 32343638 Vctri(Voltage) Fig.6.Oscillator's tuning curve:simulated in SPICE,and calculated by(12)and(14) =,forV≤V,(5) Fig.7.Microphotograph of CMOS LC VCO where the ESF satisfies As1.Especially when Ve=Vde and =1,it satisfies Ima=OminCmr Ain=Cn Amat (6) where I is the maximum current in the inductor or varactor. 4)When VacsVen<Vac+Amax,two segmental sinusoids respectively hold 4)When VdesVensVde+Amax,The same as Case 3).Solving (7),we can obtain the ESF and oscillating period, '-' ,forV≥'' 4阿 (13) =1,forV≤', (7) where the ESF,satisfies1≤O2≤Ans/Awin To validate the above method of oscillating period The oscillating periods in the above four regions can be calculation,an ideal LC tank in Fig.3(a)is simulated in calculated mathematically. HSPICE.Its parameters are L=10nH,Cmax=4pF,Cmin=1pF, 1)When VensVd-Amin,the oscillating period is and Amin=0.5V.In Fig.6,the cross line is the simulation result T=Tna=2πLC (8) in HSPICE.and the solid line is the calculation result from (12)and (14).The simulation agrees well with the 2)When VenVde+Amax,the oscillating period is calculation. T=Tm=2πVLCn (9) As the oscillator has a very large signal swing(nearly full 3)When Vde-AminVenVde,the oscillating period is a sum of power supply),the oscillating period is interpolated between two intervals,T=T +T,shown in Fig.4.T is the time on Tmax and Tmin The resulting frequency-voltage(F-V)curve, the first ellipse;T2 is the time on the second ellipse.At the which is shown in Fig.6.,varies linearly with ECV in a range defined by the oscillation amplitude.Although the ECV,the voltage and current of the varactor are Vet and Iem. capacitance-voltage(C-V)characteristic of MOS varactors is From(6)(8)and(9),we obtain the amplitude ratio step-like,the F-V curve is well linear.Contrary to widely held beliefs in [8],the linear C-V relationship of MOS varactors is (10) no need. Substituting(10)in(5)leads to the ESF TV.EXPERIMENT VALIDATION -V (11) Fig.7 shows the microphotograph of LC VCO in Fig.1.At a 3.3-V supply,the tail current of LC-VCO is 3.1mA,and the Thus,the oscillating period is, centre frequency is 1.08GHz.The oscillator's tuning curve in Fig.8 is obtained by the measurement of the fundamental frequency at different control voltages.On-chip differential spiral inductor is 12.38nH,so the single-end inductor features T=T+3= 6.19nH.The maximum and minimum capacitances in LC-VCO are 4.30pF (Cmax)and 3.180pF (Cmin).The 891

2 2 2 θ1 ω ⎛ ⎞⎛ ⎞ − ⎜ ⎟⎜ ⎟ + = ⎝ ⎠⎝ ⎠ dc max max min max V V I A CA ,forV V≤ eff ,(5) where the ESF θ1 satisfies 1 ≤ ≤ θ 1 A A min max . Especially when Veff=Vdc and 1 θ = 1, it satisfies max min max min max min max I = = ω CA CA ω (6) where Imax is the maximum current in the inductor or varactor. 4) When Vdc≤Veff≤Vdc+Amax, two segmental sinusoids respectively hold 2 2 2 θ 2 ω ⎛ ⎞⎛ ⎞ − ⎜ ⎟⎜ ⎟ + = ⎝ ⎠⎝ ⎠ dc min min max min V V I A CA ,for V V≥ eff , 2 2 1 ω ⎛ ⎞⎛ ⎞ − ⎜ ⎟⎜ ⎟ + = ⎝ ⎠⎝ ⎠ dc max max min max V V I A CA , for V V≤ eff , (7) where the ESF θ 2 satisfies 2 1 ≤ ≤ θ Amax min A . The oscillating periods in the above four regions can be calculated mathematically. 1) When Veff≤Vdc−Amin, the oscillating period is 2 T T LC = = max max π (8) 2) When Veff≥Vdc+Amax, the oscillating period is 2 T T LC = = min min π (9) 3) When Vdc−Amin≤Veff≤Vdc, the oscillating period is a sum of two intervals, T=T1+T2, shown in Fig. 4. T1 is the time on the first ellipse; T2 is the time on the second ellipse. At the ECV, the voltage and current of the varactor are Veff and Ieff. From (6) (8) and (9), we obtain the amplitude ratio max max min min A C A C = (10) Substituting (10) in (5) leads to the ESF θ1 2 2 1 θ 1 ⎛ ⎞⎛ ⎞ − − =− + ⎜ ⎟⎜ ⎟ ⎝ ⎠⎝ ⎠ eff dc eff dc min max VV VV A A (11) Thus, the oscillating period is, 1 1 2 2 2 π π θ π π ⎛⎞ ⎛⎞ − − + − ⎜⎟ ⎜⎟ ⎝⎠ ⎝⎠ =+ = + eff dc eff dc min max max min VV VV asin asin A A TTT T T ( ) 1 1 1 2 π θ ⎛ ⎞ ⎛⎞ ⎛⎞ − − = ++ − ⎜ ⎟ ⎜⎟ ⎜⎟ ⎝ ⎠ ⎝⎠ ⎝⎠ eff dc eff dc max min max min min max VV VV T T asin T asin T A A (12) 4) When Vdc≤Veff≤Vdc+Amax, The same as Case 3). Solving (7), we can obtain the ESF and oscillating period, 2 2 2 θ 1 ⎛ ⎞⎛ ⎞ − − =− + ⎜ ⎟⎜ ⎟ ⎝ ⎠⎝ ⎠ eff dc eff dc max min VV VV A A (13) ( ) 2 1 1 2 π θ ⎛ ⎞ ⎛⎞ ⎛⎞ − − = + +− + ⎜ ⎟ ⎜⎟ ⎜⎟ ⎝ ⎠ ⎝⎠ ⎝⎠ eff dc eff dc max min max min min max VV VV T T T asin T asin T A A (14) To validate the above method of oscillating period calculation, an ideal LC tank in Fig. 3(a) is simulated in HSPICE. Its parameters are L=10nH, Cmax=4pF, Cmin=1pF, and Amin=0.5V. In Fig. 6, the cross line is the simulation result in HSPICE, and the solid line is the calculation result from (12) and (14). The simulation agrees well with the calculation. As the oscillator has a very large signal swing (nearly full power supply), the oscillating period is interpolated between Tmax and Tmin. The resulting frequency-voltage (F-V) curve, which is shown in Fig. 6., varies linearly with ECV in a range defined by the oscillation amplitude. Although the capacitance-voltage (C-V) characteristic of MOS varactors is step-like, the F-V curve is well linear. Contrary to widely held beliefs in [8], the linear C-V relationship of MOS varactors is no need. IV. EXPERIMENT VALIDATION Fig. 7 shows the microphotograph of LC VCO in Fig.1. At a 3.3-V supply, the tail current of LC-VCO is 3.1mA, and the centre frequency is 1.08GHz. The oscillator’s tuning curve in Fig. 8 is obtained by the measurement of the fundamental frequency at different control voltages. On-chip differential spiral inductor is 12.38nH, so the single-end inductor features 6.19nH. The maximum and minimum capacitances in LC-VCO are 4.30pF (Cmax) and 3.180pF (Cmin). The L=10nH; Veff=2.5V Fmax=1.591GHz; Fmin=0.795GHZ Cmin=1.0pF; Cmax=4.0pF Fig. 6. Oscillator’s tuning curve: simulated in SPICE, and calculated by (12) and (14) Fig. 7. Microphotograph of CMOS LC VCO 891

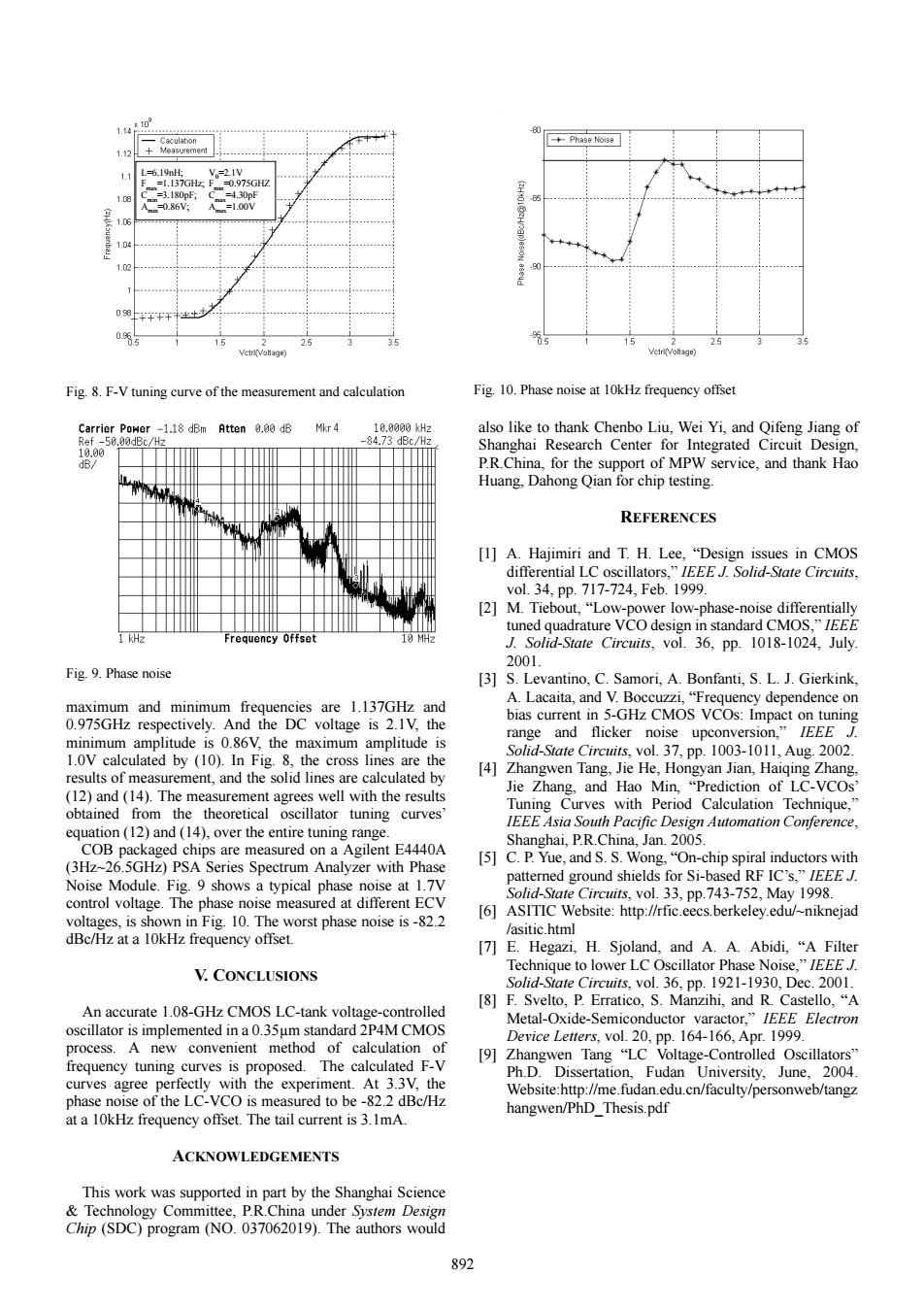

1.14 Phase Noise 112 975GH 1 3.180pf 4,0p .三0.86V: A=1.00 1. 1.04 0 0 15 1.5 2.5 Fig.8.F-V tuning curve of the measurement and calculation Fig.10.Phase noise at 10kHz frequency offset Carrier Power -1.18 dBm Atten 0.00 dB Mkr 4 1R9000kH also like to thank Chenbo Liu,Wei Yi,and Qifeng Jiang of Ret -51,uudBc/Hz 84.73 dBc/Hz 10.00 Shanghai Research Center for Integrated Circuit Design, d8/ P.R.China,for the support of MPW service,and thank Hao Huang,Dahong Qian for chip testing. REFERENCES [1]A.Hajimiri and T.H.Lee,"Design issues in CMOS differential LC oscillators."IEEE J.Solid-State Circuits. vol.34,pp.717-724,Feb.1999. [2]M.Tiebout,"Low-power low-phase-noise differentially tuned quadrature VCO design in standard CMOS,"IEEE 1 kHz Frequency offset J.Solid-State Circuits,vol.36,pp.1018-1024,July. 2001. Fig.9.Phase noise [3]S.Levantino,C.Samori,A.Bonfanti,S.L.J.Gierkink. maximum and minimum frequencies are 1.137GHz and A.Lacaita,and V.Boccuzzi,"Frequency dependence on 0.975GHz respectively.And the DC voltage is 2.1V,the bias current in 5-GHz CMOS VCOs:Impact on tuning range and flicker noise upconversion,"IEEE J. minimum amplitude is 0.86V,the maximum amplitude is 1.0V calculated by (10).In Fig.8,the cross lines are the Solid-State Circuits,vol.37,pp.1003-1011,Aug.2002. results of measurement,and the solid lines are calculated by [4]Zhangwen Tang,Jie He,Hongyan Jian,Haiqing Zhang, (12)and (14).The measurement agrees well with the results Jie Zhang,and Hao Min,"Prediction of LC-VCOs' Tuning Curves with Period Calculation Technique," obtained from the theoretical oscillator tuning curves' IEEE Asia South Pacific Design Automation Conference, equation(12)and(14),over the entire tuning range. Shanghai,P.R.China,Jan.2005. COB packaged chips are measured on a Agilent E4440A (3Hz~26.5GHz)PSA Series Spectrum Analyzer with Phase [5]C.P.Yue,and S.S.Wong,"On-chip spiral inductors with Noise Module.Fig.9 shows a typical phase noise at 1.7V patterned ground shields for Si-based RF IC's."IEEEJ. control voltage.The phase noise measured at different ECV Solid-State Circuits,vol.33,pp.743-752,May 1998. [6]ASITIC Website:http://rfic.eecs.berkeley.edu/-niknejad voltages,is shown in Fig.10.The worst phase noise is-82.2 /asitic.html dBc/Hz at a 10kHz frequency offset. [7]E.Hegazi,H.Sjoland,and A.A.Abidi,"A Filter Technique to lower LC Oscillator Phase Noise,"IEEEJ. V.CONCLUSIONS Solid-State Circuits,vol.36,pp.1921-1930,Dec.2001. [8]F.Svelto,P.Erratico,S.Manzihi,and R.Castello,"A An accurate 1.08-GHz CMOS LC-tank voltage-controlled Metal-Oxide-Semiconductor varactor,"IEEE Electron oscillator is implemented in a 0.35um standard 2P4M CMOS Device Letters,vol.20,pp.164-166,Apr.1999. process.A new convenient method of calculation of [9]Zhangwen Tang "LC Voltage-Controlled Oscillators" frequency tuning curves is proposed.The calculated F-V Ph.D.Dissertation,Fudan University,June,2004. curves agree perfectly with the experiment.At 3.3V.the Website:http://me.fudan.edu.cn/faculty/personweb/tangz phase noise of the LC-VCO is measured to be-82.2 dBc/Hz at a 10kHz frequency offset.The tail current is 3.1mA hangwen/PhD_Thesis.pdf ACKNOWLEDGEMENTS This work was supported in part by the Shanghai Science Technology Committee,P.R.China under System Design Chip (SDC)program (NO.037062019).The authors would 892

maximum and minimum frequencies are 1.137GHz and 0.975GHz respectively. And the DC voltage is 2.1V, the minimum amplitude is 0.86V, the maximum amplitude is 1.0V calculated by (10). In Fig. 8, the cross lines are the results of measurement, and the solid lines are calculated by (12) and (14). The measurement agrees well with the results obtained from the theoretical oscillator tuning curves’ equation (12) and (14), over the entire tuning range. COB packaged chips are measured on a Agilent E4440A (3Hz~26.5GHz) PSA Series Spectrum Analyzer with Phase Noise Module. Fig. 9 shows a typical phase noise at 1.7V control voltage. The phase noise measured at different ECV voltages, is shown in Fig. 10. The worst phase noise is -82.2 dBc/Hz at a 10kHz frequency offset. V. CONCLUSIONS An accurate 1.08-GHz CMOS LC-tank voltage-controlled oscillator is implemented in a 0.35µm standard 2P4M CMOS process. A new convenient method of calculation of frequency tuning curves is proposed. The calculated F-V curves agree perfectly with the experiment. At 3.3V, the phase noise of the LC-VCO is measured to be -82.2 dBc/Hz at a 10kHz frequency offset. The tail current is 3.1mA. ACKNOWLEDGEMENTS This work was supported in part by the Shanghai Science & Technology Committee, P.R.China under System Design Chip (SDC) program (NO. 037062019). The authors would also like to thank Chenbo Liu, Wei Yi, and Qifeng Jiang of Shanghai Research Center for Integrated Circuit Design, P.R.China, for the support of MPW service, and thank Hao Huang, Dahong Qian for chip testing. REFERENCES [1] A. Hajimiri and T. H. Lee, “Design issues in CMOS differential LC oscillators,” IEEE J. Solid-State Circuits, vol. 34, pp. 717-724, Feb. 1999. [2] M. Tiebout, “Low-power low-phase-noise differentially tuned quadrature VCO design in standard CMOS,” IEEE J. Solid-State Circuits, vol. 36, pp. 1018-1024, July. 2001. [3] S. Levantino, C. Samori, A. Bonfanti, S. L. J. Gierkink, A. Lacaita, and V. Boccuzzi, “Frequency dependence on bias current in 5-GHz CMOS VCOs: Impact on tuning range and flicker noise upconversion,” IEEE J. Solid-State Circuits, vol. 37, pp. 1003-1011, Aug. 2002. [4] Zhangwen Tang, Jie He, Hongyan Jian, Haiqing Zhang, Jie Zhang, and Hao Min, “Prediction of LC-VCOs’ Tuning Curves with Period Calculation Technique,” IEEE Asia South Pacific Design Automation Conference, Shanghai, P.R.China, Jan. 2005. [5] C. P. Yue, and S. S. Wong, “On-chip spiral inductors with patterned ground shields for Si-based RF IC’s,” IEEE J. Solid-State Circuits, vol. 33, pp.743-752, May 1998. [6] ASITIC Website: http://rfic.eecs.berkeley.edu/~niknejad /asitic.html [7] E. Hegazi, H. Sjoland, and A. A. Abidi, “A Filter Technique to lower LC Oscillator Phase Noise,” IEEE J. Solid-State Circuits, vol. 36, pp. 1921-1930, Dec. 2001. [8] F. Svelto, P. Erratico, S. Manzihi, and R. Castello, “A Metal-Oxide-Semiconductor varactor,” IEEE Electron Device Letters, vol. 20, pp. 164-166, Apr. 1999. [9] Zhangwen Tang “LC Voltage-Controlled Oscillators” Ph.D. Dissertation, Fudan University, June, 2004. Website:http://me.fudan.edu.cn/faculty/personweb/tangz hangwen/PhD_Thesis.pdf L=6.19nH; V0=2.1V Fmax=1.137GHz; Fmin=0.975GHZ Cmin=3.180pF; Cmax=4.30pF Amin=0.86V; Amax=1.00V Fig. 8. F-V tuning curve of the measurement and calculation Fig. 10. Phase noise at 10kHz frequency offset Fig. 9. Phase noise 892