第2期 电子学报 ol.30o.2 2002年2月 ACTA HECTRONICA SINICA Feb.2002 一种新型的高速FR滤波器及其LSI实现 唐长文张洁,闵昊 (复旦大学专用集成电路与系统因家重点实验室,上海200433) 摘要:本文提出了一种新型的高速滤波器结构,此结构的核心是一种独特的乘加单元.该乘加单元是通过对 BOOTH型乘法器与高速加法器结构的深入研究而探索出来的.采用该乘加单元我们可以实现任何阶数高速FR滤波 器.在文章的最后我们采用该结构实现了视频编码器中的一个高速色度滤波器,并与采用传统结构设计的该滤波器进 行了性能比较 关键词:有限冲击响应滤波器(FIR filter);MSI;BOOTH乘法器,加法树 中图分类号:TP302.1 文献标识码:A 文章编号:03722112(2002)02029503 A New High Speed FIR Filter Structure and VLSI Implementation TANG Zhang wen,ZHANGJie ,MIN Hao (ASIC System State Key Lab.,Fudan University,Shanghai 200433,China) Abstract:This paper presents a new highr speed FIR Filter structure which includes a unique multiplieradder unit.Through studying BOOTH multiplier and highr speed adder structures,we explored a new multipiler add unit.With this multiplieradder unit,we can implement FIR filters with any orders.In the end,we design a chroma FIR filter with this type fitler,and compare to the filter em ployed with the converntional structure. Key words:finite impulse response filter;very large scale IC:BOOTH multiplier;adder array tree 1引言 己经研究得非常成熟2引.文献[2]乘法器结构(图2)是采用 FR滤波器在视频和通信电路中的应用越来越广泛,对 了改进型Booth算法和Wallace加法树的并行结构.它主要包 其速度的要求也越来越高.传统的FR滤波器结构图)己 括下面三个模块Booth编码、部分积加法器阵列和进位加法 不能满足高速系统的要求,其主要原因是由于受到乘法器和 器,这种结构通过采用改进型Booh算法,部分积的数目减少 加法器电路的限制 了一半,由于乘法器是N位,因此将有[N/2]个部分积.部分 FR滤波器的公式为: 积加法器阵列将这[N/21个部分积相加生成2N位的进位项 V.I (Cany)和2N位的和项(Sum).最后,进位加法器将2N位的进 y(n=∑h(对x(n. 1 0 位项和2N位的和项相加产生乘积 图1中的滤波器的最大延时为TM+MT4,IM为一个乘法 2.242压缩加法器 器的延迟,工为一个加法器的延迟,M为滤波器的阶数.明显 为了提高并行性,一种特殊的加法单元:4:2压缩加法 可以看出最大延时随着滤波器的阶数的增加将迅速增加 器,作为基本加法器单元代替了全加器.4:2压缩加法器单元 本文提出了一种新型的高速滤波器结构,此结构的核心 如图3所示.它有五个输入和三个输出,能够将四个部分积 是一种独特的乘加单元.该乘加单元是通过对BOOTH型乘法 (1,2,B,4)压缩为两对新的部分积(S,C.4:2压缩加法 器与高速加法器结构的深入研究而探索出来的.采用该乘加 器可以用两个全加器等效, 单元我们可以实现任何阶数高速FR滤波器,它的最大延时 3新型的乘加单元 几乎不随滤波器的阶数的增加而增加.在文章的最后我们采 3.1乘法器和加法器 用该结构实现了视频编码器中的一个高速色度滤波器,并与 图1中加法器的输入端为M个乘法器的乘积项.而每一 采用传统结构设计的该滤波器进行了性能比较 个乘法器的乘积项是由一个2N位的加法器产生的.这样的 2 BOOTH乘法器 结构必然导致滤波器的延时是TM+MD,它将随着阶数的增 2.1B0OTH乘法器结构 加而显著增加. 乘法器是数字信号处理电路中最常用的单元,十年前就 变化一下乘法器结构,将所有乘法器中的相同的2N位 收稿日期:2001-0-19:修回日期:2001-0730 基金项目:上海市应用材料研究与发展基金(No.0108) 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

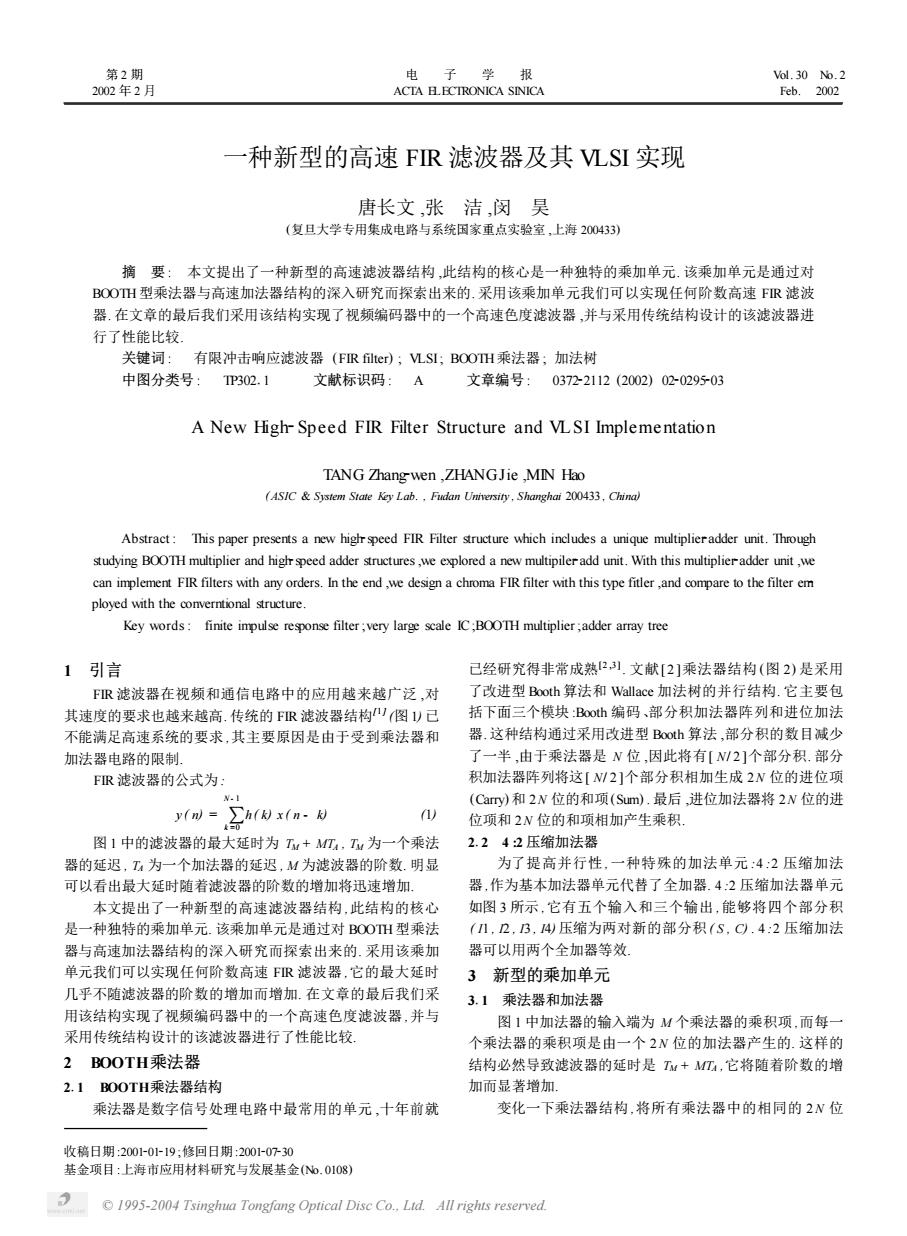

一种新型的高速 FIR 滤波器及其 VLSI 实现 唐长文 ,张 洁 ,闵 昊 (复旦大学专用集成电路与系统国家重点实验室 ,上海 200433) 摘 要 : 本文提出了一种新型的高速滤波器结构 ,此结构的核心是一种独特的乘加单元. 该乘加单元是通过对 BOOTH型乘法器与高速加法器结构的深入研究而探索出来的. 采用该乘加单元我们可以实现任何阶数高速 FIR 滤波 器. 在文章的最后我们采用该结构实现了视频编码器中的一个高速色度滤波器 ,并与采用传统结构设计的该滤波器进 行了性能比较. 关键词 : 有限冲击响应滤波器 (FIR filter) ; VLSI; BOOTH乘法器 ; 加法树 中图分类号 : TP30211 文献标识码 : A 文章编号 : 037222112 (2002) 0220295203 A New High2Speed FIR Filter Structure and VLSI Implementation TANG Zhang2wen ,ZHANGJie ,MIN Hao ( ASIC & System State Key Lab. , Fudan University , Shanghai 200433 , China) Abstract : This paper presents a new high2speed FIR Filter structure which includes a unique multiplier2adder unit. Through studying BOOTH multiplier and high2speed adder structures ,we explored a new multipiler2add unit. With this multiplier2adder unit ,we can implement FIR filters with any orders. In the end ,we design a chroma FIR filter with this type fitler ,and compare to the filter em2 ployed with the converntional structure. Key words : finite impulse response filter ;very large scale IC ;BOOTH multiplier ;adder array tree 1 引言 FIR 滤波器在视频和通信电路中的应用越来越广泛 ,对 其速度的要求也越来越高. 传统的 FIR 滤波器结构[1 ] (图 1) 已 不能满足高速系统的要求 ,其主要原因是由于受到乘法器和 加法器电路的限制. FIR 滤波器的公式为 : y ( n) = ∑ N - 1 k =0 h ( k) x ( n - k) (1) 图 1 中的滤波器的最大延时为 TM + MTA , TM 为一个乘法 器的延迟 , TA 为一个加法器的延迟 , M 为滤波器的阶数. 明显 可以看出最大延时随着滤波器的阶数的增加将迅速增加. 本文提出了一种新型的高速滤波器结构 ,此结构的核心 是一种独特的乘加单元. 该乘加单元是通过对 BOOTH 型乘法 器与高速加法器结构的深入研究而探索出来的. 采用该乘加 单元我们可以实现任何阶数高速 FIR 滤波器 ,它的最大延时 几乎不随滤波器的阶数的增加而增加. 在文章的最后我们采 用该结构实现了视频编码器中的一个高速色度滤波器 ,并与 采用传统结构设计的该滤波器进行了性能比较. 2 BOOTH乘法器 211 BOOTH乘法器结构 乘法器是数字信号处理电路中最常用的单元 ,十年前就 已经研究得非常成熟[2 ,3 ] . 文献[ 2 ]乘法器结构 (图 2) 是采用 了改进型 Booth 算法和 Wallace 加法树的并行结构. 它主要包 括下面三个模块 :Booth 编码、部分积加法器阵列和进位加法 器. 这种结构通过采用改进型 Booth 算法 ,部分积的数目减少 了一半 ,由于乘法器是 N 位 ,因此将有[ N/ 2 ]个部分积. 部分 积加法器阵列将这[ N/ 2 ]个部分积相加生成 2N 位的进位项 (Carry) 和 2N 位的和项(Sum) . 最后 ,进位加法器将 2N 位的进 位项和 2N 位的和项相加产生乘积. 212 4 :2 压缩加法器 为了提高并行性 ,一种特殊的加法单元 :4 :2 压缩加法 器 ,作为基本加法器单元代替了全加器. 4 :2 压缩加法器单元 如图 3 所示 ,它有五个输入和三个输出 ,能够将四个部分积 ( I1 , I2 , I3 , I4) 压缩为两对新的部分积 ( S , C) . 4 :2 压缩加法 器可以用两个全加器等效. 3 新型的乘加单元 311 乘法器和加法器 图 1 中加法器的输入端为 M 个乘法器的乘积项 ,而每一 个乘法器的乘积项是由一个 2N 位的加法器产生的. 这样的 结构必然导致滤波器的延时是 TM + MTA ,它将随着阶数的增 加而显著增加. 变化一下乘法器结构 ,将所有乘法器中的相同的 2N 位 收稿日期 :2001201219 ;修回日期 :2001207230 基金项目 :上海市应用材料研究与发展基金(No. 0108) 第 2 期 2002 年 2 月 电 子 学 报 ACTA ELECTRONICA SINICA Vol. 30 No. 2 Feb. 2002 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

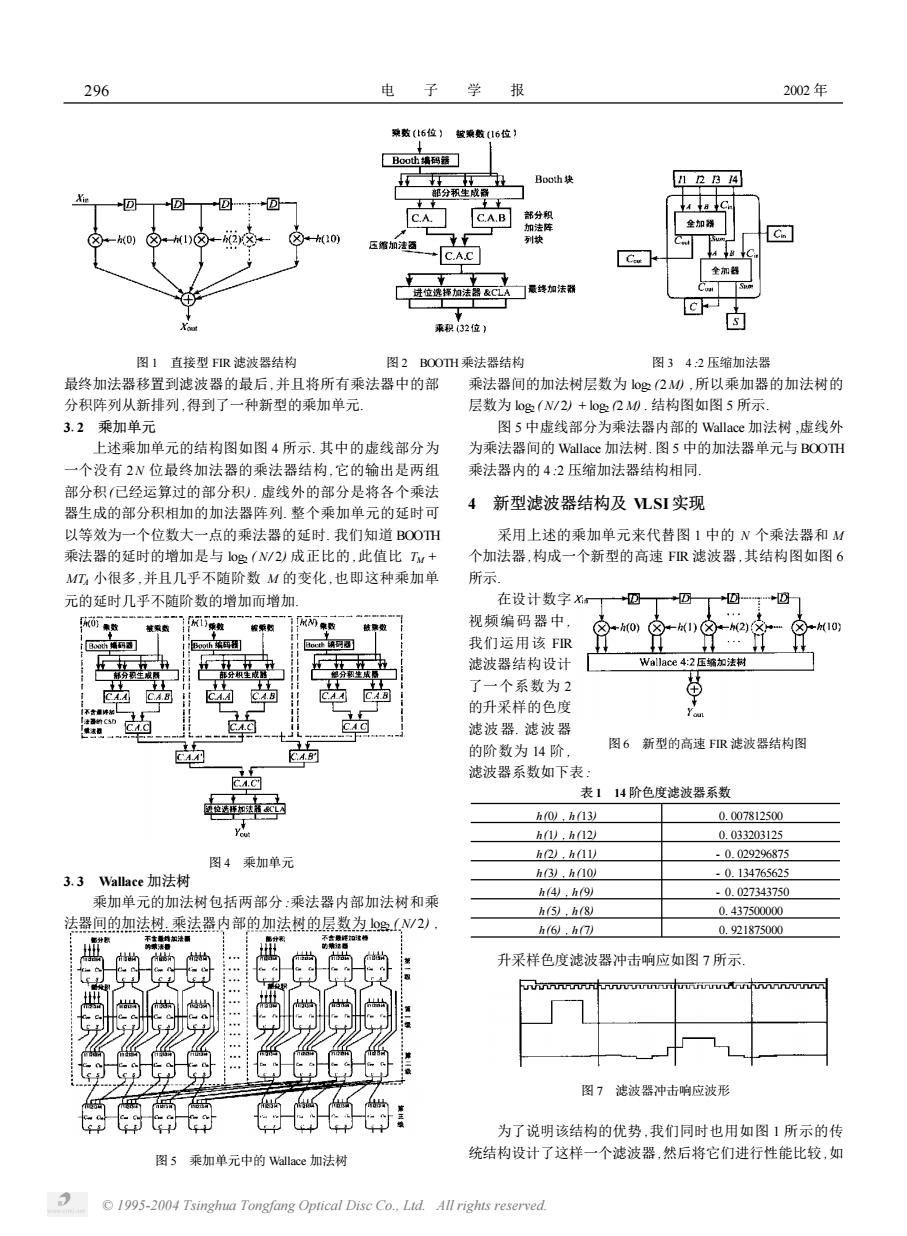

296 电子学报 2002年 乘数(t6位】被兼戴16位】 Boo出墙码籍 h Bh块 I R B 14 都分积生成器 回 A C C.A. CA.B部分积 加法库 全加滑 -0) 压缩加法一→「 列块 C.A.C 全加器 进位选郴加法器&C 门藏终加法器 乘积(32位) 图1直接型FIR滤波器结构 图2 BOOTH乘法器结构 图342压缩加法器 最终加法器移置到滤波器的最后,并且将所有乘法器中的部 乘法器间的加法树层数为og(2M,所以乘加器的加法树的 分积阵列从新排列,得到了一种新型的乘加单元 层数为og(N/2)+log20.结构图如图5所示. 3.2乘加单元 图5中虚线部分为乘法器内部的Wallace加法树,虚线外 上述乘加单元的结构图如图4所示.其中的虚线部分为 为乘法器间的Wallace加法树.图5中的加法器单元与BOOTH 一个没有2N位最终加法器的乘法器结构,它的输出是两组 乘法器内的42压缩加法器结构相同 部分积已经运算过的部分积).虚线外的部分是将各个乘法 器生成的部分积相加的加法器阵列.整个乘加单元的延时可 4新型滤波器结构及LSI实现 以等效为一个位数大一点的乘法器的延时.我们知道BOOTH 采用上述的乘加单元来代替图1中的N个乘法器和M 乘法器的延时的增加是与og(N/2)成正比的,此值比TIM+ 个加法器,构成一个新型的高速FR滤波器,其结构图如图6 MT小很多,并且几乎不随阶数M的变化,也即这种乘加单 所示 元的延时几乎不随阶数的增加而增加 在设计数字 城。 视频编码器中 (0) 2 (10 我们运用该FR 1 滤波器结构设计 Wallace4:2压缩加法制 分生 牙生 了一个系数为2 CAA 的升采样的色度 滤波器.滤波器 的阶数为14阶, 图6新型的高速FIR滤波器结构图 4.A 滤波器系数如下表: CA.C 表114阶色度滤波器系数 h0,h13) 0.007812500 h1),h12 0.033203125 h2),h11 -0.029296875 图4乘加单元 .0.134765625 3.3 Wallace加法树 h3),h10) h(4),h9 -0.027343750 乘加单元的加法树包括两部分:乘法器内部加法树和乘 h5),h8) 0.437500000 法器间的加法树.乘法器内部的加法树的层数为o9.(N/2), h6),h7 0.921875000 升采样色度滤波器冲击响应如图7所示 hnnnnnnnnnninnnuninnAnnnnnnnnnn 图7滤波器冲击响应波形 的的 为了说明该结构的优势,我们同时也用如图1所示的传 图5乘加单元中的Wallace加法树 统结构设计了这样一个滤波器,然后将它们进行性能比较,如 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

图 1 直接型 FIR 滤波器结构 图 2 BOOTH 乘法器结构 图 3 4 :2 压缩加法器 最终加法器移置到滤波器的最后 ,并且将所有乘法器中的部 分积阵列从新排列 ,得到了一种新型的乘加单元. 312 乘加单元 上述乘加单元的结构图如图 4 所示. 其中的虚线部分为 一个没有 2N 位最终加法器的乘法器结构 ,它的输出是两组 部分积(已经运算过的部分积) . 虚线外的部分是将各个乘法 器生成的部分积相加的加法器阵列. 整个乘加单元的延时可 以等效为一个位数大一点的乘法器的延时. 我们知道 BOOTH 乘法器的延时的增加是与 log2 ( N/ 2) 成正比的 ,此值比 TM + MTA 小很多 ,并且几乎不随阶数 M 的变化 ,也即这种乘加单 元的延时几乎不随阶数的增加而增加. 图 4 乘加单元 图 5 乘加单元中的 Wallace 加法树 313 Wallace 加法树 乘加单元的加法树包括两部分 :乘法器内部加法树和乘 法器间的加法树. 乘法器内部的加法树的层数为 log2 ( N/ 2) , 乘法器间的加法树层数为 log2 (2M) ,所以乘加器的加法树的 层数为 log2 ( N/ 2) + log2 (2 M) . 结构图如图 5 所示. 图 5 中虚线部分为乘法器内部的 Wallace 加法树 ,虚线外 为乘法器间的 Wallace 加法树. 图 5 中的加法器单元与 BOOTH 乘法器内的 4 :2 压缩加法器结构相同. 4 新型滤波器结构及 VLSI实现 采用上述的乘加单元来代替图 1 中的 N 个乘法器和 M 个加法器 ,构成一个新型的高速 FIR 滤波器 ,其结构图如图 6 所示. 图 6 新型的高速 FIR 滤波器结构图 在设计数字 视频编码器中 , 我们运用该 FIR 滤波器结构设计 了一个系数为 2 的升采样的色度 滤波器. 滤波器 的阶数为 14 阶 , 滤波器系数如下表 : 表 1 14 阶色度滤波器系数 h (0) , h (13) 0. 007812500 h (1) , h (12) 0. 033203125 h (2) , h (11) - 0. 029296875 h (3) , h (10) - 0. 134765625 h (4) , h (9) - 0. 027343750 h (5) , h (8) 0. 437500000 h (6) , h (7) 0. 921875000 升采样色度滤波器冲击响应如图 7 所示. 图 7 滤波器冲击响应波形 为了说明该结构的优势 ,我们同时也用如图 1 所示的传 统结构设计了这样一个滤波器 ,然后将它们进行性能比较 ,如 692 电 子 学 报 2002 年 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

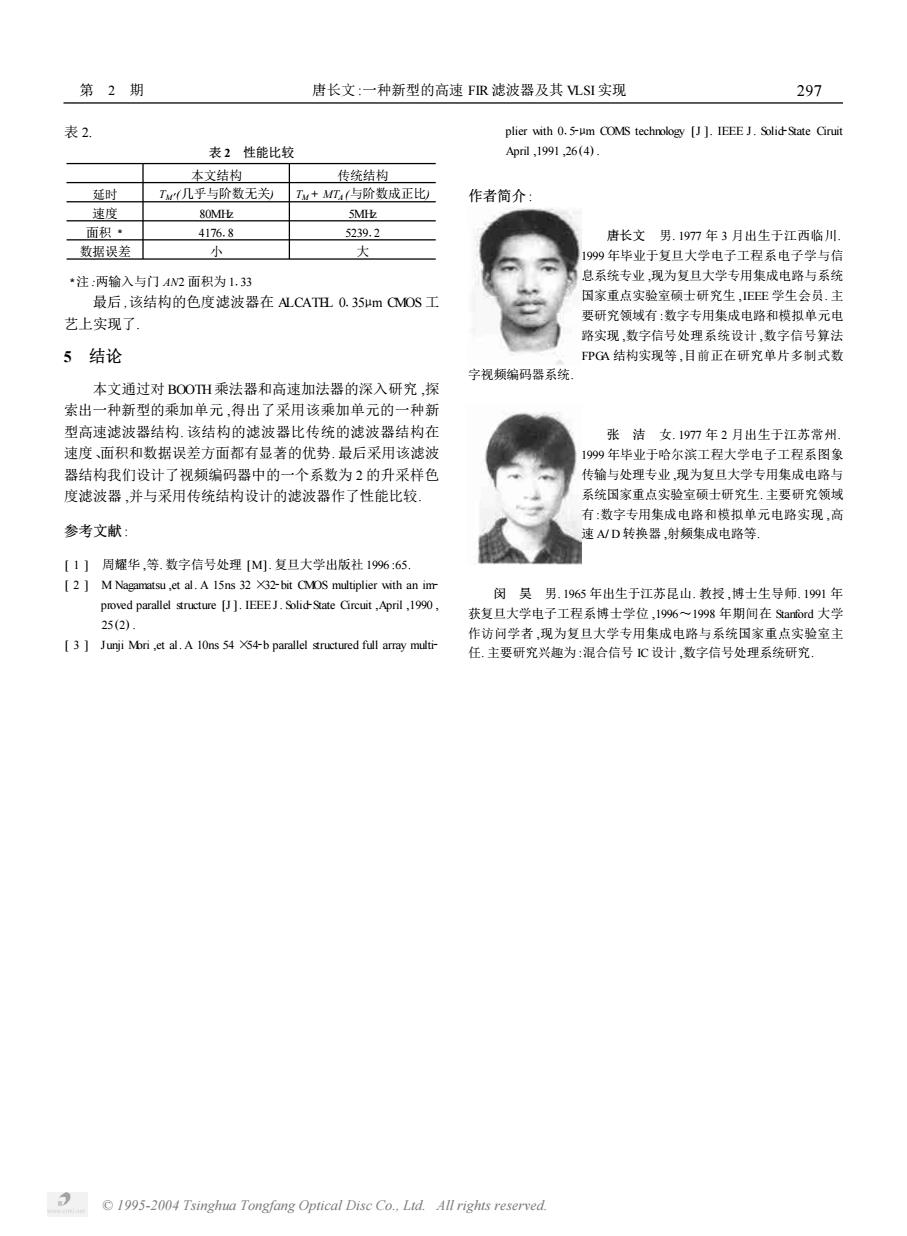

第2期 唐长文:一种新型的高速FR滤波器及其MSI实现 297 表2. plier with 0.5-um COMS technology [J ]IEEE J.Solid-Sate Ciruit 表2性能比较 Apl,1991,26(4) 本文结构 传统结构 延时 I几乎与阶数无关) Tw+MT,与阶数成正比 作者简介: 速度 80MHz 5MHz 面积· 4176.8 5239.2 唐长文男.1977年3月出生于江西临川 数据误差 小 大 1999年毕业于复旦大学电子工程系电子学与信 注:两输入与门AN2面积为1.33 息系统专业,现为复旦大学专用集成电路与系统 最后,该结构的色度滤波器在ALCATH0.35 m CMOS工 国家重点实验室硕士研究生,E正E学生会员.主 艺上实现了. 要研究领域有:数字专用集成电路和模拟单元电 路实现,数字信号处理系统设计,数字信号算法 5结论 FPGA结构实现等,目前正在研究单片多制式数 字视频编码器系统 本文通过对BOOH乘法器和高速加法器的深入研究探 索出一种新型的乘加单元,得出了采用该乘加单元的一种新 型高速滤波器结构.该结构的滤波器比传统的滤波器结构在 张洁女.1977年2月出生于江苏常州 速度、面积和数据误差方面都有显著的优势.最后采用该滤波 1999年毕业于哈尔滨工程大学电子工程系图象 器结构我们设计了视频编码器中的一个系数为2的升采样色 传输与处理专业,现为复旦大学专用集成电路与 度滤波器,并与采用传统结构设计的滤波器作了性能比较 系统国家重点实验室硕士研究生.主要研究领域 有:数字专用集成电路和模拟单元电路实现,高 参考文献」 速AWD转换器,射频集成电路等, 【1】周耀华,等.数字信号处理[M).复旦大学出版社1996:65. 2 M Nagamatsu ,et al.A 15ns 32 X32-bit CMOS multiplier with an im 闵吴男.1965年出生于江苏昆山.教授,博士生导师.1991年 proved parallel structure [J].IEEEJ.Solid-Sate Circuit,April,1990, 获复旦大学电子工程系博士学位,1996~1998年期间在Sa心ord大学 25(2). 作访问学者,现为复旦大学专用集成电路与系统国家重点实验室主 [3]Junji Mori ,et al.A 10ns 54 X54-b parallel structured full array multi- 任.主要研究兴趣为:混合信号C设计,数字信号处理系统研究 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

表 2. 表 2 性能比较 本文结构 传统结构 延时 TM′(几乎与阶数无关) TM + MTA (与阶数成正比) 速度 80MHz 5MHz 面积 3 417618 523912 数据误差 小 大 3 注 :两输入与门 AN2 面积为 1133 最后 ,该结构的色度滤波器在 ALCATEL 0135μm CMOS 工 艺上实现了. 5 结论 本文通过对 BOOTH乘法器和高速加法器的深入研究 ,探 索出一种新型的乘加单元 ,得出了采用该乘加单元的一种新 型高速滤波器结构. 该结构的滤波器比传统的滤波器结构在 速度、面积和数据误差方面都有显著的优势. 最后采用该滤波 器结构我们设计了视频编码器中的一个系数为 2 的升采样色 度滤波器 ,并与采用传统结构设计的滤波器作了性能比较. 参考文献 : [ 1 ] 周耀华 ,等. 数字信号处理 [M] . 复旦大学出版社 1996 :65. [ 2 ] M Nagamatsu ,et al. A 15ns 32 ×322bit CMOS multiplier with an im2 proved parallel structure [J ] . IEEE J . Solid2State Circuit ,April ,1990 , 25(2) . [ 3 ] Junji Mori ,et al. A 10ns 54 ×542b parallel structured full array multi2 plier with 0152μm COMS technology [J ] . IEEE J . Solid2State Ciruit April ,1991 ,26 (4) . 作者简介 : 唐长文 男. 1977 年 3 月出生于江西临川. 1999 年毕业于复旦大学电子工程系电子学与信 息系统专业 ,现为复旦大学专用集成电路与系统 国家重点实验室硕士研究生 ,IEEE 学生会员. 主 要研究领域有 :数字专用集成电路和模拟单元电 路实现 ,数字信号处理系统设计 ,数字信号算法 FPGA 结构实现等 ,目前正在研究单片多制式数 字视频编码器系统. 张 洁 女. 1977 年 2 月出生于江苏常州. 1999 年毕业于哈尔滨工程大学电子工程系图象 传输与处理专业 ,现为复旦大学专用集成电路与 系统国家重点实验室硕士研究生. 主要研究领域 有 :数字专用集成电路和模拟单元电路实现 ,高 速 A/ D 转换器 ,射频集成电路等. 闵 昊 男. 1965 年出生于江苏昆山. 教授 ,博士生导师. 1991 年 获复旦大学电子工程系博士学位 ,1996~1998 年期间在 Stanford 大学 作访问学者 ,现为复旦大学专用集成电路与系统国家重点实验室主 任. 主要研究兴趣为 :混合信号 IC 设计 ,数字信号处理系统研究. 第 2 期 唐长文 :一种新型的高速 FIR 滤波器及其 VLSI实现 792 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved