第31卷第6期 微电子学 Vol.31,No 6 2001年12月 M icroelectronics Dec.2001 文章编号:1004-3365(2001)06-0451-04 一种高速直接数字频率合成器及其FPGA实现 唐长文,闵吴 (复旦大学专用集成电路与系统国家实验室,上海200433) 摘,要:介绍了一种用于QAM调制和解调的直接数字频率合成器,该电路同时输出10位正弦 和余弦两种波形,系统时钟频率为50MHz,信号的谐波小宇.72B。输出信号的范围为DC到25 MH乙,信号频率步长为0.0116Hz,相应的转换速度为20ns,建立时间延迟为4个时钟。直接数字 合成器DDFS)采用一种有效查找表的方式生成正弦函数,为了降低ROM的大小,采用了1/8正 弦波形函数压缩算法。直接数字频率合成器的数字部分由X ilinx FPGA实现,最后通过数模转换 器输出。 关键词数字频率合成器;锁相环现场可编程逻辑阵列,查找表,只读存储器 中图分类号.TN431.2 文献标识码:A A D irect D igital Frequency Syn thesizer mplem en ted with FPGA TAN G Zhangwen,M N Hao (S tate K ey L aboratory gf A S IC Systems,Fudan Univ.,Shanghai 200433,P.R.China) Abstract A direct digital frequency synthesizer (DDFS)used for QAM modulation and demodulation is presented,which synthesizes a 10-b output sine and cosine wave w ith a spectral purity of-70 dB at 50MHz.The synthesizer covers a bandw idth from de to 25M Hz in 0.0116 Hz step w ith a corresponding sw itching speed of 20 ns and a tuning latency of 4 clck cycles.An efficient look-up table method for calculating the sine function is used, and a compressed algorithm that only calculates 1/8 sine function is employed to reduce the volume of ROM.The whole digital system is mplem ented w ith Xilinx FPGA,and the digital signals are output through two DA converters. Key words Digital frequency synthesizer,Phase bcked loop;FPGA;Look up table;ROM EEACC:1265 引 言 传统的宽带频率合成器采用锁相环结构。直接 数字频率合成器比锁相环结构具有更多的优点:建 图2QAM解调 立时间快转换时间快,频率精度高、频率纯度高、频 本文的直接数字频率合成器核心采用的结构最 带宽等。因此,直接数字频率合成技术在CDMA数 先由T ieney、Rader和Gold提出,如图3所示。它 字蜂窝电话、宽带无线LAN网、HDTV中得到广泛 的应用。特别地,随着模数转换器(ADC)四技术的 利用可溢出的L位累加器(或称相位累加器)产生 发展,使得直接数字频率合成更适合RF应用,如图 正弦函数的相位变量。相位累加器每溢出一次,就代 1QAM调制和图2QAM解调。 表正弦波形一个周期。相位累加器输入的频率控制 字(FCW)来控制生成的正弦波形的频率。正弦函 数发生器是存有正弦采样值的ROM查找表。这种 频率合成方法可以在不增加ROM查找表容量的情 况下,获得高的频率精度。相位累加器每增加一位, 频率精度就提高2倍。直接数字频率合成器的输出 图1QAM调制 频率f可以由下式确定 收稿日期:2001-01-19定稿日期2001-04-05 1995-2004 Tsinghua Tongfang Optical Disc Co.,Ltd.All rights reserved

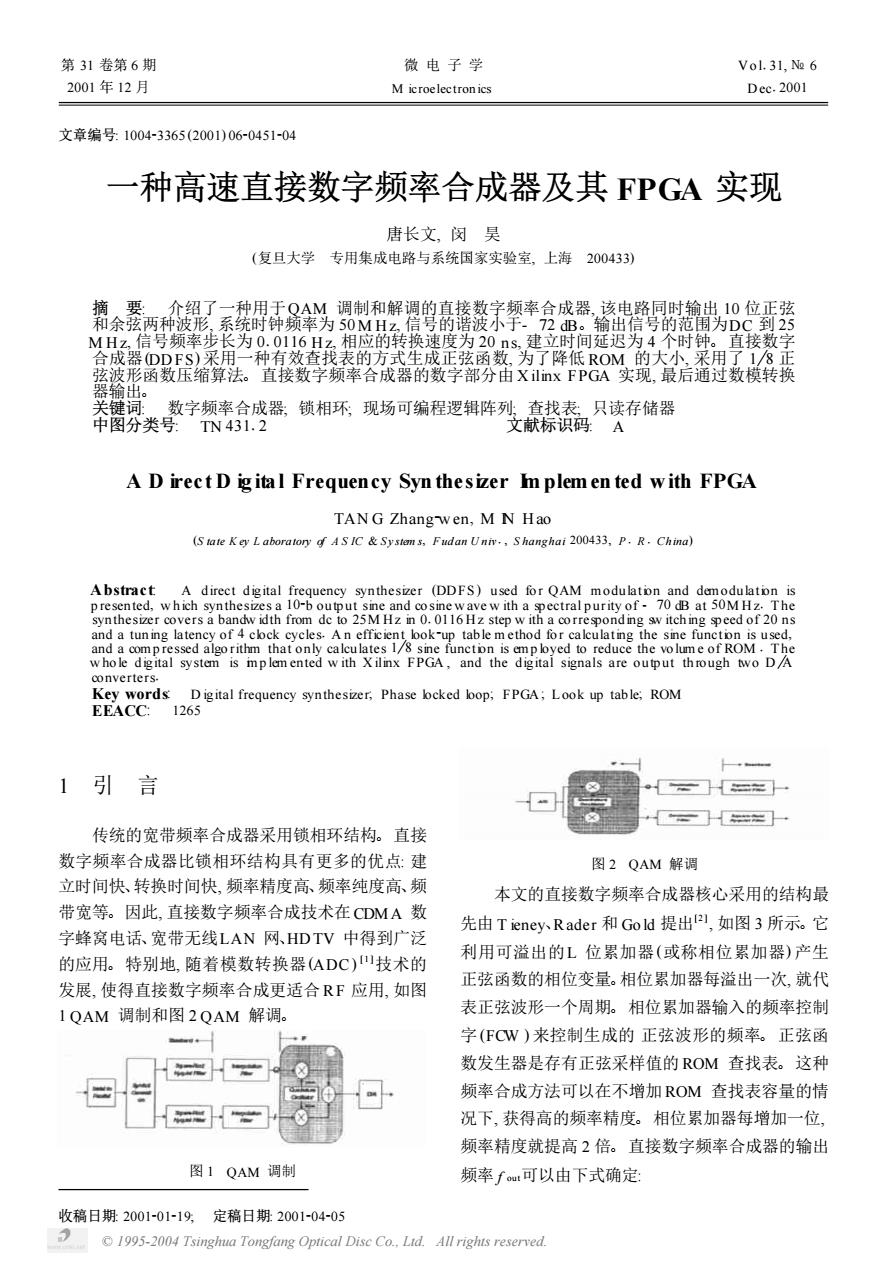

收稿日期: 2001201219; 定稿日期: 2001204205 文章编号: 100423365 (2001) 0620451204 一种高速直接数字频率合成器及其 FPGA 实现 唐长文, 闵 昊 (复旦大学 专用集成电路与系统国家实验室, 上海 200433) 摘 要: 介绍了一种用于QAM 调制和解调的直接数字频率合成器, 该电路同时输出 10 位正弦 和余弦两种波形, 系统时钟频率为 50M H z, 信号的谐波小于- 72 dB。输出信号的范围为DC 到 25 M H z, 信号频率步长为 010116 H z, 相应的转换速度为 20 n s, 建立时间延迟为 4 个时钟。直接数字 合成器(DD FS) 采用一种有效查找表的方式生成正弦函数, 为了降低 ROM 的大小, 采用了 1ö8 正 弦波形函数压缩算法。直接数字频率合成器的数字部分由 X ilinx FPGA 实现, 最后通过数模转换 器输出。 关键词: 数字频率合成器; 锁相环; 现场可编程逻辑阵列; 查找表; 只读存储器 中图分类号: TN 43112 文献标识码: A A D irect D ig ita l Frequency Syn thesizer Im plem en ted w ith FPGA TAN G Zhang2w en, M IN H ao (S tate K ey L aboratory of A S IC & S y stem s, F ud an U niv1, S hang hai 200433, P 1 R 1 Ch ina) Abstract: A direct digital frequency synthesizer (DD FS) used fo r QAM modulation and demodulation is p resented, w h ich synthesizes a 102b output sine and co sine w ave w ith a spectral purity of - 70 dB at 50M H z1 T he synthesizer covers a bandw idth from dc to 25M H z in 010116 H z step w ith a co rresponding sw itch ing speed of 20 ns and a tuning latency of 4 clock cycles1 A n efficient look2up table m ethod fo r calculating the sine function is used, and a comp ressed algo rithm that only calculates 1ö8 sine function is emp loyed to reduce the vo lum e of ROM 1 T he w ho le digital system is imp lem ented w ith X ilinx FPGA , and the digital signals are output th rough tw o DöA converters1 Key words: D igital frequency synthesizer; Phase locked loop; FPGA ; L ook up table; ROM EEACC: 1265 1 引 言 传统的宽带频率合成器采用锁相环结构。直接 数字频率合成器比锁相环结构具有更多的优点: 建 立时间快、转换时间快, 频率精度高、频率纯度高、频 带宽等。因此, 直接数字频率合成技术在CDM A 数 字蜂窝电话、宽带无线LAN 网、HD TV 中得到广泛 的应用。特别地, 随着模数转换器(ADC) [ 1 ]技术的 发展, 使得直接数字频率合成更适合 R F 应用, 如图 1 QAM 调制和图 2 QAM 解调。 图 1 QAM 调制 图 2 QAM 解调 本文的直接数字频率合成器核心采用的结构最 先由 T ieney、R ader 和 Go ld 提出[ 2 ] , 如图 3 所示。它 利用可溢出的L 位累加器(或称相位累加器) 产生 正弦函数的相位变量。相位累加器每溢出一次, 就代 表正弦波形一个周期。相位累加器输入的频率控制 字 (FCW ) 来控制生成的 正弦波形的频率。正弦函 数发生器是存有正弦采样值的 ROM 查找表。这种 频率合成方法可以在不增加 ROM 查找表容量的情 况下, 获得高的频率精度。相位累加器每增加一位, 频率精度就提高 2 倍。直接数字频率合成器的输出 频率 f out可以由下式确定: 第 31 卷第 6 期 2001 年 12 月 微 电 子 学 M icroelectron ics V o l131, № 6 D ec12001 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

452 唐长文等:一种高速直接数字频率合成器及其FPGA实现 2001年 four=fk·FCw 2 (1) 其中,FCW为频率控制字,fe为时钟频率,L 为相位累加器的字长。最小频率精度△f为: ROM Address 4y= (2) clK clk]D Flp-Flop Q D Modification 图5累加器的简单优化 相位累加器优化结构的唯一缺点是在直接数字 频率合成的输出信号的频率中,引入了∫k*1的 图3直接数字频率合成器结构 相位偏移量。然而对于字长为32位,时钟频率为50 在本文DDFS核设计中,相位累加器字长为32 MHz的相位累加器,其偏移量只有0.0058Hz,在大 位,最高时钟频率是50MHz。因此,最小频率精度 多数应用中是可以忽略的。 为0.0116Hz。两个频率之间的转换时间为一个时 2.2正弦函数计算 钟,对于50MHz时钟,转换时间为20ns∞ 直接实现正弦函数需要22×10bROM。读取 ROM查找表输出的数字正弦采样值通过DA 大容量的ROM会降低系统速度,因此,有必要采用 转换器产生量化的模拟正弦波形,再通过低通滤波 正弦ROM压缩技术B4。 器去除高频分量,得到频率精度高的正弦波形输出。 当直接数字频率合成器产生的频率接近12时钟频 2.2.1正弦函数ROM查找表的取法 率时,第一级谐波很难滤除。在实际中,直接数字频 常用的一种技术是只存储π/2弧度的正弦采样 率合成的频率限制在40%时钟频率以内。 点,然后,利用正弦函数的1/4波形对称性,产生整个 2π弧度的正弦采样点。当用相位累加器的最高两位代 2结构设计 表正弦函数的象限,则最高位表示符号,次高位表示相 位在0-π2是增加还是减小,如图6所示。在大多数 2.1有限字长效应 直接数字频率合成实现中,数字都是两进制补码形 直接数字频率合成特性的优化主要在于有限字 式5。因此,ROM查找表的输入必须采用1/4相位的 长和正弦函数计算方法两方面。图4所示的功能 绝对值,并且输出要乘以1。这样,在求补的时候就会 块显示了三种基本的噪声源。它们分别是相位累加 引入12LSB的失调,如图7、图8所示。本文采用一 器截断P(n)、输出幅度量化A(n)和正弦函数压缩 进制补码代替两进制补码,它不会引入误差。正弦采样 误差G(·)。影响频率纯度的最主要误差源是相位 截断。一种相位累加器的简单优化如图5所示,它能 点的相位和幅度的1/2LSB失调是在生成ROM查找 够降低谐波幅度3B左右,同时在频率转换时,减 表时进行补偿的。这样,同时也节省了硬件,因为一进 小输出频谱对累加器中值的依赖。而且,优化结构使 制补码可以通过一组异或门来实现。 得相位累加器字长近似变为L+1。 Sine Funcdan …合区白 内 r e Phese Truncation Quarization Noise m几厂! 图4有限字长效应引入的噪声 图6采用对称结构的直接数字频率合成器 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

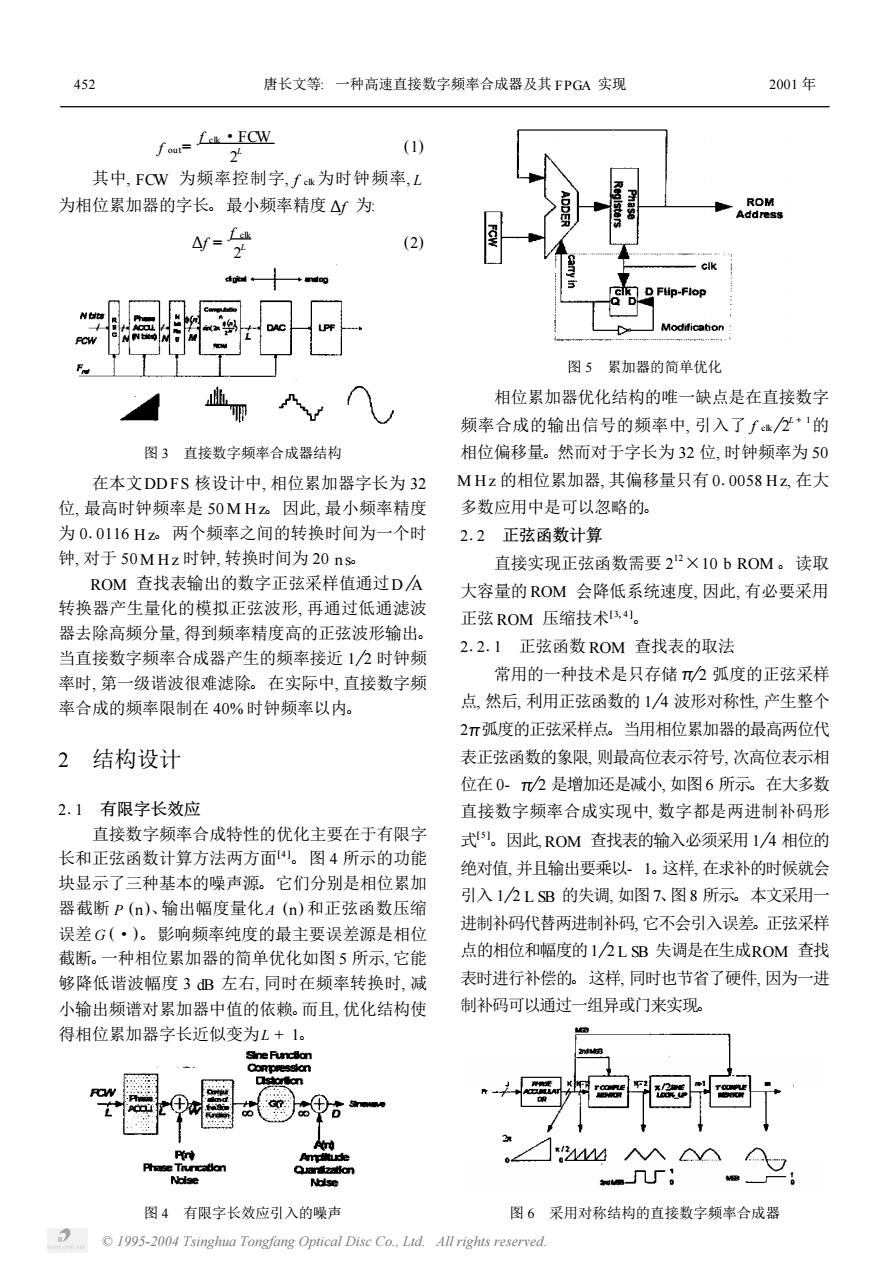

f out= f clk·FCW 2 L (1) 其中, FCW 为频率控制字, f clk为时钟频率, L 为相位累加器的字长。最小频率精度 ∃f 为: ∃f = f clk 2 L (2) 图 3 直接数字频率合成器结构 在本文DD FS 核设计中, 相位累加器字长为 32 位, 最高时钟频率是 50 M H z。因此, 最小频率精度 为 010116 H z。两个频率之间的转换时间为一个时 钟, 对于 50M H z 时钟, 转换时间为 20 n s。 ROM 查找表输出的数字正弦采样值通过DöA 转换器产生量化的模拟正弦波形, 再通过低通滤波 器去除高频分量, 得到频率精度高的正弦波形输出。 当直接数字频率合成器产生的频率接近 1ö2 时钟频 率时, 第一级谐波很难滤除。在实际中, 直接数字频 率合成的频率限制在 40% 时钟频率以内。 2 结构设计 211 有限字长效应 直接数字频率合成特性的优化主要在于有限字 长和正弦函数计算方法两方面[ 4 ]。图 4 所示的功能 块显示了三种基本的噪声源。它们分别是相位累加 器截断 P (n)、输出幅度量化A (n) 和正弦函数压缩 误差G (·)。影响频率纯度的最主要误差源是相位 截断。一种相位累加器的简单优化如图 5 所示, 它能 够降低谐波幅度 3 dB 左右, 同时在频率转换时, 减 小输出频谱对累加器中值的依赖。而且, 优化结构使 得相位累加器字长近似变为L + 1。 图 4 有限字长效应引入的噪声 图 5 累加器的简单优化 相位累加器优化结构的唯一缺点是在直接数字 频率合成的输出信号的频率中, 引入了 f clkö2 L + 1的 相位偏移量。然而对于字长为 32 位, 时钟频率为 50 M H z 的相位累加器, 其偏移量只有 010058 H z, 在大 多数应用中是可以忽略的。 212 正弦函数计算 直接实现正弦函数需要 2 12×10 b ROM。读取 大容量的 ROM 会降低系统速度, 因此, 有必要采用 正弦ROM 压缩技术[ 3, 4 ]。 21211 正弦函数 ROM 查找表的取法 常用的一种技术是只存储 Πö2 弧度的正弦采样 点, 然后, 利用正弦函数的 1ö4 波形对称性, 产生整个 2Π弧度的正弦采样点。当用相位累加器的最高两位代 表正弦函数的象限, 则最高位表示符号, 次高位表示相 位在 0- Πö2 是增加还是减小, 如图 6 所示。在大多数 直接数字频率合成实现中, 数字都是两进制补码形 式[ 5 ]。因此, ROM 查找表的输入必须采用 1ö4 相位的 绝对值, 并且输出要乘以- 1。这样, 在求补的时候就会 引入 1ö2 L SB 的失调, 如图 7、图 8 所示。本文采用一 进制补码代替两进制补码, 它不会引入误差。正弦采样 点的相位和幅度的1ö2 L SB 失调是在生成ROM 查找 表时进行补偿的。这样, 同时也节省了硬件, 因为一进 制补码可以通过一组异或门来实现。 图 6 采用对称结构的直接数字频率合成器 452 唐长文等: 一种高速直接数字频率合成器及其 FPGA 实现 2001 年 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

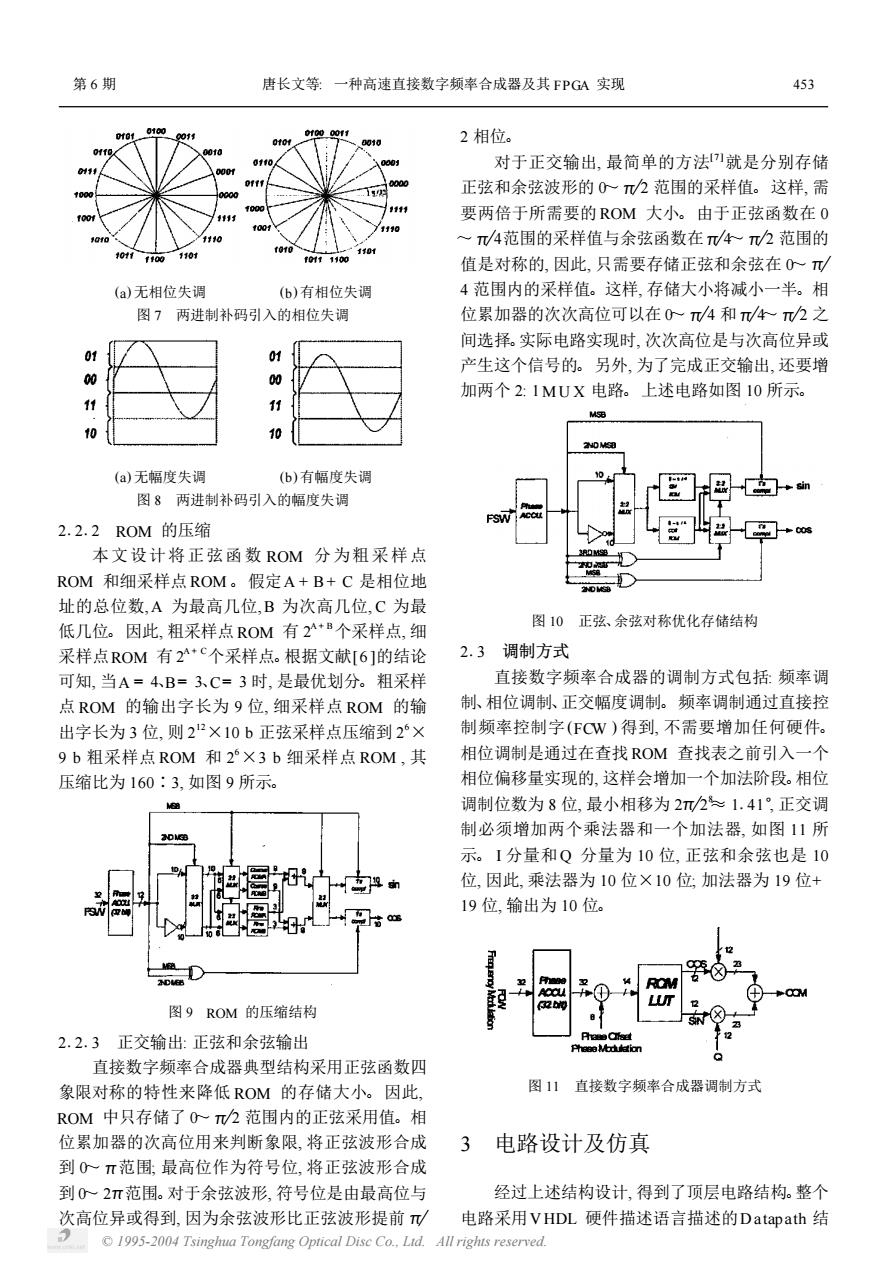

第6期 唐长文等:一种高速直接数字频率合成器及其FPGA实现 453 10 2相位。 01t 对于正交输出,最简单的方法就是分别存储 正弦和余弦波形的0~π2范围的采样值。这样,需 要两倍于所需要的ROM大小。由于正弦函数在0 1190 00 110 一π/4范围的采样值与余弦函数在4~π2范围的 0时ft00 1101 f010 110f t0时11100 值是对称的,因此,只需要存储正弦和余弦在0~π (a)无相位失调 (b)有相位失调 4范围内的采样值。这样,存储大小将减小一半。相 图7两进制补码引入的相位失调 位累加器的次次高位可以在0~π4和π4π2之 间选择。实际电路实现时,次次高位是与次高位异或 01 01 产生这个信号的。另外,为了完成正交输出,还要增 00 00 加两个2:1MUX电路。上述电路如图10所示。 1 10 10 20 (a)无幅度失调 (b)有幅度失调 图8两进制补码引入的幅度失调 2.2.2ROM的压缩 本文设计将正弦函数ROM分为粗采样点 ROM和细采样点ROM。假定A+B+C是相位地 oMB 址的总位数,A为最高几位,B为次高几位,C为最 低几位。因此,粗采样点ROM有2A+B个采样点,细 图10正弦、余弦对称优化存储结构 采样点ROM有24+C个采样点。根据文献[6]的结论 2.3调制方式 可知,当A=4B=3C=3时,是最优划分。粗采样 直接数字频率合成器的调制方式包括:频率调 点ROM的输出字长为9位,细采样点ROM的输 制、相位调制、正交幅度调制。频率调制通过直接控 出字长为3位,则22×10b正弦采样点压缩到2× 制频率控制字(FCW)得到,不需要增加任何硬件。 9b粗采样点ROM和2X3b细采样点ROM,其 相位调制是通过在查找ROM查找表之前引入一个 压缩比为160:3,如图9所示。 相位偏移量实现的,这样会增加一个加法阶段。相位 调制位数为8位,最小相移为2π/2≈1.41°,正交调 制必须增加两个乘法器和一个加法器,如图11所 示。1分量和Q分量为10位,正弦和余弦也是10 古 位,因此,乘法器为10位×10位,加法器为19位+ 19位,输出为10位。 】Aa2 32 ROM ACCU 3双 LUT 图9ROM的压缩结构 2.2.3正交输出:正弦和余弦输出 直接数字频率合成器典型结构采用正弦函数四 象限对称的特性来降低ROM的存储大小。因此, 图11直接数字频率合成器调制方式 ROM中只存储了0~π2范围内的正弦采用值。相 位累加器的次高位用来判断象限,将正弦波形合成 3 电路设计及仿真 到0~π范围,最高位作为符号位,将正弦波形合成 到0~2π范围。对于余弦波形,符号位是由最高位与 经过上述结构设计,得到了顶层电路结构。整个 次高位异或得到,因为余弦波形比正弦波形提前π 电路采用VHDL硬件描述语言描述的Datapath结 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

(a) 无相位失调 (b) 有相位失调 图 7 两进制补码引入的相位失调 (a) 无幅度失调 (b) 有幅度失调 图 8 两进制补码引入的幅度失调 21212 ROM 的压缩 本文设计将正弦函数 ROM 分为粗采样点 ROM 和细采样点 ROM。假定A + B+ C 是相位地 址的总位数, A 为最高几位,B 为次高几位, C 为最 低几位。因此, 粗采样点 ROM 有 2 A + B个采样点, 细 采样点ROM 有 2 A + C个采样点。根据文献[6 ]的结论 可知, 当A = 4、B= 3、C= 3 时, 是最优划分。粗采样 点 ROM 的输出字长为 9 位, 细采样点 ROM 的输 出字长为 3 位, 则 2 12×10 b 正弦采样点压缩到 2 6× 9 b 粗采样点 ROM 和 2 6×3 b 细采样点 ROM , 其 压缩比为 160∶3, 如图 9 所示。 图 9 ROM 的压缩结构 21213 正交输出: 正弦和余弦输出 直接数字频率合成器典型结构采用正弦函数四 象限对称的特性来降低 ROM 的存储大小。因此, ROM 中只存储了 0~ Πö2 范围内的正弦采用值。相 位累加器的次高位用来判断象限, 将正弦波形合成 到 0~ Π范围; 最高位作为符号位, 将正弦波形合成 到 0~ 2Π范围。对于余弦波形, 符号位是由最高位与 次高位异或得到, 因为余弦波形比正弦波形提前 Πö 2 相位。 对于正交输出, 最简单的方法[ 7 ]就是分别存储 正弦和余弦波形的 0~ Πö2 范围的采样值。这样, 需 要两倍于所需要的 ROM 大小。由于正弦函数在 0 ~ Πö4范围的采样值与余弦函数在 Πö4~ Πö2 范围的 值是对称的, 因此, 只需要存储正弦和余弦在 0~ Πö 4 范围内的采样值。这样, 存储大小将减小一半。相 位累加器的次次高位可以在 0~ Πö4 和 Πö4~ Πö2 之 间选择。实际电路实现时, 次次高位是与次高位异或 产生这个信号的。另外, 为了完成正交输出, 还要增 加两个 2: 1 M U X 电路。上述电路如图 10 所示。 图 10 正弦、余弦对称优化存储结构 213 调制方式 直接数字频率合成器的调制方式包括: 频率调 制、相位调制、正交幅度调制。频率调制通过直接控 制频率控制字 (FCW ) 得到, 不需要增加任何硬件。 相位调制是通过在查找 ROM 查找表之前引入一个 相位偏移量实现的, 这样会增加一个加法阶段。相位 调制位数为 8 位, 最小相移为 2Πö2 8≈ 1141°, 正交调 制必须增加两个乘法器和一个加法器, 如图 11 所 示。 I 分量和Q 分量为 10 位, 正弦和余弦也是 10 位, 因此, 乘法器为 10 位×10 位; 加法器为 19 位+ 19 位, 输出为 10 位。 图 11 直接数字频率合成器调制方式 3 电路设计及仿真 经过上述结构设计, 得到了顶层电路结构。整个 电路采用V HDL 硬件描述语言描述的D atapath 结 第 6 期 唐长文等: 一种高速直接数字频率合成器及其 FPGA 实现 453 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

454 唐长文等:一种高速直接数字频率合成器及其FPGA实现 2001年 构,内部引入了4级流水线。正弦采样值ROM,由 XC4010XLPC84A转换器ADV7128、下载电路 于容量比较小,采用组合逻辑生成。综合结果表明, 和电源电路四个部分。其中的数字输出可以输出到 能够达到系统50MHz要求。电路仿真结果如图12 板上的SRAM芯片中,然后上载到计算机进行数字 所示。 信号分析,模拟输出则通过HP示波器测试。 数字信号测试表明,电路实际工作时的结果与 仿真结果完全一致。 5 结论 本文介绍了一种用于QAM调制和解调的高速 图12电路仿真波形图 直接数字频率合成器。对整个系统在结构方面进行 前半部分是频率为6.63MHz的正弦和余弦 了优化:考虑了有限字长效应,利用正弦和余弦的对 波,频率控制字FCW=21F0BD6H,相位控制字 称性,大大降低了ROM的容量,提出了系统的几种 Phase-=00H;后半部分是频率为8.21MHz的正弦 调制方式:频率调制、相位调制和正交幅度调制。整 和余弦波,频率控制字FCW=2A098ACBH,相位控 个系统通过VHDL语言描述,采用X ilinx FPGA硬 制字Phase=-80H。图l3是上述信号的FFT频谱, 件实现,最后,还进行了硬件测试。系统时钟频率为 谐波幅度小于.72B。 50MHz,信号的谐波小于.72dB。输出信号的范围 为DC到25MHz,信号频率步长为0.0116Hz,相 ”4.310 应的转换速度为20ns,建立时间延迟为4个时钟。 参考文献 itlenisllbit ith [1]CMOS 80 MHz 10-bit video DAC ADV 7128 [Z A nalog Devices Data Sheet [2]Tierney J,Rader C M,Gold B.A digital frequency synthesizer [J IEEE Trans A udo Electroacoust, 图13FFT频谱 19711948-57 [3] Sutherland D A,Strauch R A,W harfield SS,et,al 将综合好的edif电路网表文件输入到后端 CMOS/SOS frequency synthesizer LSI circuit for FPGA厂商X ilinx的Foundation软件,进行布局和 pectrum communications [J]IEEE J Sol Sta Circ, 1984:19(8):497-505 布线,生成二进制流文件。其结果如表1所示。 [4] N icho las H T,Sam ueli H.A 150 MHz direct digital frequency synthesizer in 1 25-um CMOS w ith-90dBc 表」硬件综合结果 spurious perfom ance[J]IEEE J Sol Sta Circ,1991; 26(12):1959-1969 硬件芯片 XC4010XLP℃84-3 [5] Vankka,W altari M,Kosunen M,et al A direct 资源 140 CLB digital synthesizer w ith an on-chip DA-converter 等效门数 8318门 [J IEEE J Sol Sta Circ,1998;33(2):218-227 [6]N icholas H T,SamueliH,Km B.The opti ization 最高工作频率 54.514MHz of direct digital frequency synthesizer perfo m ance in the presence of finite word length effects [A 1 Proc 43rd Annu Frequency Control Symp [C 1988 357- 4 电路测试 363 [7]Tan K,Samueli H.A 200 MHz quadrature digital synthesizer /m ixer in Q 8-m CMOS [J IEEE J Sol 测试电路板主要包括:FPGA芯片 Sta Circ,.1995:30(3):193-200 作者简介:唐长文(1977一),男,1999年毕业于复旦大学,获电路与系 统专业学士学位,现为复旦大学专用集成电路与系统国家重点实验室硕 士研究生,研究方向为专用集成电路设计、数字信号处理系统设计、数字 信号算法FPGA结构实现等,目前正在研制单片多制式数字视频编码器 系统。 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

构, 内部引入了 4 级流水线。正弦采样值 ROM , 由 于容量比较小, 采用组合逻辑生成。综合结果表明, 能够达到系统 50M H z 要求。电路仿真结果如图 12 所示。 图 12 电路仿真波形图 前半部分是频率为 6163 M H z 的正弦和余弦 波, 频率控制字 FCW = 21F07BD 6H , 相位控制字 Phase= 00H; 后半部分是频率为 8121 M H z 的正弦 和余弦波, 频率控制字 FCW = 2A 098A CBH , 相位控 制字 Phase= 80 H。图 13 是上述信号的 FFT 频谱, 谐波幅度小于- 72 dB。 图 13 FFT 频谱 将综合好的 edif 电路网表文件输入到后端 FPGA 厂商X ilinx 的 Foundation 软件, 进行布局和 布线, 生成二进制流文件。其结果如表 1 所示。 表 1 硬件综合结果 硬件芯片 XC4010XL PC8423 资源 140 CLB 等效门数 8318 门 最高工作频率 541514M H z 4 电路测试 测 试 电 路 板 主 要 包 括: FPGA 芯 片 XC4010XL PC84、A öD 转换器ADV 7128、下载电路 和电源电路四个部分。其中的数字输出可以输出到 板上的 SRAM 芯片中, 然后上载到计算机进行数字 信号分析; 模拟输出则通过 H P 示波器测试。 数字信号测试表明, 电路实际工作时的结果与 仿真结果完全一致。 5 结 论 本文介绍了一种用于QAM 调制和解调的高速 直接数字频率合成器。对整个系统在结构方面进行 了优化: 考虑了有限字长效应; 利用正弦和余弦的对 称性, 大大降低了 ROM 的容量; 提出了系统的几种 调制方式: 频率调制、相位调制和正交幅度调制。整 个系统通过V HDL 语言描述, 采用X ilinx FPGA 硬 件实现, 最后, 还进行了硬件测试。系统时钟频率为 50M H z, 信号的谐波小于- 72 dB。输出信号的范围 为DC 到 25 M H z, 信号频率步长为 010116 H z, 相 应的转换速度为 20 n s, 建立时间延迟为 4 个时钟。 参 考 文 献: [ 1 ] CM O S 80 M H z, 102bit video DA C ADV 7128 [ Z ]. A nalog D evices D ata Sheet. [ 2 ] T ierney J, R ader C M , Go ld B. A digital frequency synthesizer [J ]. IEEE T rans A udio E lectroacoust, 1971; 19: 48257. [ 3 ] Sutherland D A , Strauch R A , W harfield S S, et, al. CM O SöSO S frequency synthesizer L S I circuit fo r spectrum comm unications [J ]. IEEE J So l Sta C irc, 1984; 19 (8): 4972505. [4 ] N icho las H T , Sam ueli H. A 150 M H z direct digital frequency synthesizer in 1. 252Λm CM O S w ith- 90dBc spurious perfo rm ance[J ]. IEEE J So l Sta C irc, 1991; 26 (12): 195921969. [ 5 ] V ankka, W altari M , Ko sunen M , et al. A direct digital synthesizer w ith an on2ch ip DöA 2converter [J ]. IEEE J So l Sta C irc, 1998; 33 (2): 2182227. [ 6 ] N icho las H T , Sam ueli H , K im B. T he op tim ization of direct digital frequency synthesizer perfo rm ance in the p resence of finite w o rd length effects [A ]. P roc 43rd A nnu F requency Contro l Symp [C ]. 1988. 3572 363. [ 7 ] T an K, Sam ueli H. A 200 M H z quadrature digital synthesizer öm ixer in 0. 82Λm CM O S [J ]. IEEE J So l Sta C irc, 1995; 30 (3): 1932200. 作者简介: 唐长文(1977—) , 男, 1999 年毕业于复旦大学, 获电路与系 统专业学士学位, 现为复旦大学专用集成电路与系统国家重点实验室硕 士研究生, 研究方向为专用集成电路设计、数字信号处理系统设计、数字 信号算法 FPGA 结构实现等, 目前正在研制单片多制式数字视频编码器 系统。 454 唐长文等: 一种高速直接数字频率合成器及其 FPGA 实现 2001 年 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved