学校代码:10246 学号:021021061 復旦大婴 博士学位论文 射频集成电路片上电感的分析与优化设计 Analysis and Optimum Design of On-Chip Inductor for RF ICs 院 系: 微电子学系 专 业: 微电子学与固体电子学 姓 名: 菅洪彦 指导教师: 闵昊教授 完成日期: 2005年4月20日

学校代码: 10246 学 号: 021021061 博 士 学 位 论 文 射频集成电路片上电感的分析与优化设计 Analysis and Optimum Design of On-Chip Inductor for RF ICs 院 系: 微电子学系 专 业: 微电子学与固体电子学 姓 名: 菅洪彦 指 导 教 师: 闵昊 教授 完 成 日 期: 2005 年 4 月 20 日

Analysis and Optimum Design of On-Chip Inductor for RF ICs by Hongyan Jian B.S.(Shaanxi Normal University,Xi'an)1992 M.S.(Ocean University of China,Qingdao)1996 A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Microelectronics in the GRADUATE DIVISION of the FUDAN UNIVERSITY,SHANGHAI Committee in charge: Professor Hao Min Professor Zhiliang Hong Professor Junyan Ren Professor Lianxing Yang Spring 2005 Copyright Spring 2005,by Hongyan Jian ALL RIGHTS RESERVED

Analysis and Optimum Design of On-Chip Inductor for RF ICs by Hongyan Jian B.S. (Shaanxi Normal University, Xi’an) 1992 M.S. (Ocean University of China, Qingdao) 1996 A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Microelectronics in the GRADUATE DIVISION of the FUDAN UNIVERSITY, SHANGHAI Committee in charge: Professor Hao Min Professor Zhiliang Hong Professor Junyan Ren Professor Lianxing Yang Spring 2005 Copyright Spring 2005, by Hongyan Jian ALL RIGHTS RESERVED

目 录 第一章引言 1.1市场需求和技术推动1 1.2电感在射频集成电路中的作用2 1.3片上电感研究进展和存在的问题2 1.3.1集成电感3 1.3.2金属互连线电感的研究现状4 1.3.3金属互连线电感研究存在的问题5 1.4论文的组织结构6 参考文献7 第二章片上电感的物理模型与特性分析 2.1串连电感10 2.1.1自感10 2.1.2互感11 2.1.3电感值的计算12 2.1.4电感值与面积成本13 2.2片上电感的实现与物理特性13 2.2.1金属互连线电感的结构13 2.2.2寄生与损耗分析15 2.2.3品质因数和自谐振频率16 2.3电感寄生电容模型17 2.3.1分布电容模型17 2.3.1.1假设和定义18 2.3.1.2电感贮存电能和寄生电容20 2.3.2平面螺旋电感的寄生电容定量计算22 2.3.3垂直螺线管电感的寄生电容定量计算26 2.3.4平板电容计算33 2.4串联电阻分析33 2.4.1直流电阻34 2.4.2趋肤效应电阻34 2.4.2.1趋肤效应35 2.4.2.2趋肤效应电阻37 2.4.3邻近效应电阻40

i 目 录 第一章 引言 1.1市场需求和技术推动 1 1.2电感在射频集成电路中的作用 2 1.3 片上电感研究进展和存在的问题 2 1.3.1集成电感 3 1.3.2 金属互连线电感的研究现状 4 1.3.3 金属互连线电感研究存在的问题 5 1.4 论文的组织结构 6 参考文献 7 第二章 片上电感的物理模型与特性分析 2.1 串连电感 10 2.1.1 自感 10 2.1.2 互感 11 2.1.3 电感值的计算 12 2.1.4 电感值与面积成本 13 2.2 片上电感的实现与物理特性 13 2.2.1 金属互连线电感的结构 13 2.2.2 寄生与损耗分析 15 2.2.3 品质因数和自谐振频率 16 2.3 电感寄生电容模型 17 2.3.1 分布电容模型 17 2.3.1.1 假设和定义 18 2.3.1.2 电感贮存电能和寄生电容 20 2.3.2 平面螺旋电感的寄生电容定量计算 22 2.3.3 垂直螺线管电感的寄生电容定量计算 26 2.3.4 平板电容计算 33 2.4 串联电阻分析 33 2.4.1 直流电阻 34 2.4.2 趋肤效应电阻 34 2.4.2.1 趋肤效应 35 2.4.2.2 趋肤效应电阻 37 2.4.3 邻近效应电阻 40

2.5衬底物理模型和损耗分析42 2.5.1衬底的变压器效应43 2.5.1.1衬底磁能损耗物理模型43 2.5.1.2衬底磁能损耗数学解析43 2.5.2衬底电容耦合损耗48 2.5.2.1衬底电容耦合损耗物理模型48 2.5.2.2衬底电容耦合损耗数学解析49 2.5.3衬底耦合50 2.5.4衬底温度效应50 2.6小结51 参考文献51 第三章片上电感的优化设计 3.1增大耦合系数的方法55 3.1.1增大同平面线圈耦合系数的方法55 3.1.2增大垂直串连耦合系数的方法57 3.1.3垂直螺线管电感优化设计58 3.2寄生电容降低方法60 3.2.1结构上降低线圈与衬底之间寄生电容的方法60 3.2.2结构上降低线圈与衬底之间寄生电容的方法62 3.2.3改进工艺降低电感寄生电容63 3.3降低串联电阻的方法64 3.3.1降低直流电阻方法64 3.3.1.1结构上降低直流电阻64 3.3.1.2工艺上降低直流电阻65 3.3.2电流拥挤效应抑制66 3.3.2.1趋肤效应抑制66 3.3.2.2邻近效应抑制69 3.3.2.3多电流路径抑制电流拥挤效应的版图优化设计方法72 3.4衬底的损耗抑制75 3.4.1衬底涡流损耗的抑制方法75 3.4.2降低衬底电容耦合损耗的方法76 3.4.3衬底耦合的降低78 3.5电感应用电路优化设计方法79 3.5.1高性能片上电感的标准79

ii 2.5 衬底物理模型和损耗分析 42 2.5.1 衬底的变压器效应 43 2.5.1.1 衬底磁能损耗物理模型 43 2.5.1.2 衬底磁能损耗数学解析 43 2.5.2 衬底电容耦合损耗 48 2.5.2.1 衬底电容耦合损耗物理模型 48 2.5.2.2 衬底电容耦合损耗数学解析 49 2.5.3 衬底耦合 50 2.5.4 衬底温度效应 50 2.6 小结 51 参考文献 51 第三章 片上电感的优化设计 3.1 增大耦合系数的方法 55 3.1.1 增大同平面线圈耦合系数的方法 55 3.1.2 增大垂直串连耦合系数的方法 57 3.1.3 垂直螺线管电感优化设计 58 3.2 寄生电容降低方法 60 3.2.1 结构上降低线圈与衬底之间寄生电容的方法 60 3.2.2 结构上降低线圈与衬底之间寄生电容的方法 62 3.2.3 改进工艺降低电感寄生电容 63 3.3 降低串联电阻的方法 64 3.3.1 降低直流电阻方法 64 3.3.1.1 结构上降低直流电阻 64 3.3.1.2 工艺上降低直流电阻 65 3.3.2 电流拥挤效应抑制 66 3.3.2.1 趋肤效应抑制 66 3.3.2.2 邻近效应抑制 69 3.3.2.3 多电流路径抑制电流拥挤效应的版图优化设计方法 72 3.4 衬底的损耗抑制 75 3.4.1 衬底涡流损耗的抑制方法 75 3.4.2 降低衬底电容耦合损耗的方法 76 3.4.3 衬底耦合的降低 78 3.5 电感应用电路优化设计方法 79 3.5.1 高性能片上电感的标准 79

3.5.2压控电感自调谐振荡器80 3.5.3pn结衬底隔离中心频率偏差校正82 3.5.4金属地屏蔽83 3.6小结83 参考文献84 第四章 测试与分析 4.1在片测试和去嵌入88 4.1.1地屏蔽的开路通路去嵌入结构89 4.1.2可缩放的开路通路去嵌入方法91 4.2测试分析93 4.2.1流片测试93 4.2.2平面螺旋和螺线管电感94 4.2.3差分和单端电感97 4.2.4结构上降低差分电感临近线圈寄生电容的方法99 4.2.5电感串连电阻降低方法100 4.2.5.1结构上降低直流电阻100 4.2.5.2多电流路径电感101 4.2.6降低衬底效应方法的验证106 4.2.6.1pn结抑制衬底高频电流107 4.2.6.2各种地屏蔽比对107 4.2.6.3不同测试功率下的衬底损耗109 4.3小结110 参考文献111 第五章 结论 5.1总结112 5.2展望113 附录一趋肤深度公式推导115 附录二两个平行线圈的耦合系数118 附录三两种去嵌入方法119 附录四双端口网络120 致谢122

iii 3.5.2 压控电感自调谐振荡器 80 3.5.3 pn结衬底隔离中心频率偏差校正 82 3.5.4 金属地屏蔽 83 3.6 小结 83 参考文献 84 第四章 测试与分析 4.1 在片测试和去嵌入 88 4.1.1 地屏蔽的开路通路去嵌入结构 89 4.1.2 可缩放的开路通路去嵌入方法 91 4.2 测试分析 93 4.2.1 流片测试 93 4.2.2 平面螺旋和螺线管电感 94 4.2.3 差分和单端电感 97 4.2.4 结构上降低差分电感临近线圈寄生电容的方法 99 4.2.5 电感串连电阻降低方法 100 4.2.5.1 结构上降低直流电阻 100 4.2.5.2 多电流路径电感 101 4.2.6 降低衬底效应方法的验证 106 4.2.6.1 pn结抑制衬底高频电流 107 4.2.6.2 各种地屏蔽比对 107 4.2.6.3 不同测试功率下的衬底损耗 109 4.3 小结 110 参考文献 111 第五章 结论 5.1 总结 112 5.2 展望 113 附录一 趋肤深度公式推导 115 附录二 两个平行线圈的耦合系数 118 附录三 两种去嵌入方法 119 附录四 双端口网络 120 致谢 122

摘 要 无线通信的迅猛发展激发了射频收发器设计的热潮。片上电感是高性能压控振荡 器(VCO)、低噪声放大器和无源滤波器等集成电路模块的重要元件。片上电感品质 因数低,占据较大的芯片面积是需要解决的两个主要问题。 近些年,大量的片上电感研究成果不断涌现,但是对于片上电感的性能局限以及 品质因数(Q)优化过程的基本理解还是不充分的。建立在数值拟合基础上的大部分 电感模型不能给电感的优化设计提供理论指导。本论文建立了包含电磁现象以及对电 感性能有重要影响的寄生电阻和寄生电容的物理模型。在此基础上,分别从集成电路 设计和工艺实现的角度提出了电感的优化方法。研究表明,在不改变工艺的前提下, 利用一些优化技术可以提高电感的性能。采用0.35um的4层金属互连线成功实现了优 化的圆形电感。试验结果证明了理论的精度,验证了优化方法的有效性。 以线圈耦合系数和电感分布电容模型为基础,设计优化了平面螺旋电感和叠层电 感。在相近的芯片面积上,实现的叠层电感值为9.9nH,平面螺旋电感只有1.3H。而 要实现1H电感,4层串连结构电感的面积是平面螺旋电感的四分之一。金属3和金属4 并联,再与并联的金属1和金属2串连,该结构电感最大品质因数(Qmx)是相同电感 值的金属3与金属4并联平面螺旋电感Qmax的210%。 电磁理论表明,小面积金属具有较弱的趋肤效应:金属线宽与间距之比越小,电 感的邻近效应越小。因此,同圈电感金属被分成每股电阻相等且并联的多股,使得最 大的品质因数提高了40%。 使用标准的CMOS工艺,在电感下面的n阱上进行p扩散,形成水平和垂直的双pn 结。将p扩散层接地来阻止电感电场到达电感下面的衬底。增大阱的电压,横向和 纵向的p结的耗尽层加厚,电感的品质因数提高了19%。这个现象证明了电感衬底电 场和磁场损耗物理模型的有效性。 关键词:片上电感品质因数自谐振频率平面螺旋电感叠层电感串联电 阻寄生电容衬底损耗优化设计在片测试 iv

iv 摘 要 无线通信的迅猛发展激发了射频收发器设计的热潮。片上电感是高性能压控振荡 器(VCO)、低噪声放大器和无源滤波器等集成电路模块的重要元件。片上电感品质 因数低,占据较大的芯片面积是需要解决的两个主要问题。 近些年,大量的片上电感研究成果不断涌现,但是对于片上电感的性能局限以及 品质因数(Q)优化过程的基本理解还是不充分的。建立在数值拟合基础上的大部分 电感模型不能给电感的优化设计提供理论指导。本论文建立了包含电磁现象以及对电 感性能有重要影响的寄生电阻和寄生电容的物理模型。在此基础上,分别从集成电路 设计和工艺实现的角度提出了电感的优化方法。研究表明,在不改变工艺的前提下, 利用一些优化技术可以提高电感的性能。采用0.35μm的4层金属互连线成功实现了优 化的圆形电感。试验结果证明了理论的精度,验证了优化方法的有效性。 以线圈耦合系数和电感分布电容模型为基础,设计优化了平面螺旋电感和叠层电 感。在相近的芯片面积上,实现的叠层电感值为9.9nH,平面螺旋电感只有1.3nH。而 要实现1nH电感,4层串连结构电感的面积是平面螺旋电感的四分之一。金属3和金属4 并联,再与并联的金属1和金属2串连,该结构电感最大品质因数(Qmax)是相同电感 值的金属3与金属4并联平面螺旋电感Qmax 的210%。 电磁理论表明,小面积金属具有较弱的趋肤效应;金属线宽与间距之比越小,电 感的邻近效应越小。因此,同圈电感金属被分成每股电阻相等且并联的多股,使得最 大的品质因数提高了40%。 使用标准的CMOS工艺,在电感下面的n阱上进行p +扩散,形成水平和垂直的双pn 结。将p + 扩散层接地来阻止电感电场到达电感下面的衬底。增大n阱的电压,横向和 纵向的pn结的耗尽层加厚,电感的品质因数提高了19%。这个现象证明了电感衬底电 场和磁场损耗物理模型的有效性。 关键词:片上电感 品质因数 自谐振频率 平面螺旋电感 叠层电感 串联电 阻 寄生电容 衬底损耗 优化设计 在片测试

Analysis and Optimum Design of On-Chip Inductor for RF ICs Abstract The wireless communication revolution has spawned a revival of interest in the design and optimization of radio transceivers.On-chip inductors are important, performance-limiting,large die area components in monolithic radio frequency (RF) circuits,such as voltage-controlled oscillators (VCO),low-noise amplifiers and passive-element filters. Although numerous results of on-chip inductors have been reported,the basic understanding of performance limitations and the procedures for optimizing the quality factor(Q)are insufficient.Most published inductor models rely on numerical techniques, which are not intuitive enough to provide the insight needed in a design process.This dissertation presents physical models that address the electromagnetic phenomena and parasitics important to the behavior of on-chip inductors.Guidelines for the optimum inductor design are proposed from the point of view of the integrated circuits(ICs)design and technology. Inductors have been fabricated in a 0.35um two-poly four-metal CMOS technology for validating the some proposed techniques and theories without altering technology to improve the Q of the inductor and circuits in this dissertation. Based on the guidelines of the distributed capacitance mode and coupling coefficient formula,the stacked and planar inductors are designed.Using the close die area of the planar inductor with 1.34nH,the stacked inductor realizes 9.9nH inductance.Realizing InH inductance,the die area of the four-layer-interconnect series inductor only is the quarter of that of the planar spiral inductor.The maximum Q of the inductor that designed by metal 3//metal 4 in series with metal 1//metal 2 is 110%greater than that of the planar inductor with same inductance. The electromagnetic theory indicates that the metal with small cross-area has the weak skin effect and the inductors with the less ratio the turn width of the space between turns have weak proximity effect.Thus,the one turn metal of the inductor is divided into multi-shunt tracks with the same impedance,and then the maximum Q has 40% improvement. Dual pn junctions in lateral and vertical directions are formed by diffusing the p on the patterned n-well in standard CMOS technology,which are inserted under the inductor. The p"-diffusion layer is grounded to shield the substrate from the electric field of inductor, the width of the depletion regions of the lateral and vertical pn junctions are changed by increasing the voltage applied to the n-wells,and then quality factor is improved by 19%. This phenomenon validates the physical models of the electric field and magnetic field losses of the on-chip inductors in the substrate. Key Wards:On-chip inductor,quality factor,self-resonant frequency,planar spirals,stacked inductor,series resistance,parasitical capacitance,substrate loss,optimum design,on-wafer measurement

v Analysis and Optimum Design of On-Chip Inductor for RF ICs Abstract The wireless communication revolution has spawned a revival of interest in the design and optimization of radio transceivers. On-chip inductors are important, performance-limiting, large die area components in monolithic radio frequency (RF) circuits, such as voltage-controlled oscillators (VCO), low-noise amplifiers and passive-element filters. Although numerous results of on-chip inductors have been reported, the basic understanding of performance limitations and the procedures for optimizing the quality factor (Q) are insufficient. Most published inductor models rely on numerical techniques, which are not intuitive enough to provide the insight needed in a design process. This dissertation presents physical models that address the electromagnetic phenomena and parasitics important to the behavior of on-chip inductors. Guidelines for the optimum inductor design are proposed from the point of view of the integrated circuits (ICs) design and technology. Inductors have been fabricated in a 0.35μm two-poly four-metal CMOS technology for validating the some proposed techniques and theories without altering technology to improve the Q of the inductor and circuits in this dissertation. Based on the guidelines of the distributed capacitance mode and coupling coefficient formula, the stacked and planar inductors are designed. Using the close die area of the planar inductor with 1.34nH, the stacked inductor realizes 9.9nH inductance. Realizing 1nH inductance, the die area of the four-layer-interconnect series inductor only is the quarter of that of the planar spiral inductor. The maximum Q of the inductor that designed by metal 3//metal 4 in series with metal 1//metal 2 is 110% greater than that of the planar inductor with same inductance. The electromagnetic theory indicates that the metal with small cross-area has the weak skin effect and the inductors with the less ratio the turn width of the space between turns have weak proximity effect. Thus, the one turn metal of the inductor is divided into multi-shunt tracks with the same impedance, and then the maximum Q has 40% improvement. Dual pn junctions in lateral and vertical directions are formed by diffusing the p+ on the patterned n-well in standard CMOS technology, which are inserted under the inductor. The p+ -diffusion layer is grounded to shield the substrate from the electric field of inductor, the width of the depletion regions of the lateral and vertical pn junctions are changed by increasing the voltage applied to the n-wells, and then quality factor is improved by 19%. This phenomenon validates the physical models of the electric field and magnetic field losses of the on-chip inductors in the substrate. Key Wards: On-chip inductor, quality factor, self-resonant frequency, planar spirals, stacked inductor, series resistance, parasitical capacitance, substrate loss, optimum design, on-wafer measurement

第一章 引言 第一章引言 本章论述了研究片上电感的动机、片上电感的作用以及当前研究进展和存在的问 题,最后概述了本文的组织结构。 1.1市场需求和技术推动 在过去十几年里,寻呼机、无绳电话、模拟及数字蜂窝电话等个人通信系统以及 数字电视、广播及全球定位导航系统得到了迅猛地发展,这些消费电子产品的成功依 赖它们的成本、电池的使用寿命、功能和重量。集成射频模块和基带数字信号处理单 元在一个单硅片上可以满足上述要求。无源元件特别是电感在射频前端系统中具有重 要作用,它们的集成引起了学术界和工业界广泛的关注。 当前的收发器设计通常采用双极工艺和BiCMOS工艺制造低噪声放大器、混频器 和压控振荡器:采用砷化镓(GAs)或双极工艺制造功率放大器:采用CMOS工艺制造 基带信号处理芯片。目前,在印刷电路板(PCB)上还在大量地使用薄膜技术或分立 形式的无源元件。为了增加集成度,不同的电路模块和元件采用同一种工艺,制作在 相同的衬底上。随着工艺的进步,CMOS工艺晶体管的截止频率()变得越来越高。 与GaAs工艺相比,CMOS工艺在价格、功耗方面都占有显著的优势。可以同时在CMOS 工艺中集成模拟和数字电路,因此可以实现更高程度的集成。这使CMOS集成电路 在较低GHz率范围的应用日益广泛。业界的目标是使得所有的收发器部分,无论是 数字还是模拟、射频都采用标准CMOS工艺实现。单芯片收发器是研究的目标和重点, 在学术上和经济上都具有较高的价值。 芯片的单片集成具有以下优点: 成本:在收发器前端部分,在PCB上的主要成分是无源元件。虽然在整个电路中 电感、电阻、电容占一个很小的比例(10%),但是整体的无源元件价值超过了电路总 价值的三分之一。最重要的是,随着中间级LC匹配网络的集成,单独的电路模块更 加容易在CMOS工艺上制造,进而大幅度下降IC的封装和试验费用。 功耗:芯片的单片集成可以节能。管脚、引线、IC封装、PCB上的连线以及分立 封装会引起较大的寄生电感和电容。当信号在PCB上的元件间传输时,附加的能量不 得不消耗在驱动这些附加的寄生电感和电容上。而单片集成就可以避免这些能量的消 耗。 面积:在今天的系统中,分立的无源元件占据了大部分PCB板的面积。微型的便 携式系统需要较小的固定电阻电感电容(RLC)电路面积。由于需要很大的面积用于 焊接附件和通孔,通过先进的封装技术节省的PCB面积变得不再显著。集成RLC元 件在芯片上是更加有效的降低PCB面积方法

第一章 引言 1 第一章 引言 本章论述了研究片上电感的动机、片上电感的作用以及当前研究进展和存在的问 题,最后概述了本文的组织结构。 1.1 市场需求和技术推动 在过去十几年里,寻呼机、无绳电话、模拟及数字蜂窝电话等个人通信系统以及 数字电视、广播及全球定位导航系统得到了迅猛地发展,这些消费电子产品的成功依 赖它们的成本、电池的使用寿命、功能和重量。集成射频模块和基带数字信号处理单 元在一个单硅片上可以满足上述要求。无源元件特别是电感在射频前端系统中具有重 要作用,它们的集成引起了学术界和工业界广泛的关注。 当前的收发器设计通常采用双极工艺和 BiCMOS 工艺制造低噪声放大器、混频器 和压控振荡器;采用砷化镓(GaAs)或双极工艺制造功率放大器;采用 CMOS 工艺制造 基带信号处理芯片。目前,在印刷电路板(PCB)上还在大量地使用薄膜技术或分立 形式的无源元件。为了增加集成度,不同的电路模块和元件采用同一种工艺,制作在 相同的衬底上。随着工艺的进步,CMOS 工艺晶体管的截止频率(fT)变得越来越高。 与GaAs工艺相比,CMOS工艺在价格、功耗方面都占有显著的优势。可以同时在CMOS 工艺中集成模拟和数字电路,因此可以实现更高程度的集成。 这使 CMOS 集成电路 在较低 GHz 频率范围的应用日益广泛。业界的目标是使得所有的收发器部分,无论是 数字还是模拟、射频都采用标准 CMOS 工艺实现。单芯片收发器是研究的目标和重点, 在学术上和经济上都具有较高的价值。 芯片的单片集成具有以下优点[1.1]: 成本:在收发器前端部分,在 PCB 上的主要成分是无源元件。虽然在整个电路中 电感、电阻、电容占一个很小的比例(10%),但是整体的无源元件价值超过了电路总 价值的三分之一。最重要的是,随着中间级 LC 匹配网络的集成,单独的电路模块更 加容易在 CMOS 工艺上制造,进而大幅度下降 IC 的封装和试验费用。 功耗:芯片的单片集成可以节能。管脚、引线、IC 封装、PCB 上的连线以及分立 封装会引起较大的寄生电感和电容。当信号在 PCB 上的元件间传输时,附加的能量不 得不消耗在驱动这些附加的寄生电感和电容上。而单片集成就可以避免这些能量的消 耗。 面积:在今天的系统中,分立的无源元件占据了大部分 PCB 板的面积。微型的便 携式系统需要较小的固定电阻电感电容(RLC)电路面积。由于需要很大的面积用于 焊接附件和通孔,通过先进的封装技术节省的 PCB 面积变得不再显著。集成 RLC 元 件在芯片上是更加有效的降低 PCB 面积方法

第一章引言 可靠性:单片集成减少了芯片与外部元件的焊接,进而提高了系统的可靠性。 精度:大部分无线通信的电路工作频率在0.8-2.5GHz之间,在这个频率,电路使 用的典型电感值为1-25H。用分立元件很难实现小值电感。表面贴片电感元件值的误 差一般在2%一25%,由于封装的寄生效应,使得在10H以下的元件值误差变得更大。 由于IC工艺的严格控制特性,片上电感能够提供了很好的精度和重复性。 设计的灵活性:信号在片上的传递避免了片外阻抗匹配的50Ω阻抗要求,而无源 元件的集成使得阻抗匹的设计配更加灵活。 试验:更多元件的集成将简化和减少电路测试,进而降低成本。 芯片的单片集成具有降低成本、功耗、面积、实验费用,增加可靠性、精度高和 设计灵活性的好处。因此,在经济利益的拉动下,技术发展的推动下,集成电感的研 究成为射频集成电路设计的一个热点课题。 1.2电感在射频集成电路中的作用 因为电感是磁能储能元件,与电能存储元件配合使用可以实现很多功能:电感具 有低通高阻特性,可以在降低电源电压、滤波等电路发挥重要作用,所以电感是射频 集成电路不可缺少的元件。 便携无线通信装置需要低成本、低电压、低功耗、低噪声、高频和低失真。没有 电感,这些要求在许多情况下是不能够得到满意解决的。 多数蜂窝通讯设备的工作频率位于0.8到2.5GHz范围内,在这样高的频率上,为 了得到射频系统中模块电路之间的最大能量传递,必须在它们之间插入阻抗匹配网络。 当两部分电路的阻抗复共扼时,能量传输达到最大。电感是阻抗变换电路的一部分, 例如L匹配和π匹配网络的一部分。T.H.L的书为阻抗匹配的设计提出了详细的指 导原则12。在设计诸如低噪声放大器(LNA)3-14、混频器1.s16和放大器.7-18等 电路模块时,阻抗匹配使电路具有较小的噪声、最大的增益、最小的反射和优化的效 率。 对于GHz以上的振荡器,采用环振电路很难实现低的相位噪声,高品质因数的电 感在实现LC调谐回路的压控振荡器(VCO)中也是必不可少的:VCO的相位噪声主 要决定于LC调谐回路的品质因数9110。一般而言,使用电感的电路都是窄带电路, 实际上,片上电感可以用于拓展频带2,1山。镜像滤波器是实现 工艺单片集 成超外差接收器的瓶颈.2),高质量的电感对于实现镜像滤波器是非常有用的。而收 发器的切换开关也随着片上电感的使用得到解决1.1]。 1.3片上电感研究进展和存在的问题 片上电感分为有源电感、金属互连线电感、键合线电感以及半有源电感。其中金 2

第一章 引言 2 可靠性:单片集成减少了芯片与外部元件的焊接,进而提高了系统的可靠性。 精度:大部分无线通信的电路工作频率在 0.8-2.5GHz 之间,在这个频率,电路使 用的典型电感值为 1-25nH。用分立元件很难实现小值电感。表面贴片电感元件值的误 差一般在 2%-25%,由于封装的寄生效应,使得在 10nH 以下的元件值误差变得更大。 由于 IC 工艺的严格控制特性,片上电感能够提供了很好的精度和重复性。 设计的灵活性:信号在片上的传递避免了片外阻抗匹配的 50Ω阻抗要求,而无源 元件的集成使得阻抗匹的设计配更加灵活。 试验:更多元件的集成将简化和减少电路测试,进而降低成本。 芯片的单片集成具有降低成本、功耗、面积、实验费用,增加可靠性、精度高和 设计灵活性的好处。因此,在经济利益的拉动下,技术发展的推动下,集成电感的研 究成为射频集成电路设计的一个热点课题。 1.2 电感在射频集成电路中的作用 因为电感是磁能储能元件,与电能存储元件配合使用可以实现很多功能;电感具 有低通高阻特性,可以在降低电源电压、滤波等电路发挥重要作用,所以电感是射频 集成电路不可缺少的元件。 便携无线通信装置需要低成本、低电压、低功耗、低噪声、高频和低失真。没有 电感,这些要求在许多情况下是不能够得到满意解决的。 多数蜂窝通讯设备的工作频率位于 0.8 到 2.5GHz 范围内,在这样高的频率上,为 了得到射频系统中模块电路之间的最大能量传递,必须在它们之间插入阻抗匹配网络。 当两部分电路的阻抗复共扼时,能量传输达到最大。电感是阻抗变换电路的一部分, 例如 L 匹配和π匹配网络的一部分。T.H. Lee 的书为阻抗匹配的设计提出了详细的指 导原则 [1.2]。在设计诸如低噪声放大器(LNA)[1.3-1.4]、混频器[1.5-1.6]和放大器[1.7-1.8]等 电路模块时,阻抗匹配使电路具有较小的噪声、最大的增益、最小的反射和优化的效 率。 对于 GHz 以上的振荡器,采用环振电路很难实现低的相位噪声,高品质因数的电 感在实现 LC 调谐回路的压控振荡器(VCO)中也是必不可少的;VCO 的相位噪声主 要决定于 LC 调谐回路的品质因数[1.9-1.10]。一般而言,使用电感的电路都是窄带电路, 实际上,片上电感可以用于拓展频带[1.2,1.11]。镜像滤波器是实现 工艺单片集 成超外差接收器的瓶颈[1.12],高质量的电感对于实现镜像滤波器是非常有用的。而收 发器的切换开关也随着片上电感的使用得到解决[1.13]。 1.3 片上电感研究进展和存在的问题 片上电感分为有源电感、金属互连线电感、键合线电感以及半有源电感。其中金

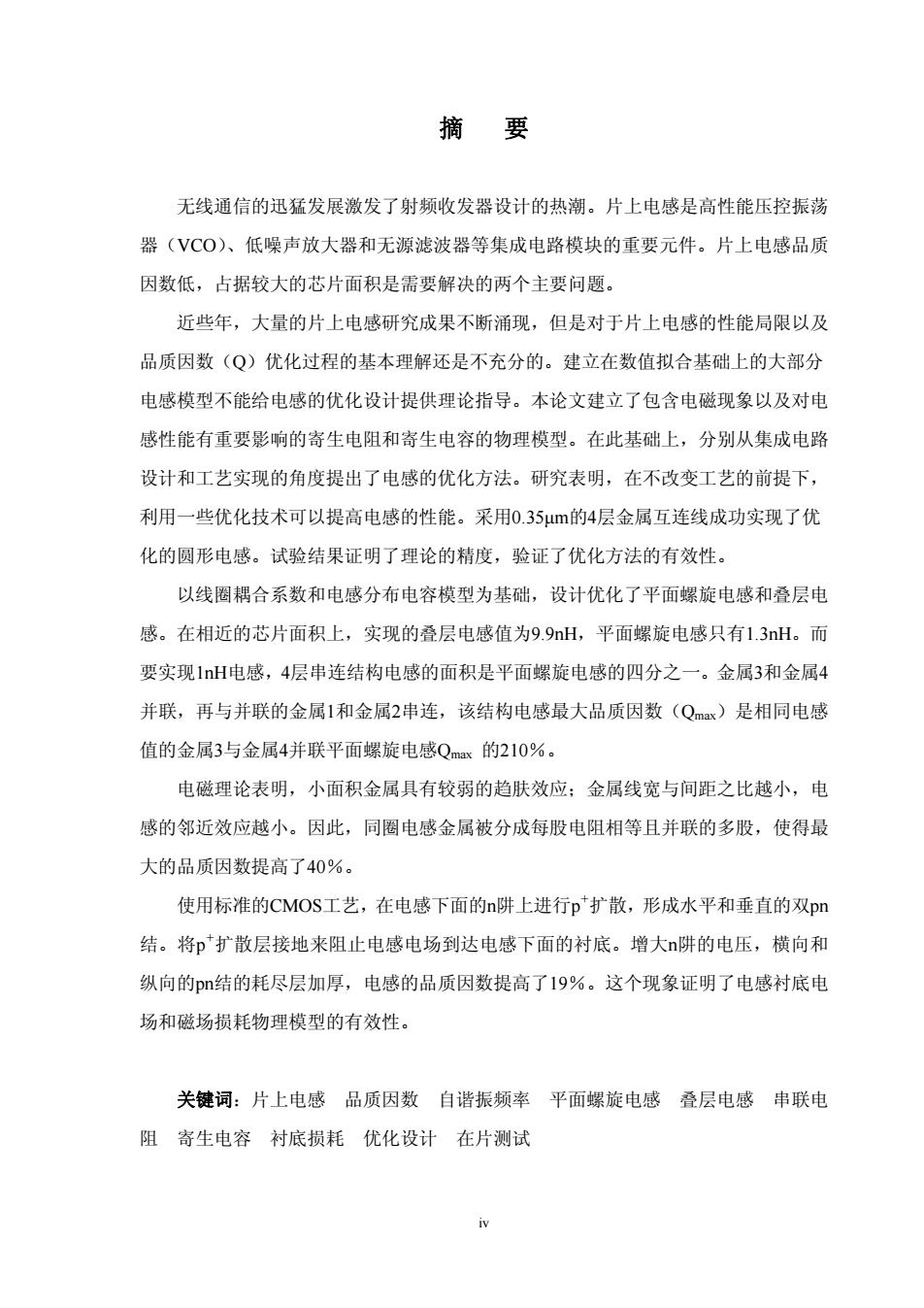

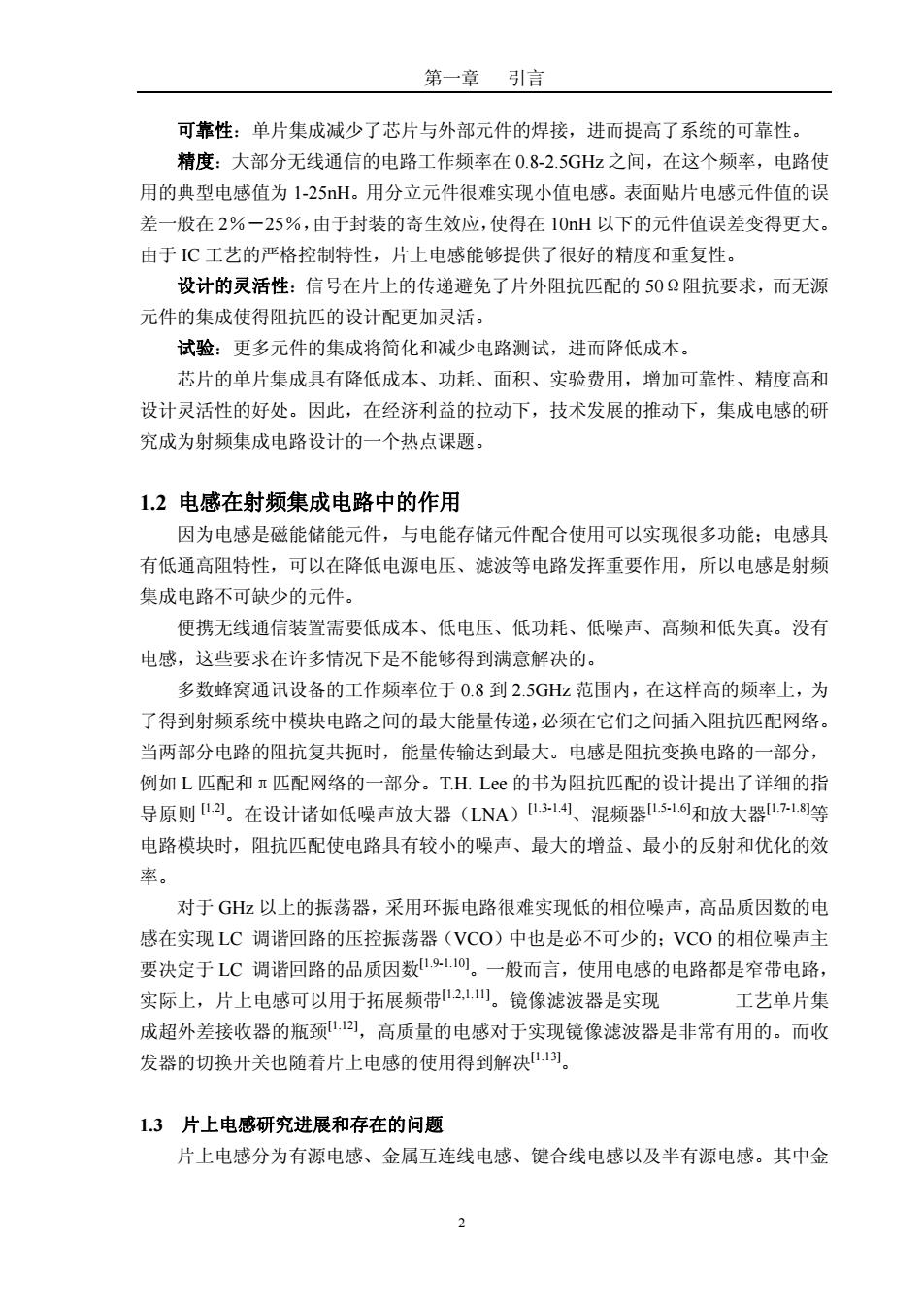

第一章 引言 属互连线电感是集成电感研究和使用的主要对象。 1.3.1集成电感 有源电感:在低频段可以通过使用有源器件模拟电感特征,而避免使用真实电感, 并可以实现比较大的电感值和Q值。有源电感和无源电感相比具有电感值可调,而且 芯片面积小的优点。无论电路的结构如何,有源电感都有相同的缺点:1)在高频上有 源器件的增益下降,使得模拟电感实现起来比较困难:2)有源电感需要占用电压,降 低其他电路的电压使用范围,使得有源电感电路的动态范围有限,3)有源电感给电路 带来附加噪声。这些缺点严重地限制了它的应用范围,特别是不能应用在高灵敏度的 模拟电路模块中。因此,这类电感主要应用于可调谐的滤波器14-1。 键合线电感:在芯片的两个焊点间、焊点与封装间以及封装与封装间焊接的金属 线称为键合线电感,见图1.1。焊线适用于任何一种工艺,可以认为是标准集成电路 元件。但是焊线在制作过程会产生垂直和水平方向的长度偏差以及金属线直径偏差, 从而导致电感量的变化,所以焊线电感的可重复性差。键合线电感的Q值可高达30一 60,但是其电感值变化范围有限,一般在0.5·4H,焊盘等引起的寄生电容比较大, 电感值的波动大,可预测性和重复性差,从而限制了它的广泛应用。因为键合线电感 的品质因数比较大,所以也有些人对其进行研究16-117。 Multilevel Interconnects Pad Lead Metal Four Metal Three Hae V7a Metal One n FOX Epitaxial Active P Substrate Bond Wire 图1.1键合线示意图 图1.2CMOS工艺互连线示意图 金属互连线电感:由金属互连线(见图12)构成的螺旋电感与IC工艺兼容,稳 定性好,并且可以实现的电感值范围比较大,从几百pH一几百H,为电路的设计提 供了灵活性。它们不需要通过焊盘与外界连接,可降低成本,提高成品率,因此被广 泛采用,是集成电感的主要形式,常被称为片上电感。 半有源电感:Tony Yeung!.1提出了采用有源电路抵消无源电感电阻的方法,进 而实现高品质因数电感。Soorapanth,T等采用半有源的电感实现了片上滤波器1.1☑,可 以替代片外的声表面波滤波器,使得滤波器的频率不再拘泥于声表面波滤波器的材料 特性,可以灵活设计。半有源电感是一个值得研究的方向

第一章 引言 3 属互连线电感是集成电感研究和使用的主要对象。 1.3.1 集成电感 有源电感:在低频段可以通过使用有源器件模拟电感特征,而避免使用真实电感, 并可以实现比较大的电感值和Q值。有源电感和无源电感相比具有电感值可调,而且 芯片面积小的优点。无论电路的结构如何,有源电感都有相同的缺点:1)在高频上有 源器件的增益下降,使得模拟电感实现起来比较困难;2)有源电感需要占用电压,降 低其他电路的电压使用范围,使得有源电感电路的动态范围有限,3)有源电感给电路 带来附加噪声。这些缺点严重地限制了它的应用范围,特别是不能应用在高灵敏度的 模拟电路模块中。因此,这类电感主要应用于可调谐的滤波器 [1.14-1.15]。 键合线电感:在芯片的两个焊点间、焊点与封装间以及封装与封装间焊接的金属 线称为键合线电感 ,见图1.1。焊线适用于任何一种工艺,可以认为是标准集成电路 元件。但是焊线在制作过程会产生垂直和水平方向的长度偏差以及金属线直径偏差, 从而导致电感量的变化,所以焊线电感的可重复性差。键合线电感的Q值可高达30- 60,但是其电感值变化范围有限,一般在0.5 - 4nH,焊盘等引起的寄生电容比较大, 电感值的波动大,可预测性和重复性差,从而限制了它的广泛应用。因为键合线电感 的品质因数比较大,所以也有些人对其进行研究[1.16-1.17]。 图 1.1 键合线示意图 图 1.2 CMOS 工艺互连线示意图 金属互连线电感:由金属互连线(见图 1.2)构成的螺旋电感与 IC 工艺兼容,稳 定性好,并且可以实现的电感值范围比较大,从几百 pH-几百 nH,为电路的设计提 供了灵活性。它们不需要通过焊盘与外界连接,可降低成本,提高成品率,因此被广 泛采用,是集成电感的主要形式,常被称为片上电感。 半有源电感:Tony Yeung[1.18] 提出了采用有源电路抵消无源电感电阻的方法,进 而实现高品质因数电感。Soorapanth, T 等采用半有源的电感实现了片上滤波器[1.12],可 以替代片外的声表面波滤波器,使得滤波器的频率不再拘泥于声表面波滤波器的材料 特性,可以灵活设计。半有源电感是一个值得研究的方向