第32卷第3期 微电子学 Vol.32,N9 3 2002年6月 Microelectronics Jun.2002 文章编号:1004-3365(2002)03-0185-04 从模式I2C总线接口电路设计及其VLSI实现 陈安,唐长文,闵昊 (复旦大学专用集成电路和系统国家重点实验室,上海200433) 摘要:提出了一种从模式的I2C总线接口电路,该接口电路实现了对可变参数ASIC芯片的配 置。该电路的设计使得可配置的ASIC芯片中参数配置所需要的芯片管脚大大减少。该方案已通过 行为仿真和综合后门级时序仿真,并且用无锡上华0.6μm CMOS工艺实现。 关键词:I2C总线;接口电路;从模式;VHDL:ASIC 中图分类号:TN47 文献标识码:A Design of a Slave I2C Bus Interface Circuit and Its VLSI Implementation CHEN An,TANG Zhang-wen,MIN Hao (State Key Laboratory of ASIC &System,Fudan Univ.Shanghai 200433,P.R.China) Abstract:An IC bus interface circuit in slave mode is presented in the paper.This interface makes it possible to program the parameter of the programmable ASIC chip.Meanwhile,it greatly reduces pins of the chip.The de- sign of the circuit has passed behavioral simulation and timing simulation after synthesis.And the circuit has been implemented in Wuxi Shanghua's 0.6 um CMOS process. Key words:IC bus;Interface circuit Slave-mode:VHDL:ASIC EEACC:1290 ASIC芯片,以很少的代价节省芯片的管脚。最典型 1引言 的应用是在参数可配置的ASIC芯片,通过该接口 电路只需两个管脚就可实现参数的输入和参数的输 I2C总线是一种被广泛应用的芯片间串行总 出验证,如图1所示。完成相应功能的并行总线接口 线,该总线最早是由Philips公司提出并倡导的。I2C 需要很多管脚,比如8位总线至少需要8条数据总 总线通过两条信号线实现了连接在总线上的器件之 线、若干条地址总线、读写控制线和片选线。 间的软件寻址和同步串行数据传输,完全避免了器 件间传统的片选寻址方法,节省了大量的数据总线、 地址总线、控制总线所占用的芯片管脚和PCB板的 面积。器件之间简单的12C总线互联方式,可以使用 ASIC 户的硬件系统具有最简单而灵活的扩展方法、简单 能接口好 而有效的系统调试和故障排除方案。并且在设计基 作的 于I2C总线的用户系统时,由于功能模块图上的功 能模块的互联可以直接对应实际的I2℃总线器件的 图112C总线接口示意图 互联,可以很方便地把功能模块图转变成电原理图。 如果再把常用的软件模块建库保存,开发用户系统 2I2C总线的基本原理[1,2] 的软件部分所花费的时间和资源也可以大大减少。 本设计中包含了一个由ASIC实现的从模式 I2C总线是通过两条双向线(时钟线SCL和数 I2C总线的接口,它可作为一个成熟的IP核嵌入到 据线SDA)在器件之间传递信息的。SDA、SCL的输 收稿日期:2001-07-17;定稿日期:2001-09-20

收稿日期!"##$%#&%$&’ 定稿日期!"##$%#(%"# 文章编号!$##)%**+,-"##".#*%#$/,%#) 从模式 0 1 2总线接口电路设计及其 3450实现 陈 安6唐长文6闵 昊 -复旦大学 专用集成电路和系统国家重点实验室6上海 "##)**. 摘 要! 提出了一种从模式的 7 " 8总线接口电路6该接口电路实现了对可变参数 9:78芯片的配 置;该电路的设计使得可配置的 9:78芯片中参数配置所需要的芯片管脚大大减少;该方案已通过 行为仿真和综合后门级时序仿真6并且用无锡上华 # 8?@:工艺实现; 关键词! 7 " 8总线’接口电路’从模式’ABCD’9:78 中图分类号! EF)& 文献标识码! 9 GHIJKLMNO5POQH0R 2STI0LUHVNOWH2JVWTJUOLX0UI34500YZPHYHLUOUJML 8B[F 9\6E9F]^_‘\a%bc\6?7F B‘d -efgfhihjkglmngfmnjmopeqrsejtfhu6vwxgyzy{|d0c)(1+c(c\*c0)\*_c1‘1c+‘2c()*1d(()&.c *d1+da+‘> *_c1‘+‘>c*c+d,*_c1+da+‘>>‘&.c9:78-_)1’.‘*)d\‘\0*)>)\a()>’.‘*)d\‘,*c+(3\*_c()(1.c>c\*c0)\4’5):_‘\a_’‘6(# 8?@:1+d-c((d0c’ABCD’9:78 ::$22! $"(# $ 引 言 7 " 8总 线 是 一 种 被 广 泛 应 用 的 芯 片 间 串 行 总 线6该总线最早是由 ;_).)1(公司提出并倡导的;7 " 8 总线通过两条信号线实现了连接在总线上的器件之 间的软件寻址和同步串行数据传输6完全避免了器 件间传统的片选寻址方法6节省了大量的数据总线$6"? 7 " 8总线是通过两条双向线-时钟线 :8D和数 据线 :C9.在器件之间传递信息的;:C9<:8D的输 第 *"卷第 *期 "##"年 +月 微 电 子 学 @ABCDEFEBGCDHABI Ad.<*"6J * K’\ LLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLL <"##

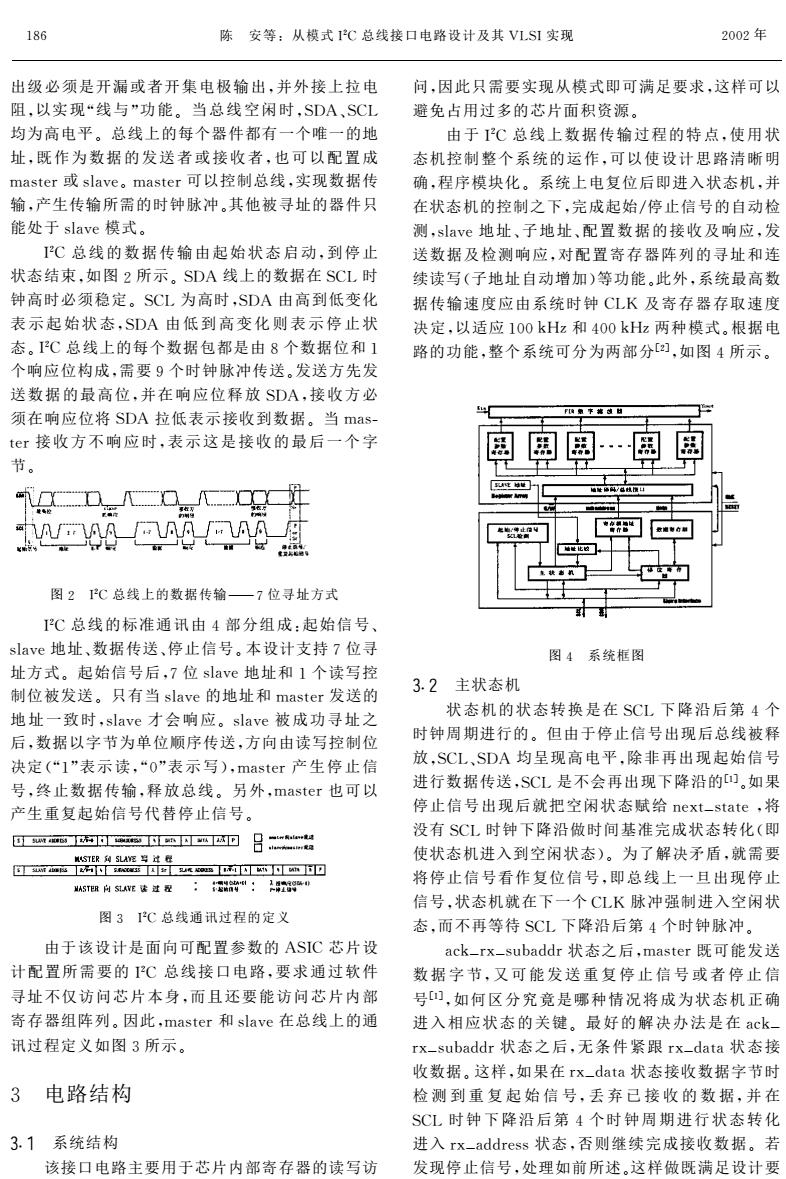

186 陈安等:从模式IC总线接口电路设计及其VISI实现 2002年 出级必须是开漏或者开集电极输出,并外接上拉电 问,因此只需要实现从模式即可满足要求,这样可以 阻,以实现“线与”功能。当总线空闲时,SDA、SCL 避免占用过多的芯片面积资源。 均为高电平。总线上的每个器件都有一个唯一的地 由于C总线上数据传输过程的特点,使用状 址,既作为数据的发送者或接收者,也可以配置成 态机控制整个系统的运作,可以使设计思路清晰明 master或slave。master可以控制总线,实现数据传 确,程序模块化。系统上电复位后即进入状态机,并 输,产生传输所需的时钟脉冲。其他被寻址的器件只 在状态机的控制之下,完成起始/停止信号的自动检 能处于slave模式。 测,slave地址、子地址、配置数据的接收及响应,发 ℃总线的数据传输由起始状态启动,到停止 送数据及检测响应,对配置寄存器阵列的寻址和连 状态结束,如图2所示。SDA线上的数据在SCL时 续读写(子地址自动增加)等功能。此外,系统最高数 钟高时必须稳定。SCL为高时,SDA由高到低变化 据传输速度应由系统时钟CLK及寄存器存取速度 表示起始状态,SDA由低到高变化则表示停止状 决定,以适应100kHz和400kHz两种模式。根据电 态。I℃总线上的每个数据包都是由8个数据位和1 路的功能,整个系统可分为两部分),如图4所示。 个响应位构成,需要9个时钟脉冲传送。发送方先发 送数据的最高位,并在响应位释放SDA,接收方必 须在响应位将SDA拉低表示接收到数据。当mas- ter接收方不响应时,表示这是接收的最后一个字 节。 图2℃总线上的数据传输一7位寻址方式 I℃总线的标准通讯由4部分组成:起始信号、 slave地址、数据传送、停止信号。本设计支持7位寻 图4系统框图 址方式。起始信号后,7位slave地址和1个读写控 3.2主状态机 制位被发送。只有当slave的地址和master发送的 地址一致时,slave才会响应。slave被成功寻址之 状态机的状态转换是在SCL下降沿后第4个 后,数据以字节为单位顺序传送,方向由读写控制位 时钟周期进行的。但由于停止信号出现后总线被释 决定(“1”表示读,“0”表示写),master产生停止信 放,SCL、SDA均呈现高电平,除非再出现起始信号 号,终止数据传输,释放总线。另外,master也可以 进行数据传送,SCL是不会再出现下降沿的)。如果 产生重复起始信号代替停止信号。 停止信号出现后就把空闲状态赋给next-state,将 没有SCL时钟下降沿做时间基准完成状态转化(即 ww可 STER4SLAE号进释 使状态机进入到空闲状态)。为了解决矛盾,就需要 国AF 4W 55 SUAOCAESS A元oW1N可内d▣ h5TER内品AwE速过显:粉: 将停止信号看作复位信号,即总线上一旦出现停止 信号,状态机就在下一个CLK脉冲强制进入空闲状 图31℃总线通讯过程的定义 态,而不再等待SCL下降沿后第4个时钟脉冲。 由于该设计是面向可配置参数的ASIC芯片设 ack-rx-subaddr状态之后,master既可能发送 计配置所需要的I℃总线接口电路,要求通过软件 数据字节,又可能发送重复停止信号或者停止信 寻址不仅访问芯片本身,而且还要能访问芯片内部 号们,如何区分究竞是哪种情况将成为状态机正确 寄存器组阵列。因此,master和slave在总线上的通 进入相应状态的关键。最好的解决办法是在ack 讯过程定义如图3所示。 rx-subaddr状态之后,无条件紧跟rx-data状态接 收数据。这样,如果在rx_-data状态接收数据字节时 3 电路结构 检测到重复起始信号,丢弃已接收的数据,并在 SCL时钟下降沿后第4个时钟周期进行状态转化 3.1系统结构 进入rx-address状态,否则继续完成接收数据。若 该接口电路主要用于芯片内部寄存器的读写访 发现停止信号,处理如前所述。这样做既满足设计要

出级必须是开漏或者开集电极输出!并外接上拉电 阻!以实 现"线 与#功 能$当 总 线 空 闲 时!%&’(%)* 均为高电平$总线上的每个器件都有一个唯一的地 址!既 作 为 数 据 的 发 送 者 或 接 收 者!也 可 以 配 置 成 +,-./0或 -1,2/$+,-./0可以控制总线!实现数据传 输!产生传输所需的时钟脉冲$其他被寻址的器件只 能处于 -1,2/模式$ 3 4 )总 线 的 数 据 传 输 由 起 始 状 态 启 动!到 停 止 状态结束!如图 4所示$%&’线上的数据在 %)*时 钟高时必须稳定$%)*为高时!%&’由高到低变化 表 示 起 始 状 态!%&’ 由 低 到 高 变 化 则 表 示 停 止 状 态$3 4 )总线上的每个数据包都是由 5个数据位和 6 个响应位构成!需要 7个时钟脉冲传送$发送方先发 送数据的最高位!并在响应位释 放 %&’!接 收 方 必 须在响应位将 %&’拉低表示接收到数据$当 +,-8 ./0接 收 方 不 响 应 时!表 示 这 是 接 收 的 最 后 一 个 字 节$ 图 4 3 4 )总线上的数据传输99 :位寻址方式 3 4 )总线的标准通讯由 ;部分组成#表 示 写?!+,-./0产 生 停 止 信 号!终止数据传输!释放总线$另外!+,-./0也可以 产生重复起始信号代替停止信号$ 图 @ 3 4 )总线通讯过程的定义 由于该设计是面向可配置参数的 ’%3)芯片设 计配置所需要的 3 4 )总线接口电路!要求通过软件 寻址不仅访问芯片本身!而且还要能访问芯片内部 寄存器组阵列$因此!+,-./0和 -1,2/在总线上的通 讯过程定义如图 @所示$ @ 电路结构 ABC 系统结构 该接口电路主要用于芯片内部寄存器的读写访 问!因此只需要实现从模式即可满足要求!这样可以 避免占用过多的芯片面积资源$ 由于 3 4 )总线上数据传输过程的特 点!使 用 状 态机控制整个系统的运作!可以使设计思路清晰明 确!程序模块化$系统上电复位后即进入状态机!并 在状态机的控制之下!完成起始D停止信号的自动检 测!-1,2/地址(子地址(配置数据的接收及响应!发 送数据及检测响应!对配置寄存器阵列的寻址和连 续读写=子地址自动增加?等功能$此外!系统最高数 据传输速度应由系统时钟 )*E及寄存器存取速度 决定!以适应 6>>FGH和 ;>>FGH两种模式$根据电 路的功能!整个系统可分为两部分I4J!如图 ;所示$ 图 ; 系统框图 ABK 主状态机 状态机的状态转换是在 %)*下降沿后第 ;个 时钟周期进行的$但由于停止信号出现后总线被释 放!%)*(%&’均呈现高电平!除非再出现起始信号 进行数据传送!%)*是不会再出现下降沿的I6J$如果 停止信号出现后就把空闲状态赋给 L/M.9 -.,./!将 没有 %)*时钟下降沿做时间基准完成状态转化=即 使状态机进入到空闲状态?$为了解决矛盾!就需要 将停止信号看作复位信号!即总线上一旦出现停止 信号!状态机就在下一个 )*E脉冲强制进入空闲状 态!而不再等待 %)*下降沿后第 ;个时钟脉冲$ ,NF9 0M9 -OP,QQ0状态之后!+,-./0既可能发送 数 据 字 节!又 可 能 发 送 重 复 停 止 信 号 或 者 停 止 信 号I6J!如何区分究竟是哪种情况将成为状态机正确 进 入相应状态的关键$最好的解决办 法 是 在 ,NF9 0M9 -OP,QQ0状态之后!无条件紧跟 0M9 Q,.,状态接 收数据$这样!如果在 0M9 Q,.,状态接收数据字节时 检 测 到 重 复 起 始 信 号!丢 弃 已 接 收 的 数 据!并 在 %)*时 钟 下 降 沿 后 第 ;个 时 钟 周 期 进 行 状 态 转 化 进入 0M9 ,QQ0/--状态!否则继续完成接收数据$若 发现停止信号!处理如前所述$这样做既满足设计要 65R 陈 安等>4年

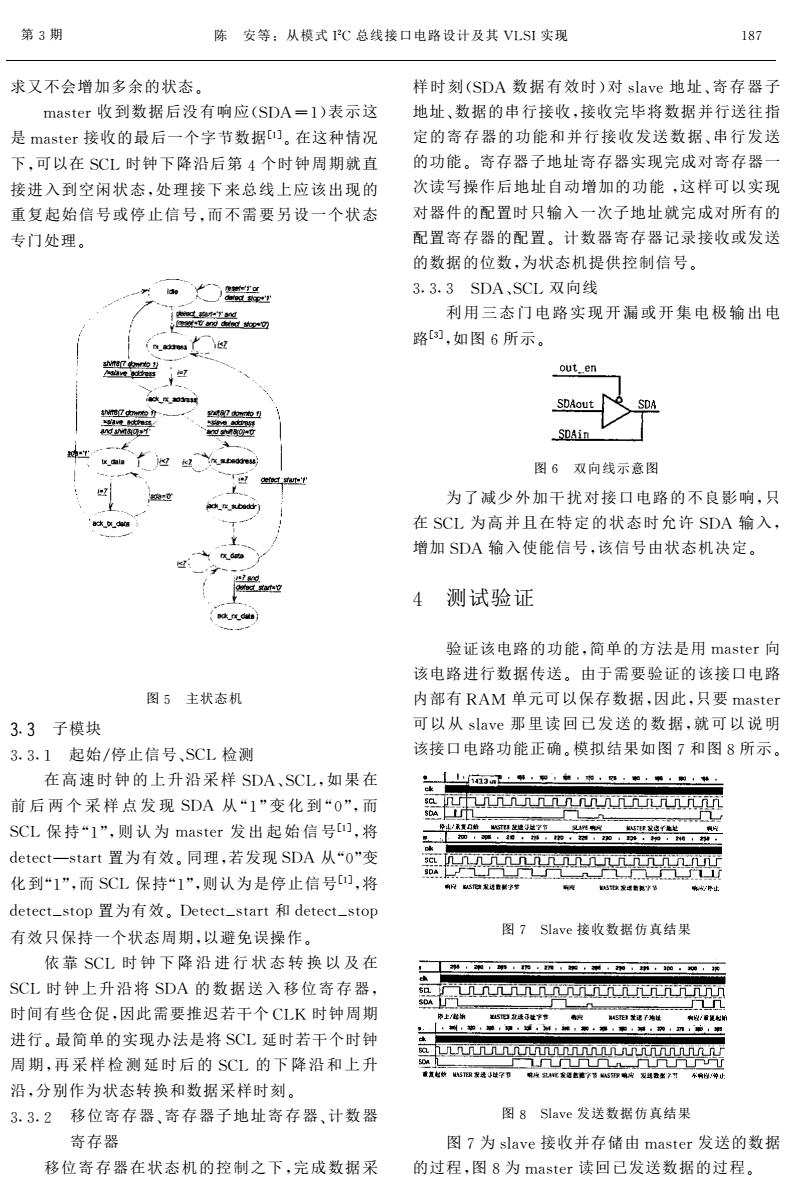

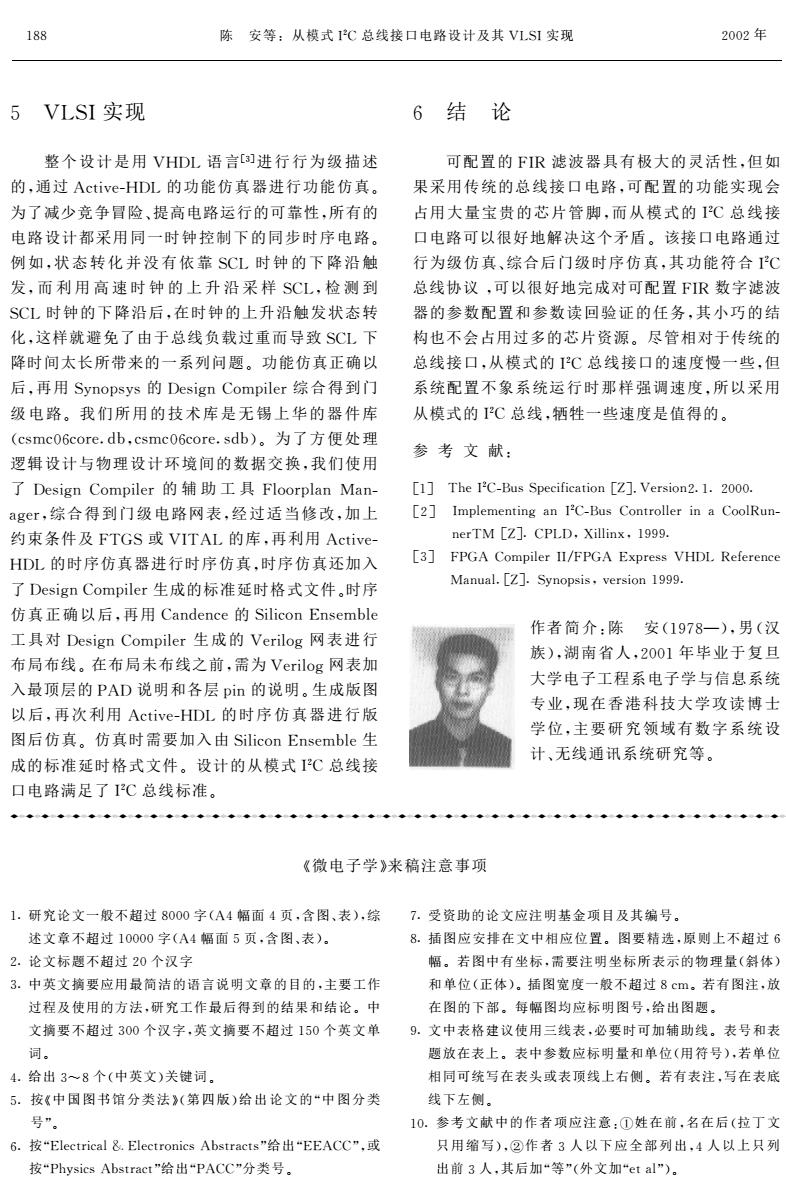

第3期 陈安等:从模式1C总线接口电路设计及其VISI实现 187 求又不会增加多余的状态。 样时刻(SDA数据有效时)对slave地址、寄存器子 master收到数据后没有响应(SDA=I)表示这 地址、数据的串行接收,接收完毕将数据并行送往指 是master接收的最后一个字节数据)。在这种情况 定的寄存器的功能和并行接收发送数据、串行发送 下,可以在SCL时钟下降沿后第4个时钟周期就直 的功能。寄存器子地址寄存器实现完成对寄存器一 接进入到空闲状态,处理接下来总线上应该出现的 次读写操作后地址自动增加的功能,这样可以实现 重复起始信号或停止信号,而不需要另设一个状态 对器件的配置时只输入一次子地址就完成对所有的 专门处理。 配置寄存器的配置。计数器寄存器记录接收或发送 的数据的位数,为状态机提供控制信号。 3.3.3SDA、SCL双向线 icod geond 利用三态门电路实现开漏或开集电极输出电 2t6n0ce过边 路[),如图6所示。 h的配安w也型 t短 outen SDAout SDA 辽介 SDAin 图6双向线示意图 为了减少外加干扰对接口电路的不良影响,只 在SCL为高并且在特定的状态时允许SDA输入, 增加SDA输入使能信号,该信号由状态机决定。 4测试验证 验证该电路的功能,简单的方法是用master向 该电路进行数据传送。由于需要验证的该接口电路 图5主状态机 内部有RAM单元可以保存数据,因此,只要master 3.3子模块 可以从slave那里读回已发送的数据,就可以说明 3.3.1起始/停止信号、SCL检测 该接口电路功能正确。模拟结果如图7和图8所示。 在高速时钟的上升沿采样SDA、SCL,如果在 前后两个采样点发现SDA从“1”变化到“0”,而 SCL保持“1”,则认为master发出起始信号们,将 经承复日静T和业进子世字官 detect-一start置为有效。同理,若发现SDA从“o”变 nnnn元nij 化到“1”,而SCL保持“1”,则认为是停止信号山,将 地发进售包序书 detect_stop置为有效。Detect-.start和detect_.stop 有效只保持一个状态周期,以避免误操作。 图7 Slave接收数据仿真结果 依靠SCL时钟下降沿进行状态转换以及在 ··第·的·m,年,·阳·,举 SCL时钟上升沿将SDA的数据送入移位寄存器, unnnnnnnnnnn 时间有些仓促,因此需要推迟若干个CLK时钟周期 具几 师上/出嫩 心回和进子生平节款5装这墙址南以:量便财的 进行。最简单的实现办法是将SCL延时若干个时钟 物第,果·,带·型:准:瑞n的 aLUnLuuuiuUuUUurUi 周期,再采样检测延时后的SCL的下降沿和上升 L拉 :5因架绿世子节明片氧爱直宽不装5西确牌双线数堂子T本响:钟止 沿,分别作为状态转换和数据采样时刻。 3.3.2移位寄存器、寄存器子地址寄存器、计数器 图8 Slave发送数据仿真结果 寄存器 图7为slave接收并存储由master发送的数据 移位寄存器在状态机的控制之下,完成数据采 的过程,图8为master读回已发送数据的过程

求又不会增加多余的状态! "#$%&’收到数据后没有响应()*+,-.表示这 是 "#$%&’接收的最后一个字节数据/-0!在这种情况 下1可以在 )23时钟下降沿后第 4个时钟周期就直 接进入到空闲状态1处理接下来总线上应该出现的 重复起始信号或停止信号1而不需要另设一个状态 专门处理! 图 5 主状态机 676 子模块 8787- 起始9停止信号:)23检测 在 高 速 时 钟 的 上 升 沿 采 样 )*+:)231如 果 在 前 后 两 个 采 样 点 发 现 )*+ 从 ;-&%&?%@$%#’%置为有效!同理1若发现 )*+从;=&%&?%A$%BC置为有效!*&%&?%A $%#’%和 >&%&?%A $%BC 有效只保持一个状态周期1以避免误操作! 依 靠 )23时 钟 下 降 沿 进 行 状 态 转 换 以 及 在 )23时 钟 上 升 沿 将 )*+ 的 数 据 送 入 移 位 寄 存 器1 时间有些仓促1因此需要推迟若干个 23D时钟周期 进行!最简单的实现办法是将 )23延时若干个时钟 周 期1再 采 样 检 测 延 时 后 的 )23的 下 降 沿 和 上 升 沿1分别作为状态转换和数据采样时刻! 8787E 移位寄存器:寄存器子地址寄存器:计数器 寄存器 移位寄存器在状态机的控制之下1完成数据采 样 时刻()*+数据有效时.对 $F#G&地址:寄存器子 地址:数据的串行接收1接收完毕将数据并行送往指 定的寄存器的功能和并行接收发送数据:串行发送 的功能!寄存器子地址寄存器实现完成对寄存器一 次读写操作后地址自动增加的功能 1这样可以实现 对器件的配置时只输入一次子地址就完成对所有的 配置寄存器的配置!计数器寄存器记录接收或发送 的数据的位数1为状态机提供控制信号! 87878 )*+:)23双向线 利 用 三 态 门 电 路 实 现 开 漏 或 开 集 电 极 输 出 电 路/801如图 H所示! 图 H 双向线示意图 为了减少外加干扰对接口电路的不良影响1只 在 )23为高并且在特定的状态时允许 )*+输入1 增加 )*+输入使能信号1该信号由状态机决定! 4 测试验证 验证该电路的功能1简单的方法是用 "#$%&’向 该电路进行数据传送!由于需要验证的该接口电路 内部有 I+J 单元可以保存数据1因此1只要 "#$%&’ 可 以 从 $F#G&那 里 读 回 已 发 送 的 数 据1就 可 以 说 明 该接口电路功能正确!模拟结果如图 K和图 L所示! 图 K )F#G&接收数据仿真结果 图 L )F#G&发送数据仿真结果 图 K为 $F#G&接收并存储由 "#$%&’发送的数据 的过程1图 L为 "#$%&’读回已发送数据的过程! 第 8期 陈 安等M从模式 N E 2总线接口电路设计及其 O3)N实现 -LK

188 陈安等:从模式I℃总线接口电路设计及其V1SI实现 2002年 5VLSI实现 6 结 论 整个设计是用VHDL语言[]进行行为级描述 可配置的FIR滤波器具有极大的灵活性,但如 的,通过Active-HDL的功能仿真器进行功能仿真。 果采用传统的总线接口电路,可配置的功能实现会 为了减少竞争冒险、提高电路运行的可靠性,所有的 占用大量宝贵的芯片管脚,而从模式的I℃总线接 电路设计都采用同一时钟控制下的同步时序电路。 口电路可以很好地解决这个矛盾。该接口电路通过 例如,状态转化并没有依靠SCL时钟的下降沿触 行为级仿真、综合后门级时序仿真,其功能符合℃ 发,而利用高速时钟的上升沿采样SCL,检测到 总线协议,可以很好地完成对可配置FIR数字滤波 SCL时钟的下降沿后,在时钟的上升沿触发状态转 器的参数配置和参数读回验证的任务,其小巧的结 化,这样就避免了由于总线负载过重而导致SCL下 构也不会占用过多的芯片资源。尽管相对于传统的 降时间太长所带来的一系列问题。功能仿真正确以 总线接口,从模式的I℃总线接口的速度慢一些,但 后,再用Synopsys的Design Compiler综合得到门 系统配置不象系统运行时那样强调速度,所以采用 级电路。我们所用的技术库是无锡上华的器件库 从模式的I℃总线,牺牲一些速度是值得的。 (csmc06core.db,csmc06core.sdb)。为了方便处理 参考文献: 逻辑设计与物理设计环境间的数据交换,我们使用 了Design Compiler的辅助工具Floorplan Man- [1]The I2C-Bus Specification [Z].Version2.1.2000. ager,综合得到门级电路网表,经过适当修改,加上 [2] Implementing an I2C-Bus Controller in a CoolRun- 约束条件及FTGS或VITAL的库,再利用Active- nerTM Z.CPLD,Xillinx,1999. HDL的时序仿真器进行时序仿真,时序仿真还加入 [3]FPGA Compiler II/FPGA Express VHDL Reference 了Design Compiler生成的标准延时格式文件。时序 Manual.[Z].Synopsis,version 1999. 仿真正确以后,再用Candence的Silicon Ensemble 作者简介:陈安(1978一),男(汉 工具对Design Compiler生成的Verilog网表进行 族),湖南省人,2001年毕业于复旦 布局布线。在布局未布线之前,需为Verilog网表加 大学电子工程系电子学与信息系统 入最顶层的PAD说明和各层pin的说明。生成版图 以后,再次利用Active-HDL的时序仿真器进行版 专业,现在香港科技大学攻读博士 学位,主要研究领域有数字系统设 图后仿真。仿真时需要加入由Silicon Ensemble生 计、无线通讯系统研究等。 成的标准延时格式文件。设计的从模式℃总线接 口电路满足了I℃总线标准。 《微电子学》来稿注意事项 1.研究论文一般不超过8000字(A4幅面4页,含图、表),综7.受资助的论文应注明基金项目及其编号。 述文章不超过10000字(A4幅面5页,含图,表)。 8.插图应安排在文中相应位置。图要精选,原则上不超过6 2.论文标题不超过20个汉字 幅。若图中有坐标,需要注明坐标所表示的物理量(斜体) 3.中英文摘要应用最简洁的语言说明文章的目的,主要工作 和单位(正体)。插图宽度一般不超过8cm。若有图注,放 过程及使用的方法,研究工作最后得到的结果和结论。中 在图的下部。每幅图均应标明图号,给出图题。 文摘要不超过300个汉字,英文摘要不超过150个英文单 9.文中表格建议使用三线表,必要时可加辅助线。表号和表 词。 题放在表上。表中参数应标明量和单位(用符号),若单位 4.给出3~8个(中英文)关键词。 相同可统写在表头或表顶线上右侧。若有表注,写在表底 5.按《中国图书馆分类法》(第四版)给出论文的“中图分类 线下左侧。 号”。 10.参考文献中的作者项应注意:①姓在前,名在后(拉丁文 6.按“Electrical&.Electronics Abstracts”给出“EEACC”,或 只用缩写),②作者3人以下应全部列出,4人以上只列 按“Physics Abstract'"给出“PACC”分类号。 出前3人,其后加“等”(外文加“etal”)

! "#$%实现 整 个 设 计 是 用 "&’#语 言()*进 行 行 为 级 描 述 的+通过 ,-./012&’#的功能仿真器进行功能仿真3 为了减少竞争冒险4提高电路运行的可靠性+所有的 电路设计都采用同一时钟控制下的同步时序电路3 例 如+状 态 转 化 并 没 有 依 靠 $5#时 钟 的 下 降 沿 触 发+而 利 用 高 速 时 钟 的 上 升 沿 采 样 $5#+检 测 到 $5#时钟的下降沿后+在时钟的上升沿触发状态转 化+这样就避免了由于总线负载过重而导致 $5#下 降时间太长所带来的一系列问题3功能仿真正确以 后+再用 $6789:6:的 ’1:/;758综合得到门 级 电 路3我 们 所 用 的 技 术 库 是 无 锡 上 华 的 器 件 库 ?-:1BCD+-:1B:CDE3为了方 便 处 理 逻辑设计与物理设计环境间的数据交换+我们使用 了 ’1:/;758的 辅 助 工 具 F=88>9=G7HG72 G;1>+综合得到门级电路网表+经过适当修 改+加 上 约束条件及 FIJ$或 "%I,#的库+再利用 ,-./012 &’#的时序仿真器进行时序仿真+时序仿真还加入 了 ’1:/;758生成的标准延时格式文件3时序 仿真正确以后+再用 5G7C17-1的 $/=/-87K7:1生 成 的 "1>/=8;网 表 进 行 布局布线3在布局未布线之前+需为 "1>/=8;网表加 入最顶层的 L,’说明和各层 9/7的说明3生成版图 以 后+再 次 利 用 ,-./012&’#的 时 序 仿 真 器 进 行 版 图后仿真3仿真时需要加入由 $/=/-87K7:1:/87MBPBM@@@B (M* %8==1>/7G588=NS72 71>IH (U*B5L#’+W/==/7X+PYYYB ()* FLJ, 58%%ZFLJ, KX9>1::"&’# N1T1>17-1 HG7SG=V(U*B$6789:/:+01>:/87PYYYB 作者 简 介O陈 安?PY[\]E+男?汉 族E+湖南省人+M@@P年毕业于复旦 大学电子工程系电子学与信息系统 专业+现在香港科技大学攻读 博 士 学位+主要研究领域有数字系 统 设 计4无线通讯系统研究等 ^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^ 3 _微电子学‘来稿注意事项 PB研究论文一般不超过 \@@@字?,a幅面 a页+含图4表E+综 述文章不超过 P@@@@字?,a幅面 !页+含图4表E3 MB论文标题不超过 M@个汉字 )B中英文摘要应用最简洁的语言说明文章的目的+主要工作 过程及使用的方法+研究工作最后得到的结果和结论3中 文摘要不超过 )@@个汉字+英文摘要不超过 P!@个英文单 词3 aB给出 )b\个?中英文E关键词3 !B按_中 国 图 书 馆 分 类 法‘?第 四 版E给 出 论 文 的c中 图 分 类 号d3 AB按cK=1-.>/-G=eK=1-.>87/-:,D:.>G-.:d给出cKK,55d+或 按cLQ6:/-:,D:.>G-.d给出cL,55d分类号3 [B受资助的论文应注明基金项目及其编号3 \B插图应安排在文中相应位置3图要精选+原则上不超过 A 幅3若图中有坐标+需要注明坐标所表示的物理量?斜体E 和 单位?正体E3插图宽度一般不超过 \-<3若有图注+放 在图的下部3每幅图均应标明图号+给出图题3 YB文中表格建议使用三线表+必要时可加辅助线3表号和表 题放在表上3表中参数应标明量和单位?用符号E+若单位 相同可统写在表头或表顶线上右侧3若有表注+写在表底 线下左侧3 P@B参考文献中的作者项应注意Of姓在前+名在后?拉丁文 只 用 缩 写E+g作 者 )人 以 下 应 全 部 列 出+a人 以 上 只 列 出前 )人+其后加c等d?外文加c1.G=dE3 P\\ 陈 安等O从模式 % M 5总线接口电路设计及其 "#$%实现 M@@M年