第32卷第3期 微电子学 Vol.32,No 3 2002年6月 Microelectronics Jun.2002 文章编号:1004-3365(2002)03-0189-03 全扫描结构可测性设计方法的研究 祝永明,唐长文,闵昊 (复旦大学专用集成电路与系统国家重点实验室,上海200433) 摘要:探讨了在Synopsys软件中用全扫描结构实现数字电路可测性设计中遇到的问题及解决 方法,如扫描结构的基本结构、测试的时序等问题。扫描结构对电路本身的结构有严格的要求,重点 讨论了扫描结构对电路结构的限制及对违反限制的电路进行修改的方法。 关键词:数字电路;可测性设计;扫描结构;设计规则 中图分类号:TN407:TN43 文献标识码:A Research on the Full-Scan Method in Design for Testability ZHU Yong-ming,TANG Zhang-wen,MIN Hao (State Key Laboratory of ASIC System,Fudan Univ..Shanghai 200433,P.R.China) Abstract:Application of scanning method in the design for testability (DFT)of digital system is described in the paper.Problems with DFT,such as the basic scanning structure and test sequence,are discussed.In scanning method,strict regulations are imposed on the original circuit structure of the chip.Restrictions of the scanning structure on the circuit structures and revision of a circuit to conform to the regulations are discussed in particular. Key words:Digital IC;Design for testability:Scanning structure;Design rule EEACC:1265 已有电路中,但它对电路的结构,尤其是时钟和复位 1 引言 端的结构有着严格的要求。如何修改已有电路,使其 符合DFT Compiler对电路结构的要求,是本文讨 随着微电子学的迅速发展,集成电路规模迅速 论的重点。 膨胀,电路结构越来越复杂。由于芯片管脚的限制和 大量故障变得不可测等因素的影响,过去由测试人 2扫描结构的原理 员根据已经设计或研制完成的系统和电路来制定测 试方案的传统做法已不适应实际生产的要求。功能 2.1扫描电路的基本结构 设计人员在设计系统和电路的同时,必须考虑到测 使用最多的扫描电路是多路选择结构,图1是 试的要求,这就是所谓的可测性设计]。 典型扫描方式电路的方框图。多路选择结构是使用 实现可测性设计有许多种方法,本文讨论扫描 一个多路信号输入来实现串行移位功能[幻。图1中, 方式电路设计(scan)方法。与其它方法相比,扫描结 电路组合部分被单列开来,由D触发器组成的时序 构的优势在于结构简单、对芯片面积影响小,实用效 电路成为了扫描链。当控制输入SCAN ENABLE= 果相当好。扫描方式可将测试矢量集从输入端“移 0时,电路动作按正常方式进行,执行电路的功能: 入”电路内部,并且可将电路内部的信号值“移出” 当控制信号SCAN ENABLE=1时,各触发器形成 来观察,从本质上提高了电路的可观察性和可控制 一个移位寄存器,为扫描方式。在扫描方式下,各触 性。Synopsys软件中,有专门针对扫描结构的测试 发器可设定任意值,也可方便地从扫描输出端(scan 软件DFT Compiler,它可以自动将扫描部分整合到 output)观察其输出值。 收稿日期:2001-07-12:定稿日期:2001-09-12

收稿日期!"##$%#&%$"’ 定稿日期!"##$%#(%$" 文章编号!$##)%**+,-"##".#*%#$/(%#* 全扫描结构可测性设计方法的研究 祝永明 0唐长文 0闵 昊 -复旦大学 专用集成电路与系统国家重点实验室0上海 "##)**. 摘 要! 探讨了在 12345626软件中用全扫描结构实现数字电路可测性设计中遇到的问题及解决 方法0如扫描结构的基本结构7测试的时序等问题8扫描结构对电路本身的结构有严格的要求0重点 讨论了扫描结构对电路结构的限制及对违反限制的电路进行修改的方法8 关键词! 数字电路’可测性设计’扫描结构’设计规则 中图分类号! 9:)#&’9:)* 文献标识码! ; =?@ABCDEB=FGHHIJA?DK=EBCLMDN=>MODPC@Q=>E?RMHMES TUV W43X%YZ3X09;:[T\]3X%^_30‘a: U]4 -bcdcefeghdijkdcjkgjlmbnopbgqcer0studvwvxyz0b{dv|{dx"##)**0}~!~o{xvd. "R>E@?AE! ;55#Z$]%Z434&6$]33Z3XY_%\4’Z3%\_’_6ZX3&4(%_6%])Z#Z%2-*+9.4&’ZXZ%]#626%_Y Z6’_6$(Z)_’Z3 %\_5]5_(~,(4)#_Y6^Z%\*+906-$\]6%\_)]6Z$6$]33Z3X6%(-$%-(_]3’%_6%6_.-_3$_0](_’Z6$-66_’~a36$]33Z3X Y_%\4’06%(Z$%(_X-#]%Z436](_ZY546_’43%\_4(ZXZ3]#$Z($-Z%6%(-$%-(_4&%\_$\Z5~/_6%(Z$%Z4364&%\_6$]33Z3X 6%(-$%-(_43%\_$Z($-Z%6%(-$%-(_6]3’(_0Z6Z434&]$Z($-Z%%4$43&4(Y %4%\_(_X-#]%Z436](_’Z6$-66_’Z35](%Z$-#](~ 1=S2C@L>! *ZXZ%]#a3’*_6ZX3&4(%_6%])Z#Z%2’1$]33Z3X6%(-$%-(_’*_6ZX3(-#_ 44"55! $"+, $ 引 言 随着微电子学的迅速发展0集成电路规模迅速 膨胀0电路结构越来越复杂8由于芯片管脚的限制和 大量故障变得不可测等因素的影响0过去由测试人 员根据已经设计或研制完成的系统和电路来制定测 试方案的传统做法已不适应实际生产的要求8功能 设计人员在设计系统和电路的同时0必须考虑到测 试的要求0这就是所谓的可测性设计6$7 8 实现可测性设计有许多种方法0本文讨论扫描 方式电路设计-6$]3.方法8与其它方法相比0扫描结 构的优势在于结构简单7对芯片面积影响小0实用效 果相当好8扫描方式可将测试矢量集从输入端8移 入9电路内部0并且可将电路内部的信号值 8移出9 来观察0从本质上提高了电路的可观察性和可控制 性812345626软件中0有专门针对扫描结构的测试 软件 *+934Y5Z#_(0它可以自动将扫描部分整合到 已有电路中0但它对电路的结构0尤其是时钟和复位 端的结构有着严格的要求8如何修改已有电路0使其 符合 *+9 34Y5Z#_(对电路结构的要求0是本文讨 论的重点8 " 扫描结构的原理 :~; 扫描电路的基本结构 使用最多的扫描电路是多路选择结构0图 $是 典型扫描方式电路的方框图8多路选择结构是使用 一个多路信号输入来实现串行移位功能6"7 8图 $中0 电路组合部分被单列开来0由 *触发器组成的时序 电路成为了扫描链8当控制输入 13;:<?$时0各触发器形成 一个移位寄存器0为扫描方式8在扫描方式下0各触 发器可设定任意值0也可方便地从扫描输出端-6$]3 4-%5-%.观察其输出值8 第 *"卷第 *期 "##"年 +月 微 电 子 学 @ABCDEFEBGCDHABI J4#~*"0K * L-3 MMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMM ~"##

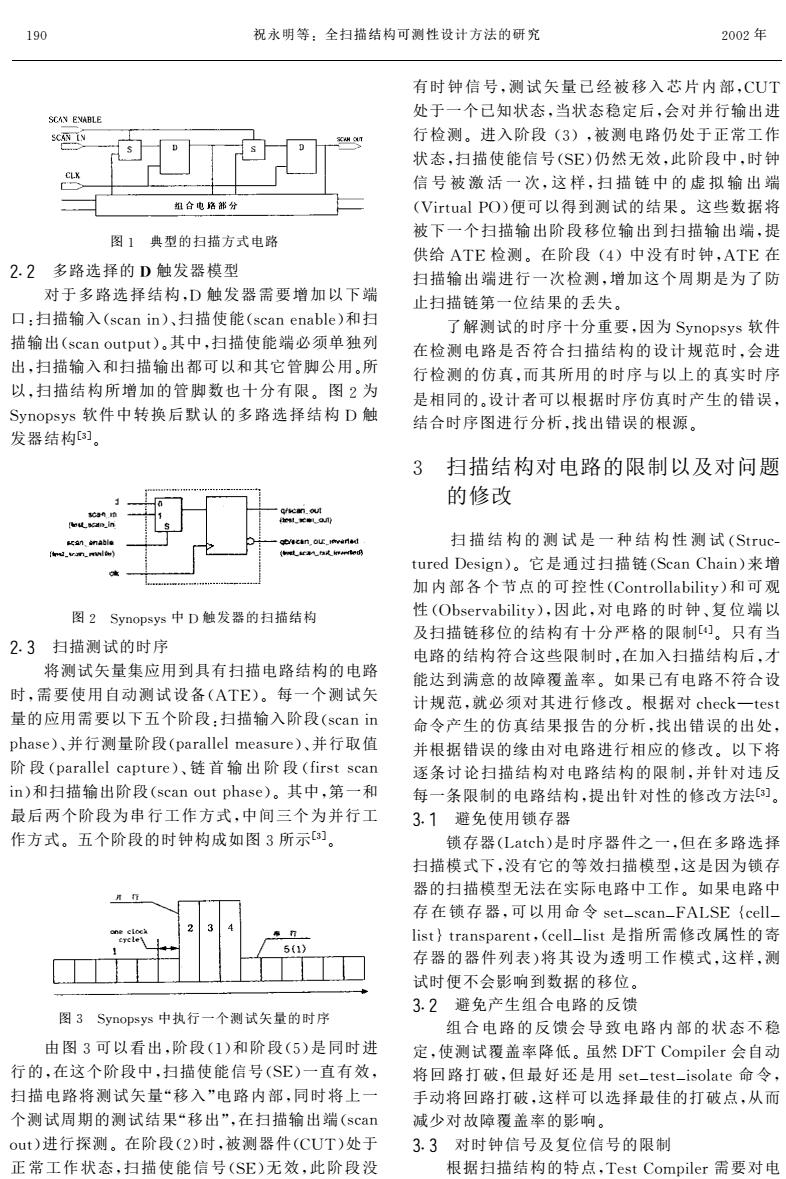

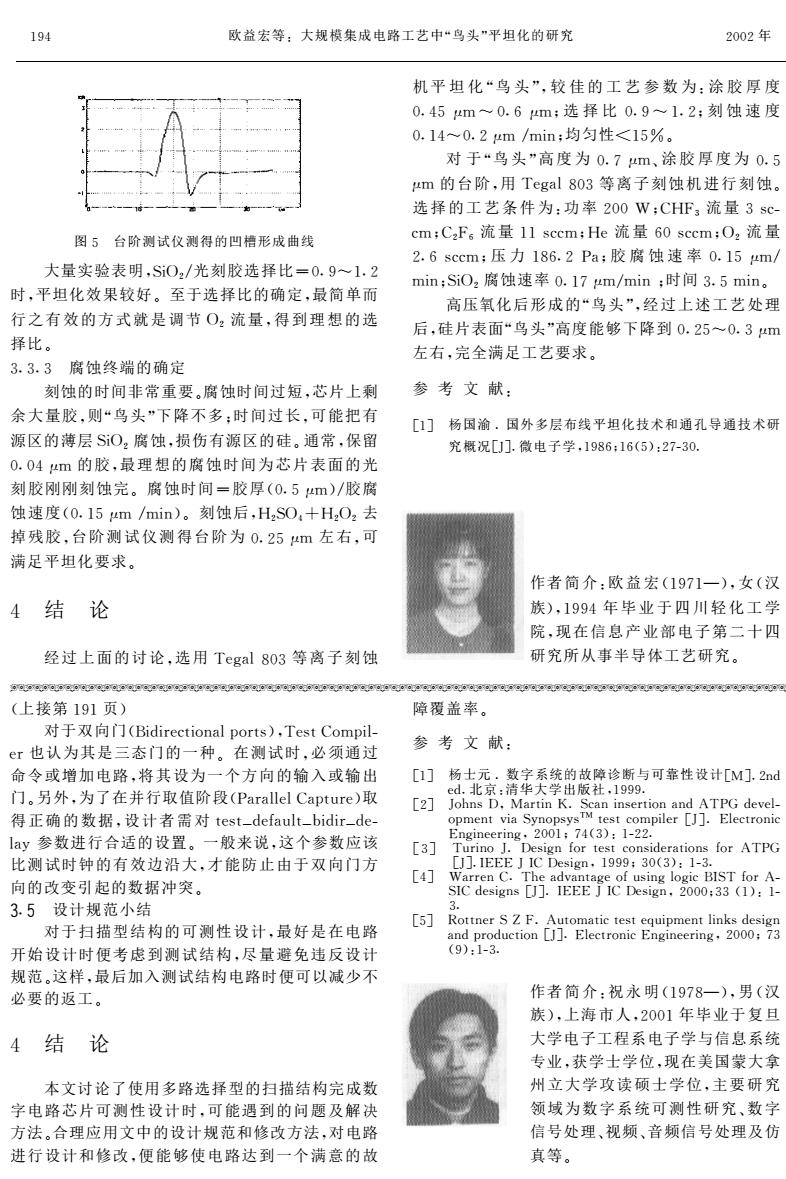

190 祝永明等:全扫描结构可测性设计方法的研究 2002年 有时钟信号,测试矢量已经被移入芯片内部,CUT 处于一个已知状态,当状态稳定后,会对并行输出进 SCAN ENABLE SCAN IN 行检测。进入阶段(3),被测电路仍处于正常工作 状态,扫描使能信号(SE)仍然无效,此阶段中,时钟 信号被激活一次,这样,扫描链中的虚拟输出端 组合电路部分 (Virtual PO)便可以得到测试的结果。这些数据将 图1典型的扫描方式电路 被下一个扫描输出阶段移位输出到扫描输出端,提 供给ATE检测。在阶段(4)中没有时钟,ATE在 2.2多路选择的D触发器模型 扫描输出端进行一次检测,增加这个周期是为了防 对于多路选择结构,D触发器需要增加以下端 止扫描链第一位结果的丢失。 口:扫描输入(scan in)、扫描使能(scan enable)和扫 了解测试的时序十分重要,因为Synopsys软件 描输出(scan output)。其中,扫描使能端必须单独列 在检测电路是否符合扫描结构的设计规范时,会进 出,扫描输入和扫描输出都可以和其它管脚公用。所 行检测的仿真,而其所用的时序与以上的真实时序 以,扫描结构所增加的管脚数也十分有限。图2为 是相同的。设计者可以根据时序仿真时产生的错误, Synopsys软件中转换后默认的多路选择结构D触 结合时序图进行分析,找出错误的根源。 发器结构]。 3 扫描结构对电路的限制以及对问题 的修改 can.out ecan.ou_imarad 扫描结构的测试是一种结构性测试(Struc tured Design)。它是通过扫描链(Scan Chain)来增 加内部各个节点的可控性(Controllability)和可观 图2 Synopsys中D触发器的扫描结构 性(Observability),因此,对电路的时钟、复位端以 及扫描链移位的结构有十分严格的限制)。只有当 2.3扫描测试的时序 电路的结构符合这些限制时,在加入扫描结构后,才 将测试矢量集应用到具有扫描电路结构的电路 能达到满意的故障覆盖率。如果已有电路不符合设 时,需要使用自动测试设备(ATE)。每一个测试矢 计规范,就必须对其进行修改。根据对check一test 量的应用需要以下五个阶段:扫描输入阶段(scan in 命令产生的仿真结果报告的分析,找出错误的出处, phase)、并行测量阶段(parallel measure)、并行取值 并根据错误的缘由对电路进行相应的修改。以下将 阶段(parallel capture)、链首输出阶段(first scan 逐条讨论扫描结构对电路结构的限制,并针对违反 in)和扫描输出阶段(scan out phase)。其中,第一和 每一条限制的电路结构,提出针对性的修改方法[] 最后两个阶段为串行工作方式,中间三个为并行工 3.1避免使用锁存器 作方式。五个阶段的时钟构成如图3所示3们。 锁存器(Latch)是时序器件之一,但在多路选择 扫描模式下,没有它的等效扫描模型,这是因为锁存 器的扫描模型无法在实际电路中工作。如果电路中 存在锁存器,可以用命令set-scan-FALSE{cell 原力 list}transparent,(cell_ist是指所需修改属性的寄 5(1) 存器的器件列表)将其设为透明工作模式,这样,测 试时便不会影响到数据的移位。 3.2避免产生组合电路的反馈 图3 Synopsys中执行一个测试矢量的时序 组合电路的反馈会导致电路内部的状态不稳 由图3可以看出,阶段(1)和阶段(5)是同时进 定,使测试覆盖率降低。虽然DFT Compiler会自动 行的,在这个阶段中,扫描使能信号(SE)一直有效, 将回路打破,但最好还是用set-test-isolate命令, 扫描电路将测试矢量“移入”电路内部,同时将上一 手动将回路打破,这样可以选择最佳的打破点,从而 个测试周期的测试结果“移出”,在扫描输出端(scan 减少对故障覆盖率的影响。 out)进行探测。在阶段(2)时,被测器件(CUT)处于 3.3对时钟信号及复位信号的限制 正常工作状态,扫描使能信号(SE)无效,此阶段没 根据扫描结构的特点,Test Compiler需要对电

图 ! 典型的扫描方式电路 "#" 多路选择的 $触发器模型 对于多路选择结构%&触发器需要增加以下端 口’扫描输入()*+,-,./扫描使能()*+,0,+120.和扫 描输出()*+,345645.7其中%扫描使能端必须单独列 出%扫描输入和扫描输出都可以和其它管脚公用7所 以%扫描结构所增加的管脚数也十分有限7图 8为 9:,36):)软件中转换后默认的多路选择结构 &触 发器结构; 扫描测试的时序 将测试矢量集应用到具有扫描电路结构的电路 时%需要使用自动测试设备(?@A.7每一个测试矢 量的应用需要以下五个阶段’扫描输入阶段()*+,-, 6B+)0./并行测量阶段(6+C+2202D0+)4C0./并行取值 阶 段 (6+C+2202*+654C0./链 首 输 出 阶 段 (E-C)5)*+, -,.和扫描输出阶段()*+,3456B+)0.7其中%第一和 最后两个阶段为串行工作方式%中间三个为并行工 作方式7五个阶段的时钟构成如图 #U 避免使用锁存器 锁存器(V+5*B.是时序器件之一%但在多路选择 扫描模式下%没有它的等效扫描模型%这是因为锁存 器的扫描模型无法在实际电路中工作7如果电路中 存 在 锁 存 器%可 以 用 命 令 )05W )*+,W X?V9AY*022W 2-)5Z5C+,)6+C0,5%(*022W 2-)5是指所需修改属性的寄 存器的器件列表.将其设为透明工作模式%这样%测 试时便不会影响到数据的移位7 >#" 避免产生组合电路的反馈 组 合 电 路 的 反 馈 会 导 致 电 路 内 部 的 状 态 不 稳 定%使测试覆盖率降低7虽然 &X@I3D6-20C会自动 将 回 路 打 破%但 最 好 还 是 用 )05W 50)5W -)32+50命 令% 手动将回路打破%这样可以选择最佳的打破点%从而 减少对故障覆盖率的影响7 >#> 对时钟信号及复位信号的限制 根据扫描结构的特点%@0)5I3D6-20C需要对电

第3期 祝永明等:全扫描结构可测性设计方法的研究 191 路内部的状态有完全的控制。因此,它必须对电路内 起来,达到满意的故障覆盖率。下面是进行多重通 部所有的时钟和使能端都有完整的控制。当任何器 过ATPG的Script] 0 件的使能端或时钟端无法被控制时,它便会被排除 例1 在扫描链之外,使故障覆盖率大大降低。有关时钟及 multi_pass-test-generation=true 复位端的问题和修改有以下几种。 ∥设置多重通过ATPG属性 3.3.1不可控的时钟端和复位端 create-test-clock-period 100\ 不可控的时钟端和复位端包括非同步复位端 ∥设置第一个时钟 (Asynchronous Reset)、时钟前有逻辑门(Gated -waveform(45,55)clk Clock)、时钟前有时序逻辑等,所有不可控的时钟端 ∥上升沿为45,下降沿为55 和复位端。基本思路是,增加一部分逻辑电路和一个 check_test 扫描工作模式使能端(TM),当扫描工作模式使能 create-test-patterns -out passl 端值为真时,电路进入扫描工作模式。这种模式下, ∥第一次产生测试矢量集 可以将有问题的部分或端口旁路掉,使扫描正常进 create_test_clock -period 100\ 行。此方法可以用在几乎所有的问题上,也是在实际 ∥设置第二个时钟 设计中应用最广泛的方法,但它需要比较多的人工 干预,因而需要较多的时间。图4分别对不可控时钟 -waveform (55,45)clk 和复位端进行了修改。 ∥上升沿为55,下降沿为55 check-test create-test-patterns -out pass2 ∥第二次产生测试矢量集 multi-pass-test-generation=false ∥取消多重通过ATPG属性 (a) 3.3.3避免多重时钟 如果一个电路既有外部时钟,又有内部时钟,便 有可能在扫描测试时产生竞争与冒险。解决方法是 手工将不同的时钟区域(Clock domain)划分到不同 的扫描链中。下面是一个例子。 (b) 例2 图4(a)对不可控时钟端进行的修改 create_clock -name clockl -p 100\ (b)对不可控复位端进行的修改 ∥定义第一个时钟区域 图4(a)中,在不可控时钟前加了一个二路选择 find{port,“clk"} 器,当testmode有效时,便可将原时钟旁路掉,改由 create_clock -name clock2 -p 100 系统的测试时钟cock来控制。图4(b)中,在不可控 ∥定义第二个时钟区域 复位端前加了一个或门,当testmode有效时,原来 find(port,"clk_inst/DIV_CLK") set_scan-path pathl all_registers\ 的复位信号被或门屏蔽掉,不会再对时序器件产生 ∥设定第一个时钟区域的扫描链 影响。以上修改只能在HDL源文件中进行。实行上 (-edge-triggered -clock clock1) 述修改后,在测试前,执行set-test-hold1test- -complete trueset-scan-path path2 mode命令,能使所加入的部分产生效果。 ∥设定剩下时钟区域的扫描链 3.3.2多重时钟沿 3.4对三态总线的限制 如果在同一电路中,既用到时钟的上升沿又用 内部三态总线往往会导致扫描阶段时内部总线 到下降沿,那么在CHECK_TEST时便会产生警 冲突,使扫描结构变得不能实施。Test compiler不 告。解决的方法是应用多重通过(Multi Pass) 会自动地对三态总线进行处理,需要人工确定在扫 ATPG。在多重通过的ATPG过程中,必须设置两 描时不会出现冲突,这要花费很多的人力,有时甚 次时钟波形,并进行两次测试矢量集的自动生成 是不可能的。 (ATPG),DFT Compiler会自动把两次的结果结合 (下转第194页)

路内部的状态有完全的控制!因此"它必须对电路内 部所有的时钟和使能端都有完整的控制!当任何器 件的使能端或时钟端无法被控制时"它便会被排除 在扫描链之外"使故障覆盖率大大降低!有关时钟及 复位端的问题和修改有以下几种! #$#$% 不可控的时钟端和复位端 不 可 控 的 时 钟 端 和 复 位 端 包 括 非 同 步 复 位 端 &’()*+,-.*./(01(1234时 钟 前 有 逻 辑 门 &56217 89.+:34时钟前有时序逻辑等"所有不可控的时钟端 和复位端!基本思路是"增加一部分逻辑电路和一个 扫 描工作模式使能端&;3 图 = &63对不可控时钟端进行的修改 &>3对不可控复位端进行的修改 图 =&63中"在不可控时钟前加了一个二路选择 器"当 21(2?.71有效时"便可将原时钟旁路掉"改由 系统的测试时钟 +9.+:来控制!图 =&>3中"在不可控 复位端前加了一个或门"当 21(2?.71有 效 时"原 来 的复位信号被或门屏蔽掉"不会再对时序器件产生 影响!以上修改只能在 @AB源文件中进行!实行上 述 修 改 后"在 测 试 前"执 行 (12C 21(2C ,.97%21(2D ?.71命令"能使所加入的部分产生效果! #$#$E 多重时钟沿 如果在同一电路中"既用到时钟的上升沿又用 到 下 降 沿"那 么 在 8@F8GC ;FH; 时 便 会 产 生 警 告!解 决 的 方 法 是 应 用 多 重 通 过 &</92IJ6((3 ’;J5!在多重通过的 ’;J5过程中"必须设置两 次 时 钟 波 形"并 进 行 两 次 测 试 矢 量 集 的 自 动 生 成 &’;J53"AK;8.?LI91-会自动把两次的结果结合 起来"达到满意的故障覆盖率!下面是进行多重通 过 ’;J5的 H+-IL2M#N! 例 O ?/92IC L6((C 21(2C P1*1-62I.*Q2-/1 R设置多重通过 ’;J5属性 +-1621C 21(2C +9.+:DL1-I.7%SST R设置第一个时钟 DU6V1W.-?X=Y"YYZ+9: R上升沿为 =Y"下降沿为 YY +,1+:C 21(2 +-1621C 21(2C L6221-*(D./2L6((9 R第一次产生测试矢量集 +-1621C 21(2C +9.+:DL1-I.7%SST R设置第二个时钟 DU6V1W.-? XYY"=YZ+9: R上升沿为 YY"下降沿为 YY +,1+:C 21(2 +-1621C 21(2C L6221-*(D./2L6((E R第二次产生测试矢量集 ?/92IC L6((C 21(2C P1*1-62I.*QW69(1 R取消多重通过 ’;J5属性 #[#[# 避免多重时钟 如果一个电路既有外部时钟"又有内部时钟"便 有可能在扫描测试时产生竞争与冒险!解决方法是 手工将不同的时钟区域&89.+:7.?6I*3划分到不同 的扫描链中!下面是一个例子! 例 \ +-1621C +9.+:D*6?1+9.+:%DL%SST R定义第一个时钟区域 WI*7XL.-2"]+9:^Z +-1621C +9.+:D*6?1+9.+:EDL%SST R定义第二个时钟区域 WI*7XL.-2"]+9:C I*(2_A‘aC 8BG^Z (12C (+6*C L62,L62,%699C -1PI(21-(T R设定第一个时钟区域的扫描链 XD17P1C 2-IPP1-17D+9.+:+9.+:%ZT D+.?L91212-/1(12C (+6*C L62,L62,E R设定剩下时钟区域的扫描链 b$c 对三态总线的限制 内部三态总线往往会导致扫描阶段时内部总线 冲突"使扫描结构变得不能实施!;1(2+.?LI91-不 会自动地对三态总线进行处理"需要人工确定在扫 描时不会出现冲突"这要花费很多的人力"有时甚至 是不可能的! &下转第 %d=页3 第 #期 祝永明等e全扫描结构可测性设计方法的研究 %d%

194 欧益宏等:大规模集成电路工艺中“鸟头”平坦化的研究 2002年 机平坦化“鸟头”,较佳的工艺参数为:涂胶厚度 0.45m~0.6m;选择比0.9~1.2:刻蚀速度 0.14~0.2m/min;均匀性<15%。 对于“鸟头”高度为0.7m、涂胶厚度为0.5 um的台阶,用Tegal803等离子刻蚀机进行刻蚀。 选择的工艺条件为:功率200W;CHF3流量3sc 图5台阶测试仪测得的凹槽形成曲线 cm;C2F。流量11sccm;He流量60sccm;O2流量 2.6sccm;压力186.2Pa;胶腐蚀速率0.15m/ 大量实验表明,SiO2/光刻胶选择比=0.9~1.2 min;SiO2腐蚀速率0.17m/min;时间3.5min。 时,平坦化效果较好。至于选择比的确定,最简单而 高压氧化后形成的“鸟头”,经过上述工艺处理 行之有效的方式就是调节O2流量,得到理想的选 后,硅片表面“鸟头”高度能够下降到0.25~0.3m 择比。 左右,完全满足工艺要求。 3.3.3腐蚀终端的确定 刻蚀的时间非常重要。腐蚀时间过短,芯片上剩 参考文献: 余大量胶,则“鸟头”下降不多:时间过长,可能把有 [1]杨国渝.国外多层布线平坦化技术和通孔导通技术研 源区的薄层SO2腐蚀,损伤有源区的硅。通常,保留 究概况[].微电子学,1986:16(5):27-30. 0.04m的胶,最理想的腐蚀时间为芯片表面的光 刻胶刚刚刻蚀完。腐蚀时间=胶厚(0.5m)/胶腐 蚀速度(0.15m/min)。刻蚀后,HzSO,十H2O2去 掉残胶,台阶测试仪测得台阶为0.25m左右,可 满足平坦化要求。 作者简介:欧益宏(1971一),女(汉 4结论 族),1994年毕业于四川轻化工学 院,现在信息产业部电子第二十四 经过上面的讨论,选用Tegal803等离子刻蚀 研究所从事半导体工艺研究。 50990@8400300@8@000@00c0@080800808408500@900900090809000@0908000@0080@0940038@098@098@080@09g000@000@000@ (上接第191页) 障覆盖率。 对于双向门(Bidirectional ports),Test Compil-- er也认为其是三态门的一种。在测试时,必须通过 参考文献: 命令或增加电路,将其设为一个方向的输入或输出 [1]杨士元.数字系统的故障诊断与可靠性设计[M].2nd 门。另外,为了在并行取值阶段(Parallel Capture)取 ed.北京:清华大学出版社,1999. [2]Johns D,Martin K.Scan insertion and ATPG devel- 得正确的数据,设计者需对test-default_bidir.-de- opment via SynopsysTM test compiler [J].Electronic lay参数进行合适的设置。一般来说,这个参数应该 Engineering,2001;74(3):1-22. [3] Turino J.Design for test considerations for ATPG 比测试时钟的有效边沿大,才能防止由于双向门方 [].1 EEE J IC Design,1999:30(3):1-3. [4] 向的改变引起的数据冲突。 Warren C.The advantage of using logic BIST for A- SIC designs [J].IEEE J IC Design.2000:33 (1):1- 3.5设计规范小结 3. [5] Rottner S Z F.Automatic test equipment links design 对于扫描型结构的可测性设计,最好是在电路 and production [J].Electronic Engineering,2000;73 开始设计时便考虑到测试结构,尽量避免违反设计 (9):1-3. 规范。这样,最后加入测试结构电路时便可以减少不 必要的返工。 作者简介:祝永明(1978一),男(汉 族),上海市人,2001年毕业于复旦 4结论 大学电子工程系电子学与信息系统 专业,获学士学位,现在美国蒙大拿 本文讨论了使用多路选择型的扫描结构完成数 州立大学攻读硕士学位,主要研究 字电路芯片可测性设计时,可能遇到的问题及解决 领域为数字系统可测性研究、数字 方法。合理应用文中的设计规范和修改方法,对电路 信号处理、视频、音频信号处理及仿 进行设计和修改,便能够使电路达到一个满意的故 真等

图 ! 台阶测试仪测得的凹槽形成曲线 大量实验表明"#$%&’光刻胶选择比()*+,-*& 时"平坦化效果较好.至于选择比的确定"最简单而 行 之 有 效 的 方 式 就 是 调 节 %&流 量"得 到 理 想 的 选 择比. /*/*/ 腐蚀终端的确定 刻蚀的时间非常重要.腐蚀时间过短"芯片上剩 余大量胶"则0鸟头1下降不多2时间过长"可能把有 源区的薄层 #$%&腐蚀"损伤有源区的硅.通常"保留 )*)345的胶"最理想的腐蚀时间为芯片表面的光 刻 胶刚刚刻蚀完.腐蚀时间(胶厚6)*!457’胶腐 蚀 速度6)*-!45 ’5$87.刻蚀后"9&#%3:9&%&去 掉 残 胶"台 阶 测 试 仪 测 得 台 阶 为 )*&!45 左 右"可 满足平坦化要求. 3 结 论 经 过 上 面 的 讨 论"选 用 ;?@)/等 离 子 刻 蚀 机 平 坦 化 0鸟 头1"较 佳 的 工 艺 参 数 为A涂 胶 厚 度 )*3!45, )*B452选 择 比 )*+, -*&2刻 蚀 速 度 )*-3,)*&45 ’5$82均匀性C-!D. 对 于 0鸟 头1高 度 为 )*E45F涂 胶 厚 度 为 )*! 45 的台阶"用 ;?@)/等离子刻蚀 机 进 行 刻 蚀. 选 择 的 工 艺 条 件 为A功 率 &))G2H9I/流 量 /JKL K52H&IB流 量 --JKK5292胶 腐 蚀 速 率 )*-!45’ 5$82#$%&腐蚀速率 )*-E45’5$82时间 /*!5$8. 高压氧化后形成的0鸟头1"经过上述工艺处理 后"硅片表面0鸟头1高度能够下降到 )*&!,)*/45 左右"完全满足工艺要求. 参 考 文 献A N-O 杨国渝 *国外多层布线平坦化技术和通孔导通技术研 究概况NPOQ微电子学"-+@B2-B6!7A&EL/)Q 作者 简 介A欧 益 宏6-+E-R7"女6汉 族7"-++3年 毕 业 于 四 川 轻 化 工 学 院"现在信息产业部电子第二 十 四 研究所从事半导体工艺研究 SSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSSS . 6上接第 -+-页7 对于双向门6T$U$V?YXVWJ7";V>??YWZVZ?WR \$U$VR U]参数进行合适的设置.一般来说"这个参数应该 比测试时钟的有效边沿大"才能防止由于双向门方 向的改变引起的数据冲突. ^*_ 设计规范小结 对于扫描型结构的可测性设计"最好是在电路 开始设计时便考虑到测试结构"尽量避免违反设计 规范.这样"最后加入测试结构电路时便可以减少不 必要的返工. 3 结 论 本文讨论了使用多路选择型的扫描结构完成数 字电路芯片可测性设计时"可能遇到的问题及解决 方法.合理应用文中的设计规范和修改方法"对电路 进行设计和修改"便能够使电路达到一个满意的故 障覆盖率. 参 考 文 献A N-O 杨士元 *数字系统的故障诊断与可靠性设计N‘OQ&8U VW$8c*#K>8$8J8Ud;Me U#]8XYJ]J;‘ WW$X8J[XVd;Me NPOQhgggPhHbVVUf>8W>=W$KW8UYVXUZKW$X8NPO*g?<KWVX8$Kg8=$8<<V$8="&)))2E/ 6+7A-L/* 作者 简 介A祝 永 明6-+E@R7"男6汉 族7"上海市人"&))-年毕业于复旦 大学电子工程系电子学与信息系统 专业"获学士学位"现在美国蒙大拿 州立大学攻读硕士学位"主要 研 究 领域为数字系统可测性研究F数 字 信号处理F视频F音频信号处理及仿 真等. -+3 欧益宏等A大规模集成电路工艺中0鸟头1平坦化的研究 &))&年