第34卷第1期 微电子学 Vol.34,01 2004年2月 M icroelectronics Feb.2004 文章编号:1004-3365(2004)01-0056-04 ASC综合后的静态验证方法的研究 舒适,唐长文,闵昊 (复旦大学专用集成电路系统与设计国家重点实验室,上海200433) 摘要:介绍了基于深亚微米QMOS工艺ASC电路设计流程中的静态验证方法。将这种验证方 法与以往的动态验证方法进行了比较,结果表明,前者比后者更加高效和准确。由此可以说明,静态 验证完全可以取代动态验证,并且静态验证比动态验证更加适合超大规模集成电路的发展趋势。 关键词:专用集成电路,电路综合,静态验证静态时序分析,形式验证 中图分类号:TN492 文献标识码A A Study on the Static Ver if ication M ethodology for Syn thesized ASIC Design SHU Shi,TAN G Zhangwen,M N Hao (S tate Key L aboratory of A SIC Systen,Fudan University,Shanghai 200433,P.R.China) Abstract A static verification methodobgy for circuit design-fbw of ASIC's based on very deep subm icron CMOS technobgy is described in the paper.A comparison of the static verification methodobgy w ith the dynam ic verification methodobgy indicates that the fomer is more efficient and more accurate than the latter.It has been shown that the static verificaton,w hich is a substitute for dynam ic verificaton,ismore suitable for VLSI's Key words ASC;Circuit synthesis Static verificaton;Static tm ing analysis Fomal verificaton EEACC:2570D 唯一的方法是用动态验证工具进行验证。动态验证 1 引言 的最大缺点在于验证时间很长,而且动态验证是对 特殊情况的验证,其验证结果正确只能说明在这种 随着深亚微米技术的发展,数字电路的规模己 TestBench RTL仿真 HRT级代码 Reference 经发展到上百万门。未来的二十多年里,一块ASC 7 芯片中将会达到上千万门的规模。这样的电路规模 结构优化 做验证的时间在整个芯片的开发周期所占的比例会 越来越重。通常,在做验证的时候,我们都会采用动 RTL级代码 态验证的方法。现在,用静态验证方法不仅能够完成 Synthesis Constraints 综合并优化 验证的工作,而且还能大大地节省验证所需要的时 间。 静态时序分析 门级网表 深亚微米工艺下的ASC设计流程如图1所示。 Timing floor-plan 设计流程可以分为以下几个主要的部分:整体设计, Constraints 布局布线 设计实现,设计验证和流片封装。流片失败70%是功 静态时序分析 物理层网表 能出错造成的),所以,设计验证是保证设计电路功 能正确的关键步骤。 DRC&LVS 2静态时序分析与形式验证 流片 (Sign-off) 在静态时序分析和形式验证的方法出现以前, 图1ASC设计流程 收稿日期2003-01-20,定稿日期2003-03-12 C1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

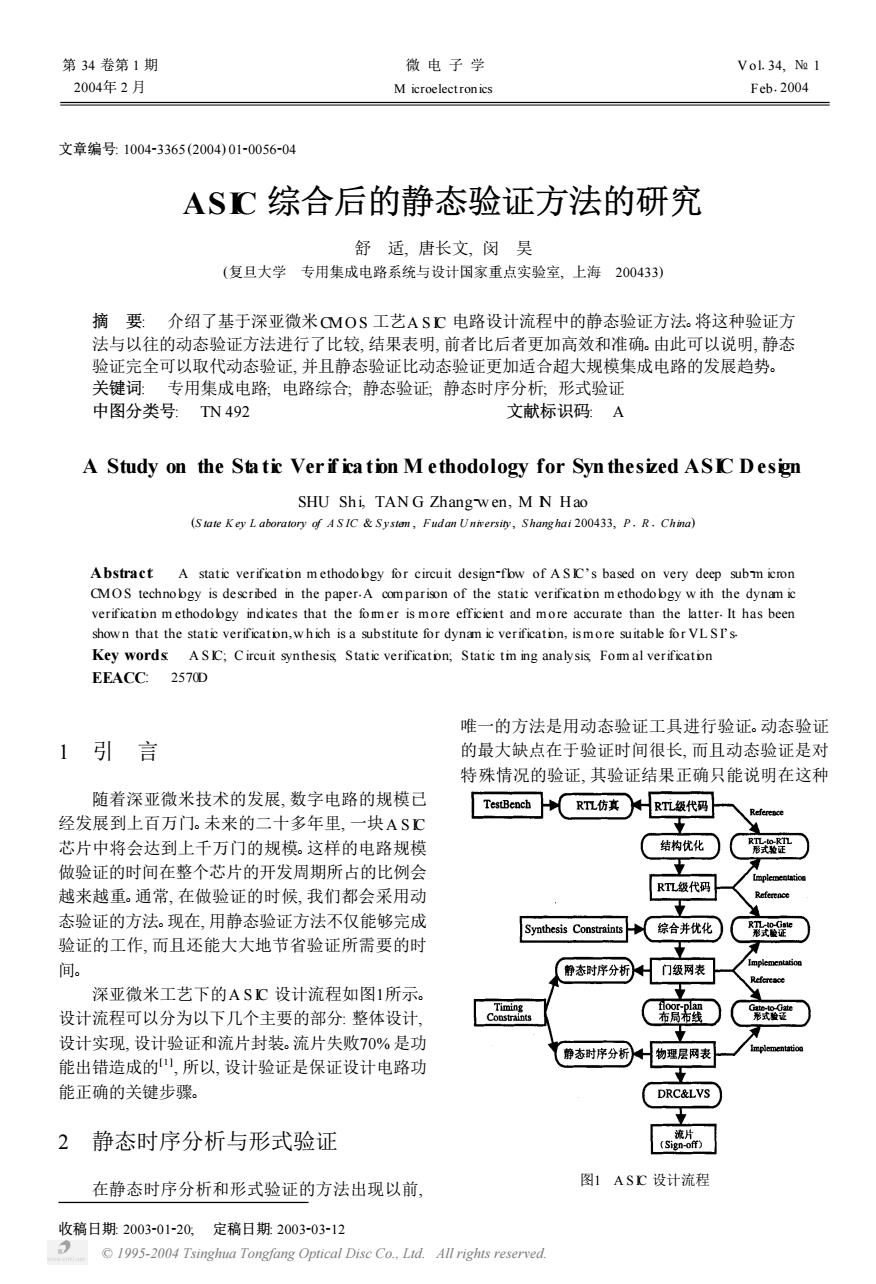

收稿日期: 2003201220; 定稿日期: 2003203212 文章编号: 100423365 (2004) 0120056204 ASIC 综合后的静态验证方法的研究 舒 适, 唐长文, 闵 昊 (复旦大学 专用集成电路系统与设计国家重点实验室, 上海 200433) 摘 要: 介绍了基于深亚微米CM O S 工艺A S IC 电路设计流程中的静态验证方法。将这种验证方 法与以往的动态验证方法进行了比较, 结果表明, 前者比后者更加高效和准确。由此可以说明, 静态 验证完全可以取代动态验证, 并且静态验证比动态验证更加适合超大规模集成电路的发展趋势。 关键词: 专用集成电路; 电路综合; 静态验证; 静态时序分析; 形式验证 中图分类号: TN 492 文献标识码: A A Study on the Sta tic Ver if ica tion M ethodology for Syn thesized ASIC D esign SHU Sh i, TAN G Zhang2w en, M IN H ao (S tate K ey L aboratory of A S IC & S y stem , Fud an U niversity , S hanghai 200433, P 1 R 1 China) Abstract: A static verification m ethodology for circuit design2flow of A S IC’s based on very deep sub2m icron CM O S technology is described in the paper1A comparison of the static verification m ethodology w ith the dynam ic verification m ethodology indicates that the form er is more efficient and more accurate than the latter1It has been show n that the static verification,w h ich is a substitute for dynam ic verification, ismore suitable for VL S I’s1 Key words: A S IC; C ircuit synthesis; Static verification; Static tim ing analysis; Form al verification EEACC: 2570D 1 引 言 随着深亚微米技术的发展, 数字电路的规模已 经发展到上百万门。未来的二十多年里, 一块A S IC 芯片中将会达到上千万门的规模。这样的电路规模 做验证的时间在整个芯片的开发周期所占的比例会 越来越重。通常, 在做验证的时候, 我们都会采用动 态验证的方法。现在, 用静态验证方法不仅能够完成 验证的工作, 而且还能大大地节省验证所需要的时 间。 深亚微米工艺下的A S IC 设计流程如图1所示。 设计流程可以分为以下几个主要的部分: 整体设计, 设计实现, 设计验证和流片封装。流片失败70% 是功 能出错造成的[ 1 ] , 所以, 设计验证是保证设计电路功 能正确的关键步骤。 2 静态时序分析与形式验证 在静态时序分析和形式验证的方法出现以前, 唯一的方法是用动态验证工具进行验证。动态验证 的最大缺点在于验证时间很长, 而且动态验证是对 特殊情况的验证, 其验证结果正确只能说明在这种 图1 A S IC 设计流程 第 34 卷第 1 期 2004年 2 月 微 电 子 学 M icroelect ronics V ol134, № 1 Feb12004 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

第1期 舒适等:ASC综合后的静态验证方法的研究 57 特定条件下的功能正确,不能据此说明电路一定没 度、工作电压、输入充放电速度、输出扇出大小。我们 有功能错误。在提出静态时序分析和形式验证的概 可以通过对实际电路进行测试,从测试得到的数据 念后,我们可以用静态验证代替动态验证。静态验证 分析计算器件的延时信息,这样就可以预测出电路 的方法是把时序验证和逻辑功能验证分开来做,不 在实际实现后会出现的延时信息。不同的厂商提供 需要加任何激励。这样做可以大大节省验证时间。 的库文件中己经包含了器件的延时信息,做静态时 静态时序分析是判断电路中所有单元是否满足 序分析的时候调用这些库文件,分析和检查设计电 时序要求。静态时序分析检查设计中电路每一条通 路各个路径的建立时间和保持时间是否满足时序要 路的时序信息,看是否有时序错误。静态时序分析不 求,是否有违反设计规则的地方。 检查电路的逻辑功能,所以,在做完电路的时序验证 DATA 后,还必须做形式验证。 CLK 形式验证不考虑设计电路的时序问题,它只比 数据输入 较两个电路的功能是否一致。形式验证不需要加激 线上RC延时 输出负载延时 励。因此,如果RTL级电路动态验证正确的前提条 件成立,那么,只要通过形式验证,就能保证后者的 图2电路器件延时模型 电路功能没有错误。 有了器件的模型,就可以用STA的工具做电路 比较动态验证和静态验证,后者的优点在于:1) 的静态时序分析。STA主要分为两个阶段,第一个 运行时间短:2)覆盖率为100%;3)通过错误分析报 阶段是在布局布线前,第二个阶段是在布局布线后。 告,比较容易找到出错处。 这两个阶段的主要区别在于:后者有具体的连线长 下面,我们着重就后一种验证方法进行具体的 度、宽度、信号分布情况等信息,所以,后者可以更加 描述。 准确地估计线上延时,以及时钟树的延时,而前者只 能根据设计电路面积的大小,估计线上延时和时钟 3ASC中的静态时序分析 树的延时。 STA的工具有Synopsys公司的Prmetme, 在设计ASC芯片的时候,设计者除了要考虑 Cadence公司的Pearl,等等。静态时序分析工具可以 如何按照要求设计出正确的电路外,还要考虑设计 对设计电路进行以下几种分析 电路在物理层实现后,原本在RTL级正确的逻辑关 a)从主要的输入端口到电路中所有触发器: 系是否还会保证不出错。因此,设计者需要能够精确 b)从触发器到触发器: 描述器件特性的器件模型。这些器件模型要和实际 c)从触发器到主要输出端口; 器件的工作情况相同,当用这些器件模型做设计电 d)从主要的输入端口到主要的输出端口。 路验证时,电路的工作情况就和实际设计出来的芯 静态时序分析工具把整个设计电路打散成上述 片的工作情况相同。 四种类型的时序路径,分析不同路径的时序信息,得 建立一个用器件模型搭出的简单电路,如图2所 到建立时间和保持时间的计算结果。这里有必要介 示。从图中可以看出造成电路延时的四种因素。数据 绍一下这两个参数的含义,因为静态时序分析的精 输入跳变延时取决于D触发器输入瑞充放电的速 髓就在于判断和分析这两个参数的结果。 度和输入端RC负载的大小,输入数据跳变越频繁, 如图3所示),数据从触发器FF1的D端进入, 延时就越长,门延时由D触发器自身RC负载大小 传到触发器FF2的Q端输出,这是一个最基本的时 和充放电速度决定,线上RC延时则由D触发器的 序路径,而且这两个触发器都是用同一个时钟驱动。 输出驱动能力和线上RC的负载大小决定,连线越 首先分析Setup check。假设在tme=O的时候, 长,负载越大,驱动时间越长,输出负载只是增加D FF1的第一个上升沿时钟使得FF1获得D端的数 触发器输出驱动的负荷量,输出接负载的门数越多, 据,那么,数据到达FF2的D端的时间一定要比FF2 输出数据的延时时间就越长。这些延时是基于不同 的第二个上升沿时钟到达FF2的CLK端的时间要 的QMOS工艺和具体电路的布局布线。在特定的工 短。如果预定的Setuptme V platon的尺度为“o” 艺条件和工作环境下,影响器件充放电速度和自身 要求数据到达的时间就必须小于10ns,否则,时序 RC负载的因素有器件的面积、密度、参杂密度、温 分析结果就会报setup ti e的V platon。Setuptime C1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

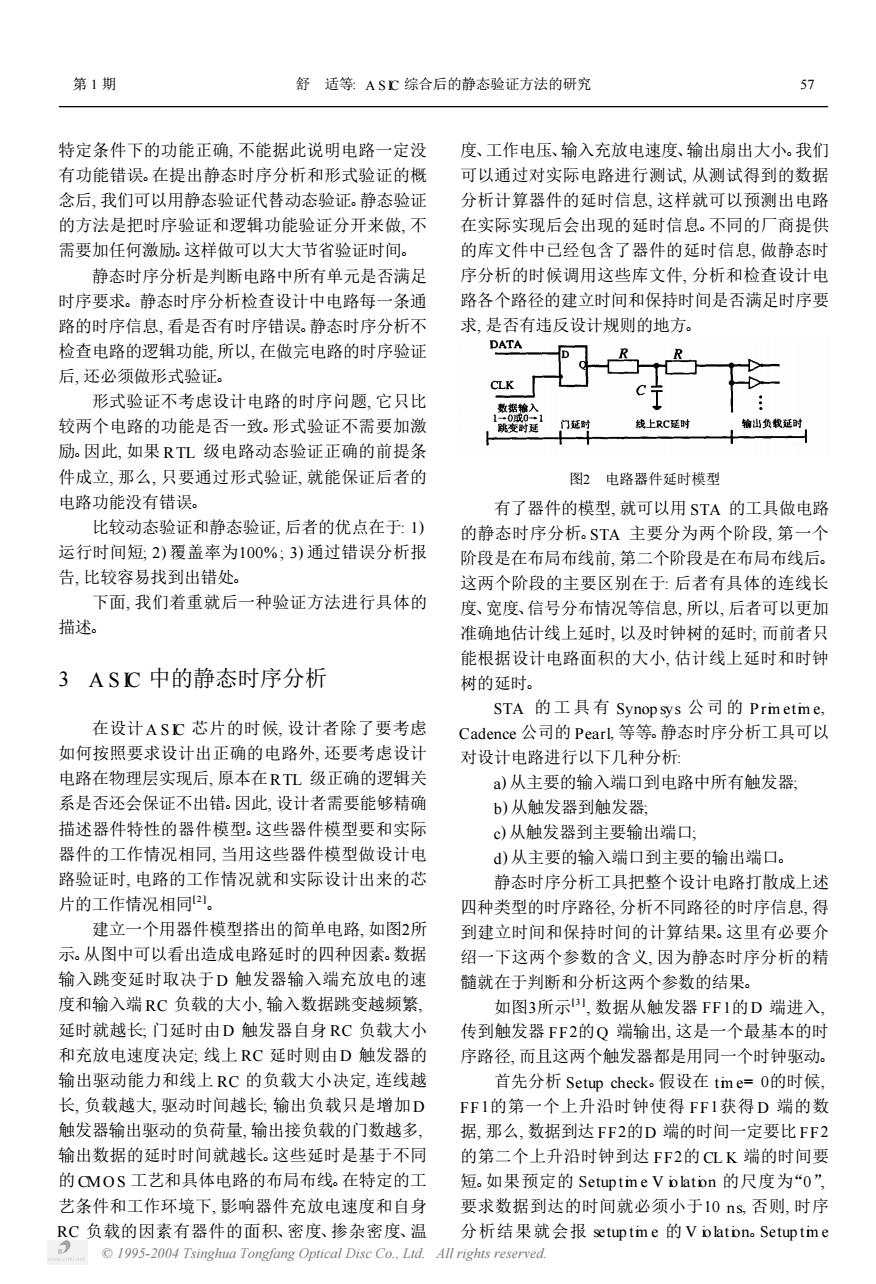

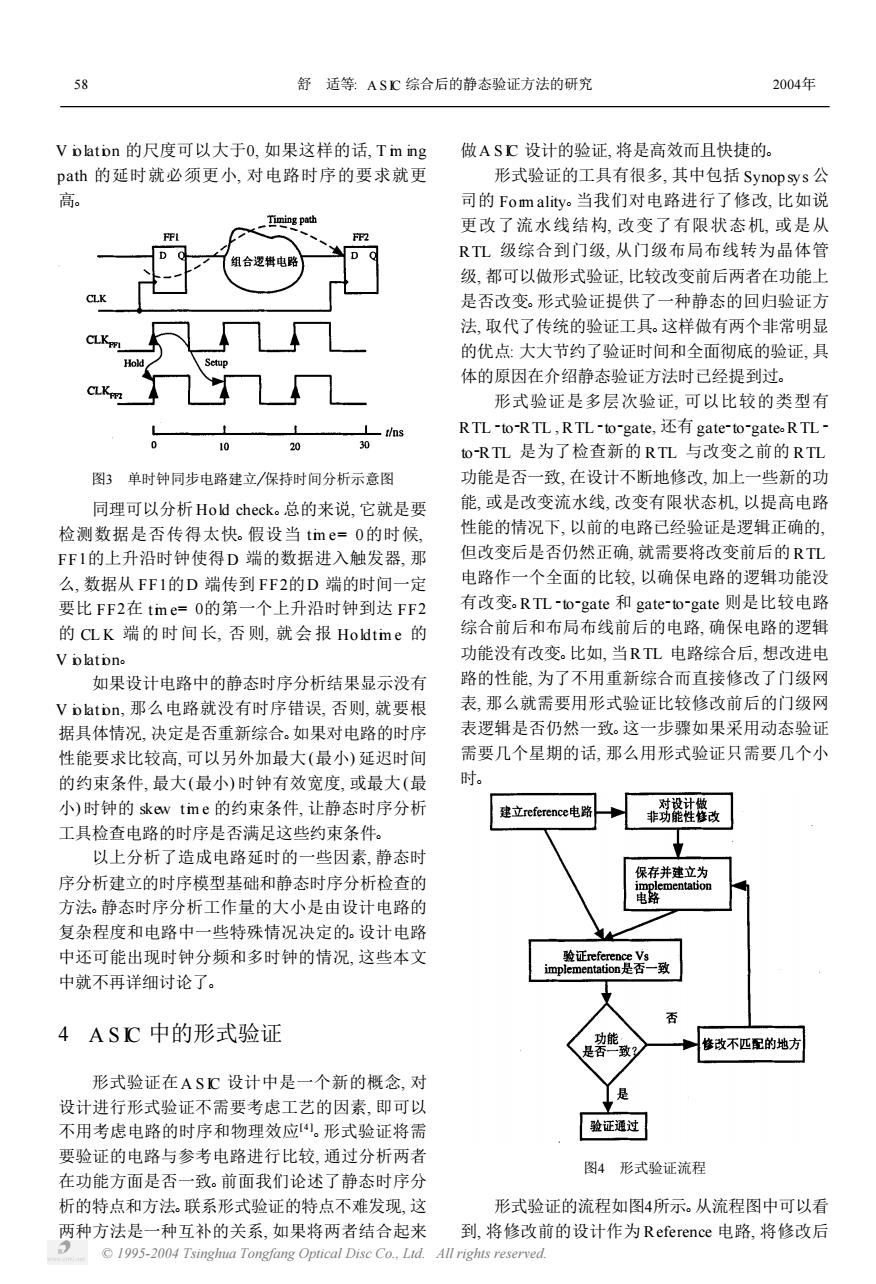

特定条件下的功能正确, 不能据此说明电路一定没 有功能错误。在提出静态时序分析和形式验证的概 念后, 我们可以用静态验证代替动态验证。静态验证 的方法是把时序验证和逻辑功能验证分开来做, 不 需要加任何激励。这样做可以大大节省验证时间。 静态时序分析是判断电路中所有单元是否满足 时序要求。静态时序分析检查设计中电路每一条通 路的时序信息, 看是否有时序错误。静态时序分析不 检查电路的逻辑功能, 所以, 在做完电路的时序验证 后, 还必须做形式验证。 形式验证不考虑设计电路的时序问题, 它只比 较两个电路的功能是否一致。形式验证不需要加激 励。因此, 如果 R TL 级电路动态验证正确的前提条 件成立, 那么, 只要通过形式验证, 就能保证后者的 电路功能没有错误。 比较动态验证和静态验证, 后者的优点在于: 1) 运行时间短; 2) 覆盖率为100% ; 3) 通过错误分析报 告, 比较容易找到出错处。 下面, 我们着重就后一种验证方法进行具体的 描述。 3 A S IC 中的静态时序分析 在设计A S IC 芯片的时候, 设计者除了要考虑 如何按照要求设计出正确的电路外, 还要考虑设计 电路在物理层实现后, 原本在R TL 级正确的逻辑关 系是否还会保证不出错。因此, 设计者需要能够精确 描述器件特性的器件模型。这些器件模型要和实际 器件的工作情况相同, 当用这些器件模型做设计电 路验证时, 电路的工作情况就和实际设计出来的芯 片的工作情况相同[ 2 ]。 建立一个用器件模型搭出的简单电路, 如图2所 示。从图中可以看出造成电路延时的四种因素。数据 输入跳变延时取决于D 触发器输入端充放电的速 度和输入端 RC 负载的大小, 输入数据跳变越频繁, 延时就越长; 门延时由D 触发器自身 RC 负载大小 和充放电速度决定; 线上 RC 延时则由D 触发器的 输出驱动能力和线上 RC 的负载大小决定, 连线越 长, 负载越大, 驱动时间越长; 输出负载只是增加D 触发器输出驱动的负荷量, 输出接负载的门数越多, 输出数据的延时时间就越长。这些延时是基于不同 的 CM O S 工艺和具体电路的布局布线。在特定的工 艺条件和工作环境下, 影响器件充放电速度和自身 RC 负载的因素有器件的面积、密度、掺杂密度、温 度、工作电压、输入充放电速度、输出扇出大小。我们 可以通过对实际电路进行测试, 从测试得到的数据 分析计算器件的延时信息, 这样就可以预测出电路 在实际实现后会出现的延时信息。不同的厂商提供 的库文件中已经包含了器件的延时信息, 做静态时 序分析的时候调用这些库文件, 分析和检查设计电 路各个路径的建立时间和保持时间是否满足时序要 求, 是否有违反设计规则的地方。 图2 电路器件延时模型 有了器件的模型, 就可以用 STA 的工具做电路 的静态时序分析。STA 主要分为两个阶段, 第一个 阶段是在布局布线前, 第二个阶段是在布局布线后。 这两个阶段的主要区别在于: 后者有具体的连线长 度、宽度、信号分布情况等信息, 所以, 后者可以更加 准确地估计线上延时, 以及时钟树的延时; 而前者只 能根据设计电路面积的大小, 估计线上延时和时钟 树的延时。 STA 的工具有 Synop sys 公司的 P rim etim e, Cadence 公司的 Pearl, 等等。静态时序分析工具可以 对设计电路进行以下几种分析: a) 从主要的输入端口到电路中所有触发器; b) 从触发器到触发器; c) 从触发器到主要输出端口; d) 从主要的输入端口到主要的输出端口。 静态时序分析工具把整个设计电路打散成上述 四种类型的时序路径, 分析不同路径的时序信息, 得 到建立时间和保持时间的计算结果。这里有必要介 绍一下这两个参数的含义, 因为静态时序分析的精 髓就在于判断和分析这两个参数的结果。 如图3所示[ 3 ] , 数据从触发器 FF1的D 端进入, 传到触发器 FF2的Q 端输出, 这是一个最基本的时 序路径, 而且这两个触发器都是用同一个时钟驱动。 首先分析 Setup check。假设在 tim e= 0的时候, FF1的第一个上升沿时钟使得 FF1获得D 端的数 据, 那么, 数据到达 FF2的D 端的时间一定要比 FF2 的第二个上升沿时钟到达 FF2的 CL K 端的时间要 短。如果预定的 Setup tim e V iolation 的尺度为“0”, 要求数据到达的时间就必须小于10 ns, 否则, 时序 分析结果就会报 setup tim e 的 V iolation。Setup tim e 第 1 期 舒 适等: A S IC 综合后的静态验证方法的研究 57 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

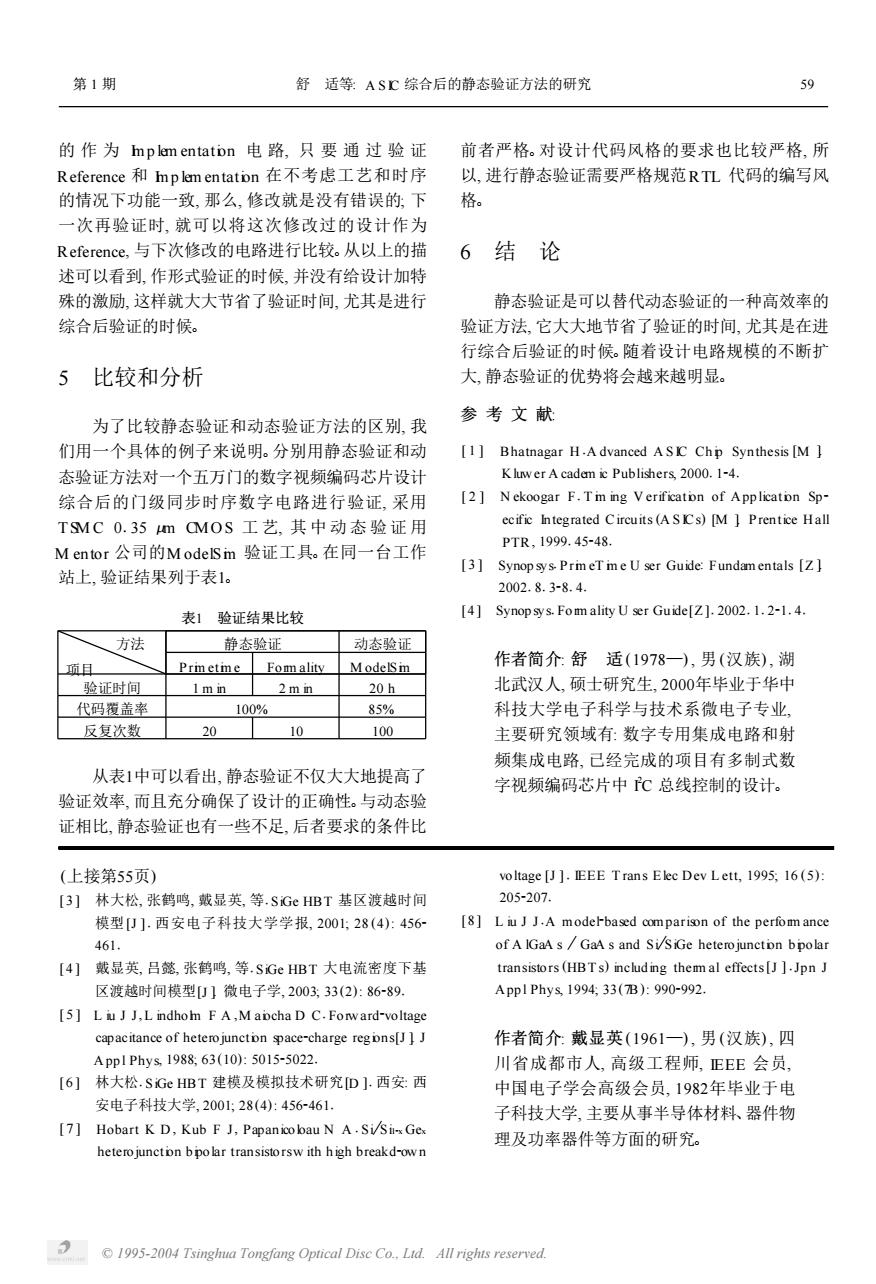

58 舒适等:ASC综合后的静态验证方法的研究 2004年 V plation的尺度可以大于0,如果这样的话,Tmng 做ASC设计的验证,将是高效而且快捷的。 path的延时就必须更小,对电路时序的要求就更 形式验证的工具有很多,其中包括Synop sys公 高。 司的Fom ality。当我们对电路进行了修改,比如说 T工ming path 更改了流水线结构,改变了有限状态机,或是从 52 RTL级综合到门级,从门级布局布线转为晶体管 组合逻辑电路 级,都可以做形式验证,比较改变前后两者在功能上 是否改变。形式验证提供了一种静态的回归验证方 法,取代了传统的验证工具。这样做有两个非常明显 的优点:大大节约了验证时间和全面彻底的验证,具 体的原因在介绍静态验证方法时已经提到过。 形式验证是多层次验证,可以比较的类型有 t/ns RTL-to-RTL,RTL-to-gate,还有gate-to-gate R TL- 0 20 30 to-RTL是为了检查新的RTL与改变之前的RTL 图3单时钟同步电路建立/保持时间分析示意图 功能是否一致,在设计不断地修改,加上一些新的功 同理可以分析Hold check。总的来说,它就是要 能,或是改变流水线,改变有限状态机,以提高电路 检测数据是否传得太快。假设当time=0的时候, 性能的情况下,以前的电路己经验证是逻辑正确的, FFI的上升沿时钟使得D端的数据进入触发器,那 但改变后是否仍然正确,就需要将改变前后的RTL 么,数据从FF1的D端传到FF2的D端的时间一定 电路作一个全面的比较,以确保电路的逻辑功能没 要比FF2在time=0的第一个上升沿时钟到达FF2 有改变。RTL~to-gate和gate~to~gate则是比较电路 的CLK端的时间长,否则,就会报Holdtie的 综合前后和布局布线前后的电路,确保电路的逻辑 Vpolatine 功能没有改变。比如,当RTL电路综合后,想改进电 如果设计电路中的静态时序分析结果显示没有 路的性能,为了不用重新综合而直接修改了门级网 V platin,那么电路就没有时序错误,否则,就要根 表,那么就需要用形式验证比较修改前后的门级网 据具体情况,决定是否重新综合。如果对电路的时序 表逻辑是否仍然一致。这一步骤如果采用动态验证 性能要求比较高,可以另外加最大(最小)延迟时间 需要几个星期的话,那么用形式验证只需要几个小 的约束条件,最大(最小)时钟有效宽度,或最大(最 时。 小)时钟的skew tme的约束条件,让静态时序分析 对设计做 建立reference电路 非功能性修政 工具检查电路的时序是否满足这些约束条件。 以上分析了造成电路延时的一些因素,静态时 保存并建立为 序分析建立的时序模型基础和静态时序分析检查的 電路 方法。静态时序分析工作量的大小是由设计电路的 复杂程度和电路中一些特殊情况决定的。设计电路 中还可能出现时钟分频和多时钟的情况,这些本文 验证reference Vs implementation是否一致 中就不再详细讨论了。 4ASC中的形式验证 功能 是否一致多 修改不匹配的地方 形式验证在ASC设计中是一个新的概念,对 是 设计进行形式验证不需要考虑工艺的因素,即可以 不用考虑电路的时序和物理效应。形式验证将需 验证通过 要验证的电路与参考电路进行比较,通过分析两者 图4形式验证流程 在功能方面是否一致。前面我们论述了静态时序分 析的特点和方法。联系形式验证的特点不难发现,这 形式验证的流程如图4所示。从流程图中可以看 两种方法是一种互补的关系,如果将两者结合起来 到,将修改前的设计作为Reference电路,将修改后 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

V iolation 的尺度可以大于0, 如果这样的话, T im ing path 的延时就必须更小, 对电路时序的要求就更 高。 图3 单时钟同步电路建立ö保持时间分析示意图 同理可以分析 Hold check。总的来说, 它就是要 检测数据是否传得太快。假设当 tim e= 0的时候, FF1的上升沿时钟使得D 端的数据进入触发器, 那 么, 数据从 FF1的D 端传到 FF2的D 端的时间一定 要比 FF2在 tim e= 0的第一个上升沿时钟到达 FF2 的 CL K 端的时间长, 否则, 就会报 Holdtim e 的 V iolation。 如果设计电路中的静态时序分析结果显示没有 V iolation, 那么电路就没有时序错误, 否则, 就要根 据具体情况, 决定是否重新综合。如果对电路的时序 性能要求比较高, 可以另外加最大(最小) 延迟时间 的约束条件, 最大(最小) 时钟有效宽度, 或最大(最 小) 时钟的 skew tim e 的约束条件, 让静态时序分析 工具检查电路的时序是否满足这些约束条件。 以上分析了造成电路延时的一些因素, 静态时 序分析建立的时序模型基础和静态时序分析检查的 方法。静态时序分析工作量的大小是由设计电路的 复杂程度和电路中一些特殊情况决定的。设计电路 中还可能出现时钟分频和多时钟的情况, 这些本文 中就不再详细讨论了。 4 A S IC 中的形式验证 形式验证在A S IC 设计中是一个新的概念, 对 设计进行形式验证不需要考虑工艺的因素, 即可以 不用考虑电路的时序和物理效应[ 4 ]。形式验证将需 要验证的电路与参考电路进行比较, 通过分析两者 在功能方面是否一致。前面我们论述了静态时序分 析的特点和方法。联系形式验证的特点不难发现, 这 两种方法是一种互补的关系, 如果将两者结合起来 做A S IC 设计的验证, 将是高效而且快捷的。 形式验证的工具有很多, 其中包括 Synop sys 公 司的 Form ality。当我们对电路进行了修改, 比如说 更改了流水线结构, 改变了有限状态机, 或是从 R TL 级综合到门级, 从门级布局布线转为晶体管 级, 都可以做形式验证, 比较改变前后两者在功能上 是否改变。形式验证提供了一种静态的回归验证方 法, 取代了传统的验证工具。这样做有两个非常明显 的优点: 大大节约了验证时间和全面彻底的验证, 具 体的原因在介绍静态验证方法时已经提到过。 形式验证是多层次验证, 可以比较的类型有 R TL 2to2R TL , R TL 2to2gate, 还有 gate2to2gate。R TL 2 to2R TL 是为了检查新的 R TL 与改变之前的 R TL 功能是否一致, 在设计不断地修改, 加上一些新的功 能, 或是改变流水线, 改变有限状态机, 以提高电路 性能的情况下, 以前的电路已经验证是逻辑正确的, 但改变后是否仍然正确, 就需要将改变前后的 R TL 电路作一个全面的比较, 以确保电路的逻辑功能没 有改变。R TL 2to2gate 和 gate2to2gate 则是比较电路 综合前后和布局布线前后的电路, 确保电路的逻辑 功能没有改变。比如, 当R TL 电路综合后, 想改进电 路的性能, 为了不用重新综合而直接修改了门级网 表, 那么就需要用形式验证比较修改前后的门级网 表逻辑是否仍然一致。这一步骤如果采用动态验证 需要几个星期的话, 那么用形式验证只需要几个小 时。 图4 形式验证流程 形式验证的流程如图4所示。从流程图中可以看 到, 将修改前的设计作为 R eference 电路, 将修改后 58 舒 适等: A S IC 综合后的静态验证方法的研究 2004年 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

第1期 舒适等:ASC综合后的静态验证方法的研究 59 的作为mplem entaton电路,只要通过验证 前者严格。对设计代码风格的要求也比较严格,所 Reference和mplem entation在不考虑工艺和时序 以,进行静态验证需要严格规范RTL代码的编写风 的情况下功能一致,那么,修改就是没有错误的,下 格。 一次再验证时,就可以将这次修改过的设计作为 Reference,与下次修改的电路进行比较。从以上的描 6 结论 述可以看到,作形式验证的时候,并没有给设计加特 殊的激励,这样就大大节省了验证时间,尤其是进行 静态验证是可以替代动态验证的一种高效率的 综合后验证的时候。 验证方法,它大大地节省了验证的时间,尤其是在进 行综合后验证的时候。随着设计电路规模的不断扩 5 比较和分析 大,静态验证的优势将会越来越明显。 参考文献 为了比较静态验证和动态验证方法的区别,我 们用一个具体的例子来说明。分别用静态验证和动 [1]Bhatnagar H.A dvanced ASIC Chp Synthesis [M 态验证方法对一个五万门的数字视频编码芯片设计 Kluwer A cadem ic Publishers,2000.1-4. 综合后的门级同步时序数字电路进行验证,采用 [2 N ekoogar F.Tm ing Verificaton of Applicaton Sp- TMC0.35 m CMOS工艺,其中动态验证用 ecific Integrated Circuits (A S ICs)[M 1 Prentice Hall pTR,1999.45-48. M entor公司的M odelSi验证工具。在同一台工作 [3]Synopsys PrmeT me U ser Guide:Fundamentals [Z] 站上,验证结果列于表1。 2002.8.3-8.4. 表1验证结果比较 [4]Synopsys.Fom ality U ser Guide[Z].2002.1.2-1.4. 方法 静态验证 动态验证 顶且 Prmetme Fom ality ModelSm 作者简介:舒适(1978一),男(汉族),湖 验证时间 1min 2min 20h 北武汉人,硕士研究生,2000年毕业于华中 代码覆盖率 100% 85% 科技大学电子科学与技术系微电子专业, 反复次数 20 10 100 主要研究领域有:数字专用集成电路和射 频集成电路,己经完成的项目有多制式数 从表1中可以看出,静态验证不仅大大地提高了 字视频编码芯片中C总线控制的设计。 验证效率,而且充分确保了设计的正确性。与动态验 证相比,静态验证也有一些不足,后者要求的条件比 (上接第55页) voltage [J ]IEEE Trans Elec Dev Lett,1995;16(5): [3]林大松,张鹤鸣,戴显英,等.SiGeHBT基区渡越时间 205-207. 模型].西安电子科技大学学报,2001:28(4):456 [8]L iu JJ.A modelbased comparison of the perfom ance 461. of A IGaA s/GaA s and Si/SiGe heterojuncton bipolar [4]戴显英,吕懿,张鹤鸣,等.SiGeHBT大电流密度下基 transistors(HBTs)including them al effects[J ]Jpn J 区渡越时间模型U]微电子学,2003,33(2):86-89. Appl Phys,1994,33(B):990-992. [5]Luu JJ,L indhom FA,M aicha D C.Forward-voltage capacitance of heterojunction space-charge regins[J]J 作者简介:戴显英(1961一),男(汉族),四 Appl Phys,198863(10):5015-5022. 川省成都市人,高级工程师,EEE会员, [6]林大松.SiGeHBT建模及模拟技术研究D].西安:西 中国电子学会高级会员,1982年毕业于电 安电子科技大学,2001,28(4):456-461. 子科技大学,主要从事半导体材料、器件物 [7]Hobart K D,Kub F J,Papanicobau N A.Si/Six Gex 理及功率器件等方面的研究。 hetero juncton bpo lar transistorsw ith high breakd-own C 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

的 作 为 Imp lem entation 电 路, 只 要 通 过 验 证 R eference 和 Imp lem entation 在不考虑工艺和时序 的情况下功能一致, 那么, 修改就是没有错误的; 下 一次再验证时, 就可以将这次修改过的设计作为 R eference, 与下次修改的电路进行比较。从以上的描 述可以看到, 作形式验证的时候, 并没有给设计加特 殊的激励, 这样就大大节省了验证时间, 尤其是进行 综合后验证的时候。 5 比较和分析 为了比较静态验证和动态验证方法的区别, 我 们用一个具体的例子来说明。分别用静态验证和动 态验证方法对一个五万门的数字视频编码芯片设计 综合后的门级同步时序数字电路进行验证, 采用 T SM C 0135 Λm CM O S 工 艺, 其 中 动 态 验 证 用 M entor 公司的M odelSim 验证工具。在同一台工作 站上, 验证结果列于表1。 表1 验证结果比较 方法 项目 静态验证 动态验证 P rim etim e Form ality M odelSim 验证时间 1 m in 2 m in 20 h 代码覆盖率 100% 85% 反复次数 20 10 100 从表1中可以看出, 静态验证不仅大大地提高了 验证效率, 而且充分确保了设计的正确性。与动态验 证相比, 静态验证也有一些不足, 后者要求的条件比 前者严格。对设计代码风格的要求也比较严格, 所 以, 进行静态验证需要严格规范R TL 代码的编写风 格。 6 结 论 静态验证是可以替代动态验证的一种高效率的 验证方法, 它大大地节省了验证的时间, 尤其是在进 行综合后验证的时候。随着设计电路规模的不断扩 大, 静态验证的优势将会越来越明显。 参 考 文 献: [ 1 ] Bhatnagar H 1A dvanced A S IC Ch ip Synthesis [M ]. K luw er A cadem ic Publishers, 200011241 [ 2 ] N ekoogar F1T im ing V erification of A pp lication Sp2 ecific Integrated C ircuits (A S IC s) [M ]. P rentice H all PTR, 19991452481 [ 3 ] Synop sys1P rim eT im e U ser Guide: Fundam entals [Z ]. 2002181328141 [4 ] Synop sys1Form ality U ser Guide[Z]12002111221141 作者简介: 舒 适 (1978—) , 男 (汉族) , 湖 北武汉人, 硕士研究生, 2000年毕业于华中 科技大学电子科学与技术系微电子专业, 主要研究领域有: 数字专用集成电路和射 频集成电路, 已经完成的项目有多制式数 字视频编码芯片中 I 2 C 总线控制的设计。 (上接第55页) [ 3 ] 林大松, 张鹤鸣, 戴显英, 等1SiGe HBT 基区渡越时间 模型[J ] 1西安电子科技大学学报, 2001; 28 (4): 4562 4611 [ 4 ] 戴显英, 吕懿, 张鹤鸣, 等1SiGe HBT 大电流密度下基 区渡越时间模型[J ]. 微电子学, 2003; 33 (2): 862891 [ 5 ] L iu J J, L indholm F A ,M aiocha D C1Forw ard2voltage capacitance of heterojunction space2charge regions[J ]. J A pp l Phys, 1988; 63 (10): 5015250221 [ 6 ] 林大松1SiGe HBT 建模及模拟技术研究[D ]1西安: 西 安电子科技大学, 2001; 28 (4): 45624611 [ 7 ] Hobart K D , Kub F J, Papanicoloau N A 1SiöSi12x Gex heterojunction bipolar transistorsw ith h igh breakd2ow n voltage [J ] 1IEEE T rans E lec D ev L ett, 1995; 16 (5): 20522071 [8 ] L iu J J 1A model2based comparison of the perform ance of A lGaA s öGaA s and SiöSiGe heterojunction bipolar transistors (HBT s) including therm al effects[J ] 1Jpn J A pp l Phys, 1994; 33 (7B): 99029921 作者简介: 戴显英 (1961—) , 男 (汉族) , 四 川省成都市人, 高级工程师, IEEE 会员, 中国电子学会高级会员, 1982年毕业于电 子科技大学, 主要从事半导体材料、器件物 理及功率器件等方面的研究。 第 1 期 舒 适等: A S IC 综合后的静态验证方法的研究 59 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved