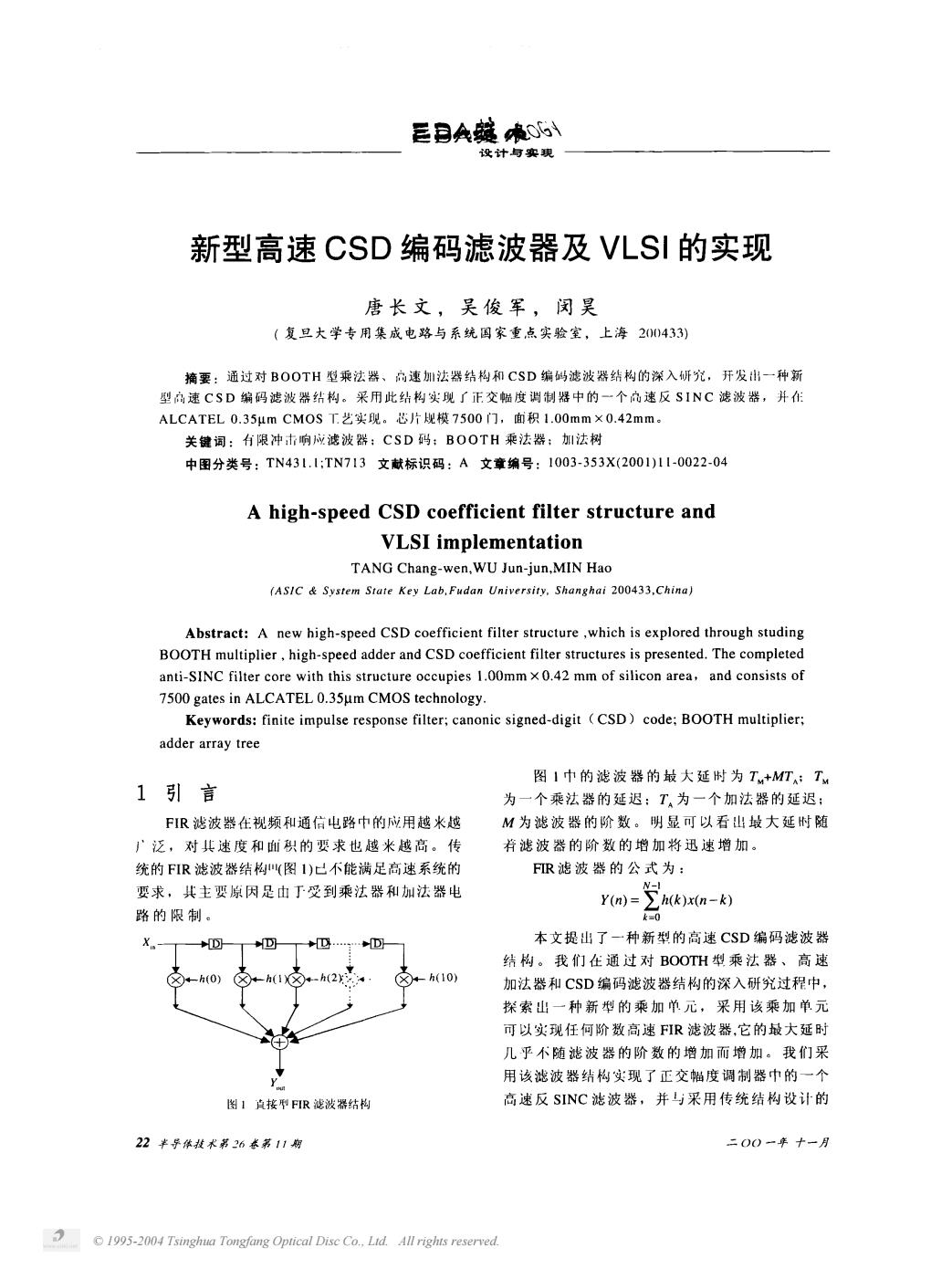

三日A 设计与实现 新型高速CSD编码滤波器及VLSI的实现 唐长文,吴俊军,闵昊 (复旦大学专用集成电路与系统国家重点实验室,上海200433) 摘要:通过对BOOTH型乘法器、速加法器结构和CSD编码滤波器结构的深入研究,开发出一种新 型高速CSD编码滤波器结构。采用此结构实现了正交幅度调制器中的一个速反SINC滤波器,并在 ALCATEL0.35 um CMOS T艺实现。芯片规模7500门,面积1.00mm×0.42mm。 关键词:有限冲击响应滤波器:CSD码:BOOTH乘法器;加法树 中图分类号:TN431.I;TN713文献标识码:A文章编号:1003-353X(2001)11-0022-04 A high-speed CSD coefficient filter structure and VLSI implementation TANG Chang-wen,WU Jun-jun,MIN Hao (ASIC System State Key Lab,Fudan University,Shanghai 200433,China) Abstract:A new high-speed CSD coefficient filter structure which is explored through studing BOOTH multiplier,high-speed adder and CSD coefficient filter structures is presented.The completed anti-SINC filter core with this structure occupies 1.00mm x0.42 mm of silicon area,and consists of 7500 gates in ALCATEL 0.35um CMOS technology. Keywords:finite impulse response filter;canonic signed-digit CSD)code;BOOTH multiplier; adder array tree 图1巾的滤波器的最大延时为TM+MTA;TM 1引言 为一个乘法器的延迟:T为一个加法器的延迟; FIR滤波器在视频和通信电路中的应用越米越 M为滤波器的阶数。明显可以看出坡大延时随 广泛,对其速度和面积的要求也越来越高。传 着滤波器的阶数的增加将迅速增加。 统的FIR滤波器结构(图1)已不能满足高速系统的 FIR滤波器的公式为: 要求,其主要原因是由于受到乘法器和加法器电 N-1 Y(n)=h(k)x(n-k) 路的限制。 k=0 X→回→→巴→D 本文提出了一种新型的高速CSD编码滤波器 结构。我们在通过对BOOTH型乘法器、高速 4-h0) -(10-h(2-h(10) 加法器和CSD编码滤波器结构的深入研究过程中, 探索出一种新型的乘加单元,采用该乘加单元 可以实现任何阶数高速FIR滤波器,它的最大延时 几乎不随滤波器的阶数的增加而增加。我们采 用该滤波器结构实现了正交幅度调制器巾的一个 图1直接型FR滤波器结构 高速反SINC滤波器,并与采用传统结构设计的 22半导体技术第26参第11期 二0O一年十一月 1995-2004 Tsinghua Tongfang Optical Disc Co.,Lid.All rights reserved

© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

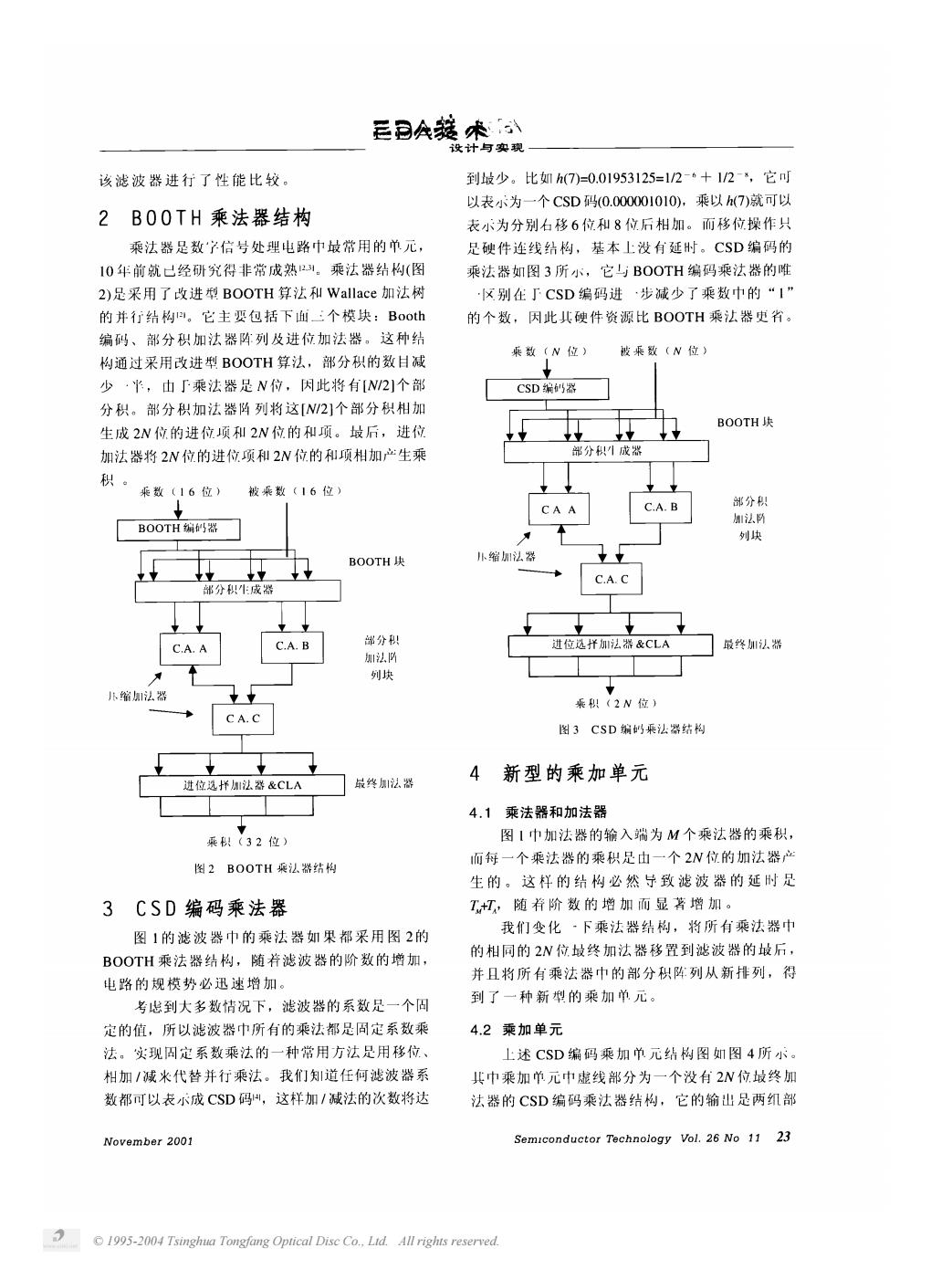

已A装來小 设计与实现 该滤波器进行了性能比较。 到坡少。比如h(7)=0.01953125=1/2-6十1/2-,它可 以表小示为一个CSD码(0.000001010),乘以h(7)就可以 2B00TH乘法器结构 表小示为分别名移6位和8位后相加。而移位操作只 乘法器是数字信号处理电路巾歧常用的单元, 足硬件连线结构,基本上没有延时。CSD编码的 10年前就已经研究得非常成熟2.。乘法器结构(图 乘法器如图3所小,它与BOOTH编码乘法器的唯 2)是采用了改进型BOOTH算法和Wallace加法树 区别在丁CSD编码进·步减少了乘数巾的“1” 的并行结构。它主要包括下血三个模块:Booth 的个数,因此其硬件资源比BOOTH乘法器吏省。 编码、部分积加法器阵列及进位加法器。这种结 乘数(N位) 被乘数(N位) 构通过采用改进型BOOTH算法,部分积的数甘减 少·半,由于乘法器足N位,因此将有N2]个部 CSD编妈器 分积。部分积加法器陷列将这[N2]个部分积相加 BOOTH块 生成2N位的进位项和2N位的和项。歧后,进位 加法器将2N位的进位项和2N位的和项相加产生乘 部分积成器 积。 乘数(16位) 被乘数(16位》 C.A.B 部分积 加法所 BOOTH编5器 刻块 BOOTH块 小缩加法器 部分积生成器 C.A.B 部分积 进位选并加法器&CLA 最终加以器 加法所 列块 小缩法器 乘积(2N位) 图3CSD编妈乘法器结构 4新型的乘加单元 进位远并加法誉&CLA 最终加法器 4.1乘法器和加法器 乘积(32位) 图1巾加法器的输入端为M个乘法器的乘积, 而每一个乘法器的乘积是由一个2N位的加法器产 图2 BOOTH乘泓器结构 生的。这样的结构必然宁致滤波器的延时足 3CSD编码乘法器 T+,随行阶数的增加而显若增加。 图1的滤波器巾的乘法器如果都采用图2的 我们变化·下乘法器结构,将所有乘法器巾 BOOTH乘法器结构,随荇滤波器的阶数的增加, 的相同的2W位蚊终加法器移置到滤波器的坡后, 并且将所有乘法器巾的部分积阵列从新排列,得 电路的规模势必迅速增加。 考虑到大多数情况下,滤波器的系数是一个回 到了一种新型的乘加单元。 定的值,所以滤波器巾所有的乘法都是同定系数乘 4.2乘加单元 法。实现因定系数乘法的一种常用方法是用移位、 上述CSD编码乘加单元结构图如图4所小。 相加/减米代替并行乘法。我们道任何滤波器系 其巾乘加单元中虚线部分为一个没有2N位最终加 数都可以表示成CSD码,这样加/减法的次数将达 法器的CSD编码乘法器结构,它的输出是两红部 November 2001 Semiconductor Technology Vol.26 No 11 23 1995-2004 Tsinghua Tongfang Optical Disc Co..Lid.All rights reserved

© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

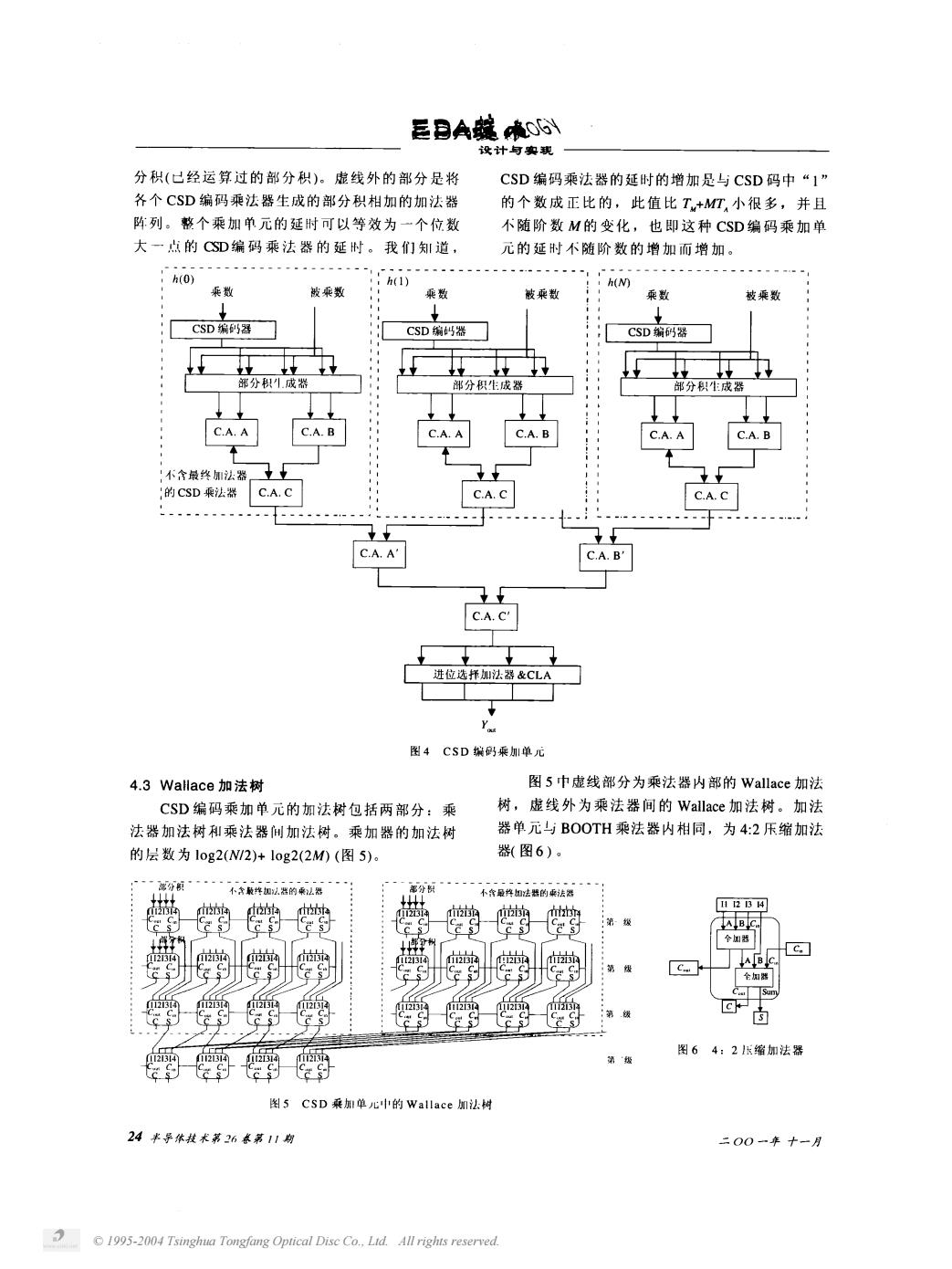

邑BA罐\ 设计与实现 分积(已经运算过的部分积)。虚线外的部分是将 CSD编码乘法器的延时的增加是与CSD码中“1” 各个CSD编码乘法器生成的部分积相加的加法器 的个数成正比的,此值比T+MT,小很多,并且 阵列。整个乘加单元的延时可以等效为一个位数 不随阶数M的变化,也即这种CSD编码乘加单 大一点的CSD编码乘法器的延时。我们知道, 元的延时不随阶数的增加而增加。 h(0) :h(1) h(N) 乘数 被乘数 乘数 被乘数 乘数 被乘数 CSD编码器 CSD编码器 CSD编码器 部分积1成器 部分积生成器 部分!生成器 C.A.B C.A.A 不含最终加法器 ,的CSD乘法器 C.A.C CA.B 进位选择加法器&CLA 图4CsD编码乘加1单元 4.3 Wallace加法树 图5中虚线部分为乘法器内部的Wallace加法 CSD编码乘加单元的加法树包括两部分:乘 树,虚线外为乘法器间的Wallace加法树。加法 法器加法树和乘法器间加法树。乘加器的加法树 器单元与B00TH乘法器内相同,为4:2乐缩加法 的层数为1og2(N/2)+1og2(2M)(图5)。 器(图6)。 ·部分积 不含敲加以器的乘器 部分积 不含最抖加法器的乘法器 H234 第级 全加器 c. 1234 学 全加器 Sam 123 1234 123 12 图6 4:2压缩加法器 112I314 1234 第 图5CSD乘加!单儿中的Wallace加让树 24半导体技术第26春第11期 二O0一年十一月 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

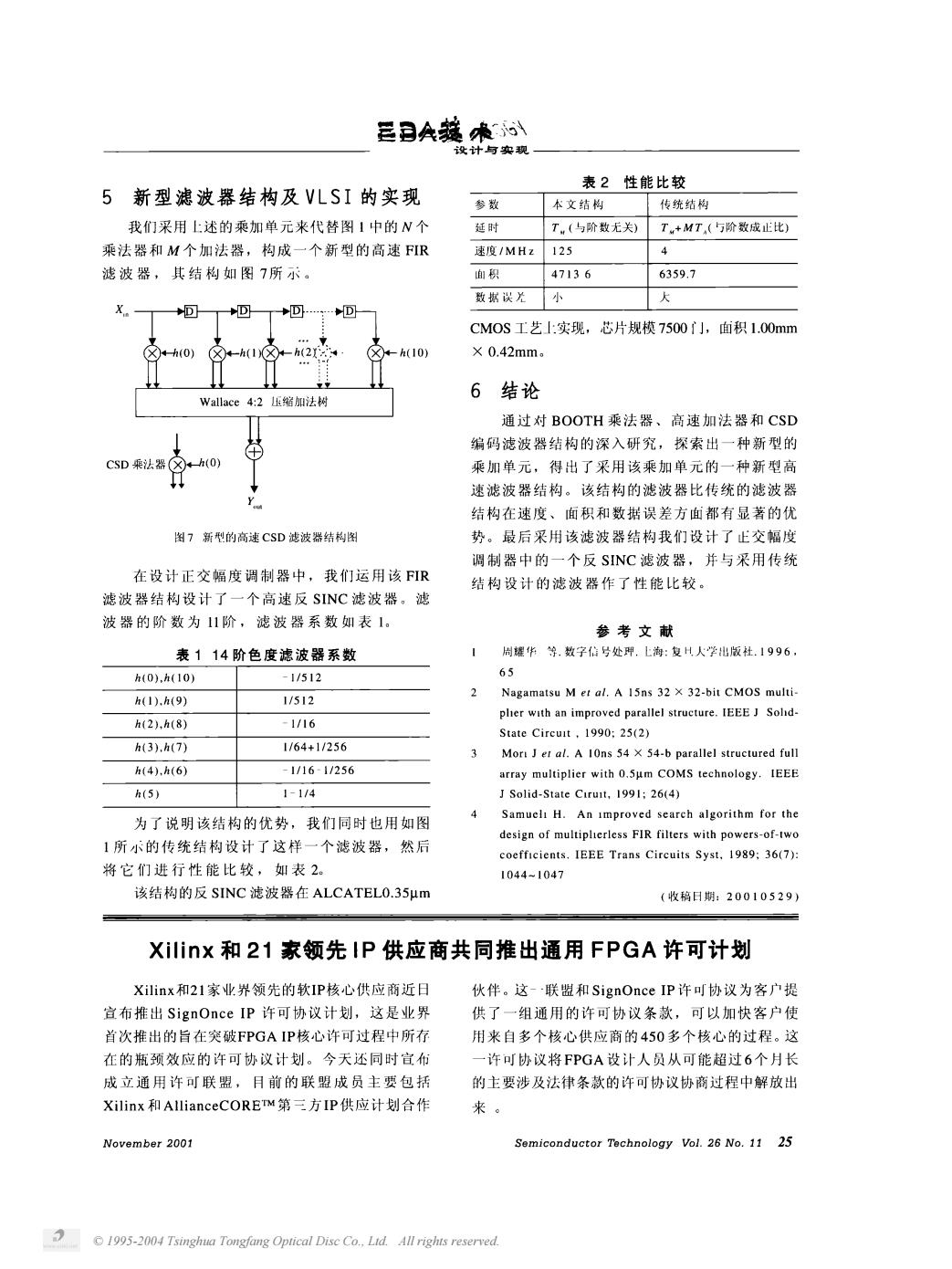

三目A接来\ 设计句实现 表2性能比较 5新型滤波器结构及VLSI的实现 参数 本文结构 传统结构 我们采用上述的乘加单元来代替图1中的N个 延时 T(马阶数无关) T+MT,(与阶数成止比) 乘法器和M个加法器,构成一个新型的高速FIR 速度1MHz 125 4 滤波器,其结构如图7所示。 血积 47136 6359.7 数据误片 小 D D CMOS工艺上:实现,芯片规模7500J,面积1.00mm h(0) h(2 h(10) ×0.42mm。 Wallace4:2压缩加法树 6结论 通过对BOOTH乘法器、高速加法器和CSD 编码滤波器结构的深入研究,探索出一种新型的 CSD乘法器 乘加单元,得出了采用该乘加单元的一种新型高 速滤波器结构。该结构的滤波器比传统的滤波器 结构在速度、面积和数据误差方面都有显著的优 图7新型的高速CSD滤波器结构图 势。最后采用该滤波器结构我们设计了止交幅度 调制器中的一个反SINC滤波器,并与采用传统 在设计正交幅度调制器中,我们运用该FIR 结构设计的滤波器作了性能比较。 滤波被器结构设计了一个高速反SINC滤波器,滤 波器的阶数为1阶,滤波器系数如表1。 参考文献 表114阶色度滤波器系数 1 周耀华等.数字信号处弹,上海:复H人学出版社.1996, h(0).h(10) -1/512 65 2 Nagamatsu M et al.A 15ns 32 X 32-bit CMOS multi- h(1).h(9) 1/512 phier with an improved parallel structure.IEEE J Sold- h(2),h(8) -1/16 State Circuit,1990;25(2) h(3),h(7) 1/64+1/256 3 Mort J er al.A 10ns 54 X 54-b parallel structured full h(4),h(6) -1/16-1/256 array multiplier with 0.5um COMS technology.IEEE h(5) 1-1/4 J Solid-State Ciruit,1991;26(4) 4 为了说明该结构的优势,我们同时也用如图 SamuelI H.An improved search algorithm for the design of multiplierless FIR filters with powers-of-two 1所小的传统结构设计了这样一个滤波器,然后 coefficients.IEEE Trans Circuits Syst,1989;36(7): 将它们进行性能比较,如表2。 1044-1047 该结构的反SINC滤波器在ALCATEL0.35μm (收稿日期:20010529) Xilinx和21家领先IP供应商共同推出通用FPGA许可计划 Xilinx和21家业养领先的软IP核心供应商近日 伙伴。这-~联盟和SignOnce IP许可协议为客户提 宣布推出SignOnce IP许可协议计划,这是业界 供了一组通用的许可协议条款,可以加快客户使 首次推出的旨在突破FPGA IP核心许可过程中所存 用来自多个核心供应商的450多个核心的过程。这 在的瓶颈效应的许可协议计划。今天还同时宣布 一许可协议将FPGA设计人员从可能超过6个月长 成立通用许可联盟,月前的联盟成员主要包括 的主要涉及法律条款的许可协议协商过程中解放出 Xilinx和AllianceCORETM第三方IP供应计划合作 来。 November 2001 Semiconductor Technology Vol.26 No.11 25 1995-2004 Tsinghua Tongfang Optical Disc Co..Lid.All rights reserved

© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved