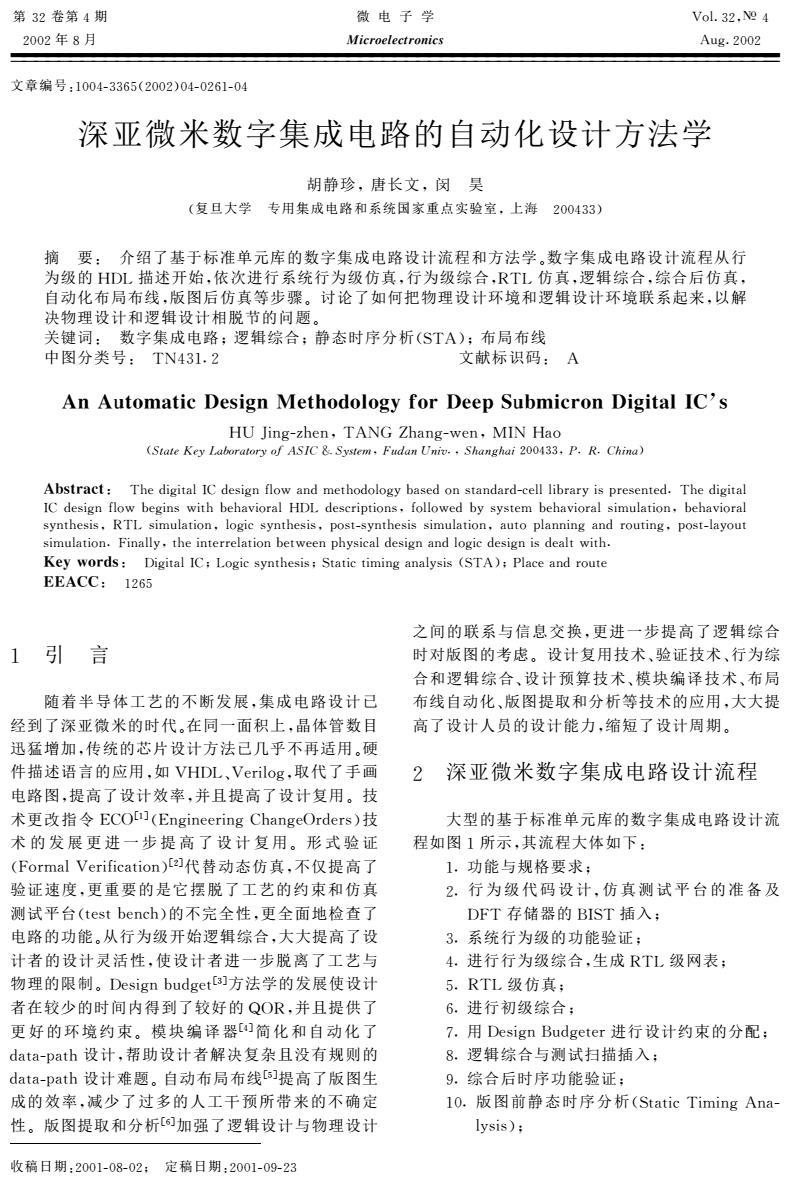

第32卷第4期 微电子学 Vol.32,94 2002年8月 Microelectronics Aug.2002 文章编号:1004-3365(2002)04-0261-04 深亚微米数字集成电路的自动化设计方法学 胡静珍,唐长文,闵昊 (复旦大学专用集成电路和系统国家重点实验室,上海200433) 摘要:介绍了基于标准单元库的数字集成电路设计流程和方法学。数字集成电路设计流程从行 为级的HDL描述开始,依次进行系统行为级仿真,行为级综合,RTL仿真,逻辑综合,综合后仿真, 自动化布局布线,版图后仿真等步骤。讨论了如何把物理设计环境和逻辑设计环境联系起来,以解 决物理设计和逻辑设计相脱节的问题。 关键词:数字集成电路;逻辑综合:静态时序分析(STA);布局布线 中图分类号:TN431.2 文献标识码:A An Automatic Design Methodology for Deep Submicron Digital IC's HU Jing-zhen,TANG Zhang-wen,MIN Hao (State Key Laboratory of ASIC System,Fudan Univ..Shanghai 200433.P.R.China) Abstract:The digital IC design flow and methodology based on standard-cell library is presented.The digital IC design flow begins with behavioral HDL descriptions,followed by system behavioral simulation,behavioral synthesis.RTL simulation,logic synthesis,post-synthesis simulation,auto planning and routing,post-layout simulation.Finally,the interrelation between physical design and logic design is dealt with. Key words:Digital IC;Logic synthesis:Static timing analysis (STA);Place and route EEACC:1265 之间的联系与信息交换,更进一步提高了逻辑综合 1 引言 时对版图的考虑。设计复用技术、验证技术、行为综 合和逻辑综合、设计预算技术、模块编译技术、布局 随着半导体工艺的不断发展,集成电路设计已 布线自动化、版图提取和分析等技术的应用,大大提 经到了深亚微米的时代。在同一面积上,晶体管数目 高了设计人员的设计能力,缩短了设计周期。 迅猛增加,传统的芯片设计方法已几乎不再适用。硬 件描述语言的应用,如VHDL、Verilog,取代了手画 2深亚微米数字集成电路设计流程 电路图,提高了设计效率,并且提高了设计复用。技 术更改指令ECO](Engineering ChangeOrders)技 大型的基于标准单元库的数字集成电路设计流 术的发展更进一步提高了设计复用。形式验证 程如图1所示,其流程大体如下: (Formal Verification)代替动态仿真,不仅提高了 1.功能与规格要求: 验证速度,更重要的是它摆脱了工艺的约束和仿真 2.行为级代码设计,仿真测试平台的准备及 测试平台(test bench)的不完全性,更全面地检查了 DFT存储器的BIST插入: 电路的功能。从行为级开始逻辑综合,大大提高了设 3.系统行为级的功能验证; 计者的设计灵活性,使设计者进一步脱离了工艺与 4.进行行为级综合,生成RTL级网表: 物理的限制。Design budget3]方法学的发展使设计 5.RTL级仿真: 者在较少的时间内得到了较好的QOR,并且提供了 6.进行初级综合: 更好的环境约束。模块编译器简化和自动化了 7.用Design Budgeter进行设计约束的分配: data-path设计,帮助设计者解决复杂且没有规则的 8.逻辑综合与测试扫描插入: data-path设计难题。自动布局布线[提高了版图生 9.综合后时序功能验证: 成的效率,减少了过多的人工干预所带来的不确定 I0.版图前静态时序分析(Static Timing Ana 性。版图提取和分析[6们加强了逻辑设计与物理设计 lysis); 收稿日期:2001-08-02:定稿日期:2001-09-23

收稿日期!"##$%#&%#"’ 定稿日期!"##$%#(%") 文章编号!$##*%))+,-"##".#*%#"+$%#* 深亚微米数字集成电路的自动化设计方法学 胡静珍/唐长文/闵 昊 -复旦大学 专用集成电路和系统国家重点实验室/上海 "##*)). 摘 要! 介绍了基于标准单元库的数字集成电路设计流程和方法学0数字集成电路设计流程从行 为级的 123描述开始/依次进行系统行为级仿真/行为级综合/453仿真/逻辑综合/综合后仿真/ 自动化布局布线/版图后仿真等步骤0讨论了如何把物理设计环境和逻辑设计环境联系起来/以解 决物理设计和逻辑设计相脱节的问题0 关键词! 数字集成电路’逻辑综合’静态时序分析-657.’布局布线 中图分类号! 58*)$9" 文献标识码! 7 :;:?@=ABCDEAF;GD=H>I>J>FKL>MCDDNO;CAFA=@JQRSE 1T UVWX%YZ[W/578\]Z^WX%_[W/‘a8 1^b -cdedfgfhiejkledklhkmncopqchrdfs/tuvewxwyz9/c{ew|{ey"##*))/}9~9p{ywe. :PE=M@B=! 5Z[!VXV"^#a$

262 胡静珍等:深亚微米数字集成电路的自动化设计方法学 2002年 ll.floorplan,布局,Clock Tree的插入以及全 18.功耗分析 局布线: 19.DRC&.LVS验证 l2.插入Clock Tree后的网表重新进行综合; 20.流片 l3.用Formality[6]验证原来的综合后网表和 数字集成电路设计的EDA工具已经发展到了 插入Clock Tree后的网表; 较完善的程度。整套流程都已实现了EDA自动化。 14.全局布线后进行静态时序分析: 但是,随着电路规模的增大和系统的越来越复杂,对 15.细节布线: EDA工具的要求越来越高。为解决新出现的问题, 16,版图后静态时序分析: 相继提出了一些新的技术,同时,新的工具也得到了 17.用门级电路的仿真器进行版图后时序功能 发展。本文重点介绍两种新技术。 验证; 场与情求 Ut乐的材表 TES RC.SDH 图1深亚微米数字集成电路设计流程

!!"#$%%&’$()*布局*+$%,-.&//的插入以及全 局布线0 !1"插入 +$%,-.&//后的网表重新进行综合0 !2"用 3%&4($56789:验证原来的综合后网表和 插入 +$%,-.&//后的网表0 !;"全局布线后进行静态时序分析0 !"功耗分析 !?"@A+BCDE验证 1F"流片 数字集成电路设计的 G@H工具已经发展到了 较完善的程度I整套流程都已实现了 G@H自动化I 但是*随着电路规模的增大和系统的越来越复杂*对 G@H工具的要求越来越高I为解决新出现的问题* 相继提出了一些新的技术*同时*新的工具也得到了 发展I本文重点介绍两种新技术I 图 ! 深亚微米数字集成电路设计流程 191 胡静珍等J深亚微米数字集成电路的自动化设计方法学 1FF1年

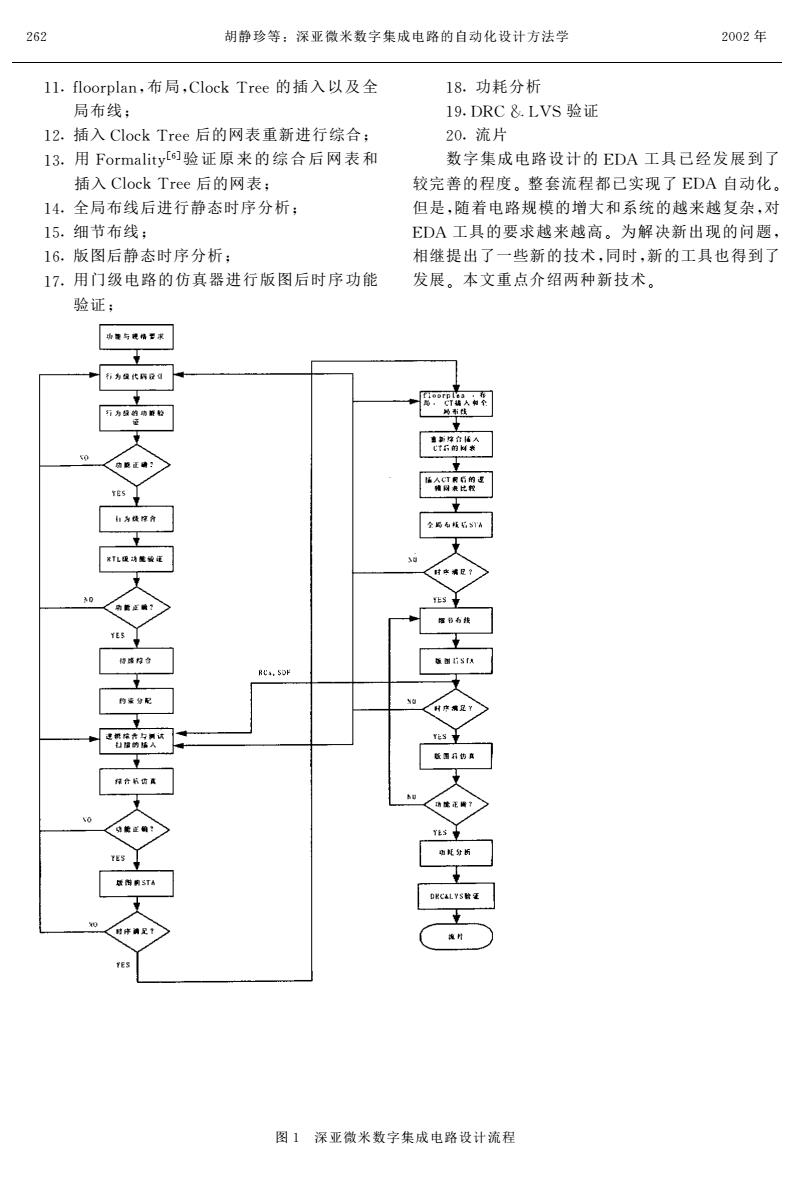

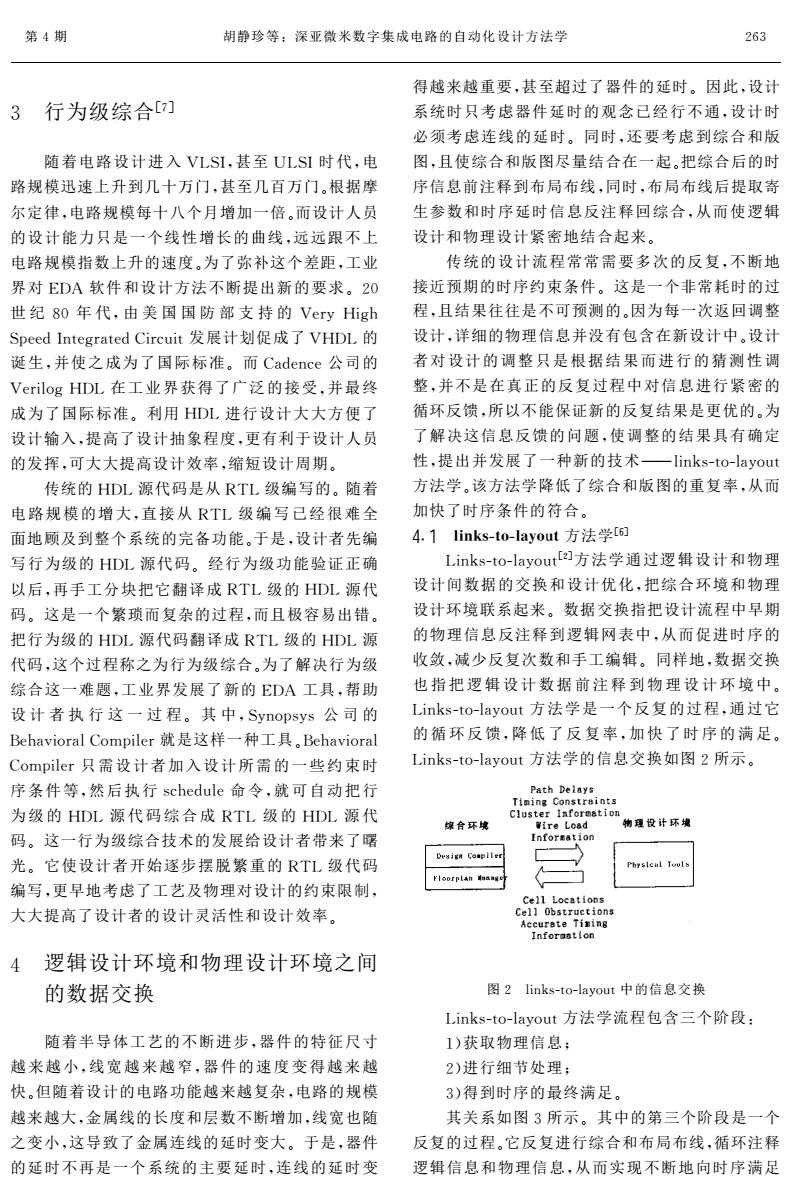

第4期 胡静珍等:深亚微米数字集成电路的自动化设计方法学 263 得越来越重要,甚至超过了器件的延时。因此,设计 3 行为级综合[] 系统时只考虑器件延时的观念已经行不通,设计时 必须考虑连线的延时。同时,还要考虑到综合和版 随着电路设计进入VLSI,甚至ULSI时代,电 图,且使综合和版图尽量结合在一起。把综合后的时 路规模迅速上升到几十万门,甚至几百万门。根据摩 序信息前注释到布局布线,同时,布局布线后提取寄 尔定律,电路规模每十八个月增加一倍。而设计人员 生参数和时序延时信息反注释回综合,从而使逻辑 的设计能力只是一个线性增长的曲线,远远跟不上 设计和物理设计紧密地结合起来。 电路规模指数上升的速度。为了弥补这个差距,工业 传统的设计流程常常需要多次的反复,不断地 界对EDA软件和设计方法不断提出新的要求。20 接近预期的时序约束条件。这是一个非常耗时的过 世纪80年代,由美国国防部支持的Very High 程,且结果往往是不可预测的。因为每一次返回调整 Speed Integrated Circuit发展计划促成了VHDL的 设计,详细的物理信息并没有包含在新设计中。设计 诞生,并使之成为了国际标准。而Cadence公司的 者对设计的调整只是根据结果而进行的猜测性调 Verilog HDL在工业界获得了广泛的接受,并最终 整,并不是在真正的反复过程中对信息进行紧密的 成为了国际标准。利用HDL进行设计大大方便了 循环反馈,所以不能保证新的反复结果是更优的。为 设计输入,提高了设计抽象程度,更有利于设计人员 了解决这信息反馈的问题,使调整的结果具有确定 的发挥,可大大提高设计效率,缩短设计周期。 性,提出并发展了一种新的技术一links-to-layout 传统的HDL源代码是从RTL级编写的。随着 方法学。该方法学降低了综合和版图的重复率,从而 电路规模的增大,直接从RTL级编写已经很难全 加快了时序条件的符合。 面地顾及到整个系统的完备功能。于是,设计者先编 4.1 links-to-layout方法学[6] 写行为级的HDL源代码。经行为级功能验证正确 Links--to-layout幻方法学通过逻辑设计和物理 以后,再手工分块把它翻译成RTL级的HDL源代 设计间数据的交换和设计优化,把综合环境和物理 码。这是一个繁琐而复杂的过程,而且极容易出错。 设计环境联系起来。数据交换指把设计流程中早期 把行为级的HDL源代码翻译成RTL级的HDL源 的物理信息反注释到逻辑网表中,从而促进时序的 代码,这个过程称之为行为级综合。为了解决行为级 收敛,减少反复次数和手工编辑。同样地,数据交换 综合这一难题,工业界发展了新的EDA工具,帮助 也指把逻辑设计数据前注释到物理设计环境中。 设计者执行这一过程。其中,Synopsys公司的 Links-to-layout方法学是一个反复的过程,通过它 Behavioral Compiler就是这样一种工具。Behavioral 的循环反馈,降低了反复率,加快了时序的满足。 Compiler只需设计者加入设计所需的一些约束时 Links-to-layout方法学的信息交换如图2所示。 序条件等,然后执行schedule命令,就可自动把行 Path Delays Timing Constraints 为级的HDL源代码综合成RTL级的HDL源代 Cluster Information 擦合环境 Wire Load 物理设计环城 码。这一行为级综合技术的发展给设计者带来了曙 Infor图ation Desiga CoaplLer 光。它使设计者开始逐步摆脱繁重的RTL级代码 Phrslcul Touls 编写,更早地考虑了工艺及物理对设计的约束限制, Cell Locations 大大提高了设计者的设计灵活性和设计效率。 Cel】0 bstructions Accurate Tining Inforastion 逻辑设计环境和物理设计环境之间 的数据交换 图2 links--to-layout中的信息交换 Links-to-layout方法学流程包含三个阶段: 随着半导体工艺的不断进步,器件的特征尺寸 1)获取物理信息: 越来越小,线宽越来越窄,器件的速度变得越来越 2)进行细节处理; 快。但随着设计的电路功能越来越复杂,电路的规模 3)得到时序的最终满足。 越来越大,金属线的长度和层数不断增加,线宽也随 其关系如图3所示。其中的第三个阶段是一个 之变小,这导致了金属连线的延时变大。于是,器件 反复的过程。它反复进行综合和布局布线,循环注释 的延时不再是一个系统的主要延时,连线的延时变 逻辑信息和物理信息,从而实现不断地向时序满足

! 行为级综合"#$ 随着电路设计进入 %&’()甚至 *&’(时代)电 路规模迅速上升到几十万门)甚至几百万门+根据摩 尔定律)电路规模每十八个月增加一倍+而设计人员 的设计能力只是一个线性增长的曲线)远远跟不上 电路规模指数上升的速度+为了弥补这个差距)工业 界对 ,-.软件和设计方法不断提出新的要求+/0 世 纪 10年 代)由 美 国 国 防 部 支 持 的 %2345678 ’922:(;63?@6=:2;?2公司的 %236AB75-&在工业界获得了广泛的接受)并最终 成为了国际标准+利用 5-&进行设计大大方便了 设计输入)提高了设计抽象程度)更有利于设计人员 的发挥)可大大提高设计效率)缩短设计周期+ 传统的 5-&源代码是从 CD&级编写的+随着 电路规模的增大)直接从 CD&级编写已经很难全 面地顾及到整个系统的完备功能+于是)设计者先编 写行为级的 5-&源代码+经行为级功能验证正确 以后)再手工分块把它翻译成 CD&级的 5-&源代 码+这是一个繁琐而复杂的过程)而且极容易出错+ 把行为级的 5-&源代码翻译成 CD&级的 5-&源 代码)这个过程称之为行为级综合+为了解决行为级 综合这一难题)工业界发展了新的 ,-.工具)帮助 设 计 者 执 行 这 一 过 程+ 其 中)’4;B9E4E公 司 的 F28=G6B3=A>BH96A23就是这样一种工具+F28=G6B3=A >BH96A23只需设计者加入设计所需的一些约束时 序条件等)然后执行 E?82:@A2命令)就可自动把行 为级的 5-&源代码综合 成 CD&级 的 5-&源 代 码+这一行为级综合技术的发展给设计者带来了曙 光+它使设计者开始逐步摆脱繁重的 CD&级代码 编写)更早地考虑了工艺及物理对设计的约束限制) 大大提高了设计者的设计灵活性和设计效率+ I 逻辑设计环境和物理设计环境之间 的数据交换 随着半导体工艺的不断进步)器件的特征尺寸 越来越小)线宽越来越窄)器件的速度变得越来越 快+但随着设计的电路功能越来越复杂)电路的规模 越来越大)金属线的长度和层数不断增加)线宽也随 之变小)这导致了金属连线的延时变大+于是)器件 的延时不再是一个系统的主要延时)连线的延时变 得越来越重要)甚至超过了器件的延时+因此)设计 系统时只考虑器件延时的观念已经行不通)设计时 必须考虑连线的延时+同时)还要考虑到综合和版 图)且使综合和版图尽量结合在一起+把综合后的时 序信息前注释到布局布线)同时)布局布线后提取寄 生参数和时序延时信息反注释回综合)从而使逻辑 设计和物理设计紧密地结合起来+ 传统的设计流程常常需要多次的反复)不断地 接近预期的时序约束条件+这是一个非常耗时的过 程)且结果往往是不可预测的+因为每一次返回调整 设计)详细的物理信息并没有包含在新设计中+设计 者对设计的调整只是根据结果而进行的猜测性调 整)并不是在真正的反复过程中对信息进行紧密的 循环反馈)所以不能保证新的反复结果是更优的+为 了解决这信息反馈的问题)使调整的结果具有确定 性)提出并发展了一种新的技术JJ A6;KEL<BLA=4B@< 方法学+该方法学降低了综合和版图的重复率)从而 加快了时序条件的符合+ MNO PQRSTUVWUPXYWZV方法学"[$ &6;KEL<BLA=4B@< "/$方法学通过逻辑设计和物理 设计间数据的交换和设计优化)把综合环境和物理 设计环境联系起来+数据交换指把设计流程中早期 的物理信息反注释到逻辑网表中)从而促进时序的 收敛)减少反复次数和手工编辑+同样地)数据交换 也指把逻辑设计数据前 注 释 到 物 理 设 计 环 境 中+ &6;KEL<BLA=4B@<方法学是一个反复的过程)通过它 的 循 环 反 馈)降 低 了 反 复 率)加 快 了 时 序 的 满 足+ &6;KEL<BLA=4B@<方法学的信息交换如图 /所示+ 图 / A6;KEL<BLA=4B@<中的信息交换 &6;KEL<BLA=4B@<方法学流程包含三个阶段\ ]^获取物理信息_ /^进行细节处理_ !^得到时序的最终满足+ 其关系如图 !所示+其中的第三个阶段是一个 反复的过程+它反复进行综合和布局布线)循环注释 逻辑信息和物理信息)从而实现不断地向时序满足 第 I期 胡静珍等\深亚微米数字集成电路的自动化设计方法学 /‘!

264 胡静珍等:深亚微米数字集成电路的自动化设计方法学 2002年 方向收敛。 layout的位置和功能如图4所示。 通过使用Floorplan Manager,实现了逻辑设计 铁收物理伯 选行烟节处理 海到时序的县势 满足 环境和物理设计环境的紧密联系,克服了以前逻辑 图3 links--to-layout的三个阶段 设计和物理设计相脱节的问题。 Design Compiler 运行初始的TL线 5 结束语 棕合 执行早期的物理没 随着电路规模的增大、系统复杂性的增强和半 布局布线工具 计 导体工艺的发展,集成电路设计进入了深亚微米时 代。传统的设计方法已不能适应时代的发展,设计者 下loorplan Manager 新建用户找负载 树型 旧的设计观念必须更新。逻辑设计和物理设计各司 其职、互不关心、互不了解的传统必须打破。深亚微 Design Coapiler 执行设计说算 米时代的集成电路设计要求设计者在进行HDL代 码设计时必须考虑后面的逻辑综合和布局布线,进 行逻辑综合时必须考虑布局布线,必须把逻辑综合 Floorplan Hanager 重新棕合RTL 和版图紧密地联系起来,把它们的信息互相反馈。信 息互相反馈是一件非常困难的事,原先的设计者只 布局布线工具 布局布找 能根据结果对设计进行猜测性的调整。Synopsys公 时序满足 时序不满足 司的Floorplan Manager工具的开发帮助设计者解 最终网表 决了这一难题。 参考文献: [1]Synopsys.ECO Compiler User Guide [Z].2000.05 图4 Floorplan Manager的应用设计流程 [2]Synopsys.Formality User Guide [Z].2000.05 4.2 Floorplan Managert6] [3]Synopsys.Design Budgeting User Guide [Z].2000. Floorplan Managert)是处理逻辑设计环境和 05 物理设计环境间数据交换的综合和优化工具。它提 [4] Synopsys.Module Compiler User Guide [Z].2000.05 供了Synopsys的links-to-layout方法学。使用 [5]Cadence.Cadence Envisia Silicon Ensemble Tutorial & Floorplan Manager工具,可以前注释逻辑数据到物 Envisia Silicon Ensemble Reference [Z]. 理环境,反注释物理数据到逻辑环境,反复优化设 [6] Synopsys.Floorplan Manager User Guide [Z].2000. 05 计,从而快速实现时序的最终满足。它在逻辑环境与 [7] Synopsys.Behavioral Compiler User Guide [Z]. 物理环境间的数据交换流程如同links-to-layout的 2000.05 数据交换流程。 Floorplan Manager内嵌于逻辑综合工具 作者简介:胡静珍(1979一),女(汉 Design Compiler。它使用与Design Compiler相同 族),浙江永康人,2001年毕业于复 的优化技术,相同的时序机制,使用dc一shell命令 旦大学电子工程系电子学与信息系 行界面,共享Design Compiler的report功能。也就 统专业,现在中科院上海技术物理 是说,Floorplan Manager并不是一个独立的工具, 研究所攻读硕士学位,主要研究领 但是有独立的命令,它在Design Compiler中嵌套使 域有:红外系统研究,数据的采集及 用。整个设计流程中Floorplan Manager和links--to- 处理,星载整机及器件研究等

方向收敛! 图 " #$%&’()*(#+,*-)的三个阶段 图 . /#**01#+%2+%+340的应用设计流程 567 89::;?=>=@A;BCD /#**01#+%2+%+340BED是 处 理 逻 辑 设 计 环 境 和 物理设计环境间数据交换的综合和优化工具!它提 供 了 F,%*1’,’的 #$%&’()*(#+,*-)方 法 学! 使 用 /#**01#+%2+%+340工具G可以前注释逻辑数据到物 理 环 境G反 注 释 物 理 数 据 到 逻 辑 环 境G反 复 优 化 设 计G从而快速实现时序的最终满足!它在逻辑环境与 物理环境间的数据交换流程如同 #$%&’()*(#+,*-)的 数据交换流程! /#**01#+% 2+%+340内 嵌 于 逻 辑 综 合 工 具 H4’$3%I*J1$#40!它使用与 H4’$3%I*J1$#40相同 的优化技术G相同的时序机制G使用 KLM’N4##命令 行界面G共享 H4’$3%I*J1$#40的 041*0)功能!也就 是说G/#**01#+%2+%+340并不是一个 独 立 的 工 具G 但是有独立的命令G它在 H4’$3%I*J1$#40中嵌套使 用!整个设计流程中 /#**01#+%2+%+340和 #$%&’()*( #+,*-)的位置和功能如图 .所示! 通过使用 /#**01#+%2+%+340G实现了逻辑设计 环境和物理设计环境的紧密联系G克服了以前逻辑 设计和物理设计相脱节的问题! O 结束语 随着电路规模的增大P系统复杂性的增强和半 导体工艺的发展G集成电路设计进入了深亚微米时 代!传统的设计方法已不能适应时代的发展G设计者 旧的设计观念必须更新!逻辑设计和物理设计各司 其职P互不关心P互不了解的传统必须打破!深亚微 米时代的集成电路设计要求设计者在进行 QHR代 码设计时必须考虑后面的逻辑综合和布局布线G进 行逻辑综合时必须考虑布局布线G必须把逻辑综合 和版图紧密地联系起来G把它们的信息互相反馈!信 息互相反馈是一件非常困难的事G原先的设计者只 能根据结果对设计进行猜测性的调整!F,%*1’,’公 司的 /#**01#+%2+%+340工具的开发帮助设计者解 决了这一难题! 参 考 文 献S BTD F,%*1’,’UVIWI*J1$#40X’40Y-$K4BZDUE[[[U[O BED F,%*1’,’U/*0J+#$),X’40Y-$K4BZDUE[[[U[O B"D F,%*1’,’UH4’$3%\-K34)$%3X’40Y-$K4BZDUE[[[U [O B.D F,%*1’,’U2*K-#4I*J1$#40X’40Y-$K4BZDUE[[[U[O BOD I+K4%L4UI+K4%L4V%]$’$+F$#$L*%V%’4J^#4_-)*0$+#‘ V%]$’$+F$#$L*%V%’4J^#4a4b404%L4BZDU BcD F,%*1’,’U/#**01#+%2+%+340X’40Y-$K4BZDUE[[[U [O BdD F,%*1’,’U\4N+]$*0+#I*J1$#40X’40Y-$K4 BZDU E[[[U[O 作者 简 介S胡 静 珍eTfdfghG女e汉 族hG浙江永康人GE[[T年毕业于复 旦大学电子工程系电子学与信息系 统专业G现在中科院上海技术 物 理 研究所攻读硕士学位G主要研 究 领 域有S红外系统研究G数据的采集及 处理G星载整机及器件研究等! Ec. 胡静珍等S深亚微米数字集成电路的自动化设计方法学 E[[E年