正在加载图片...

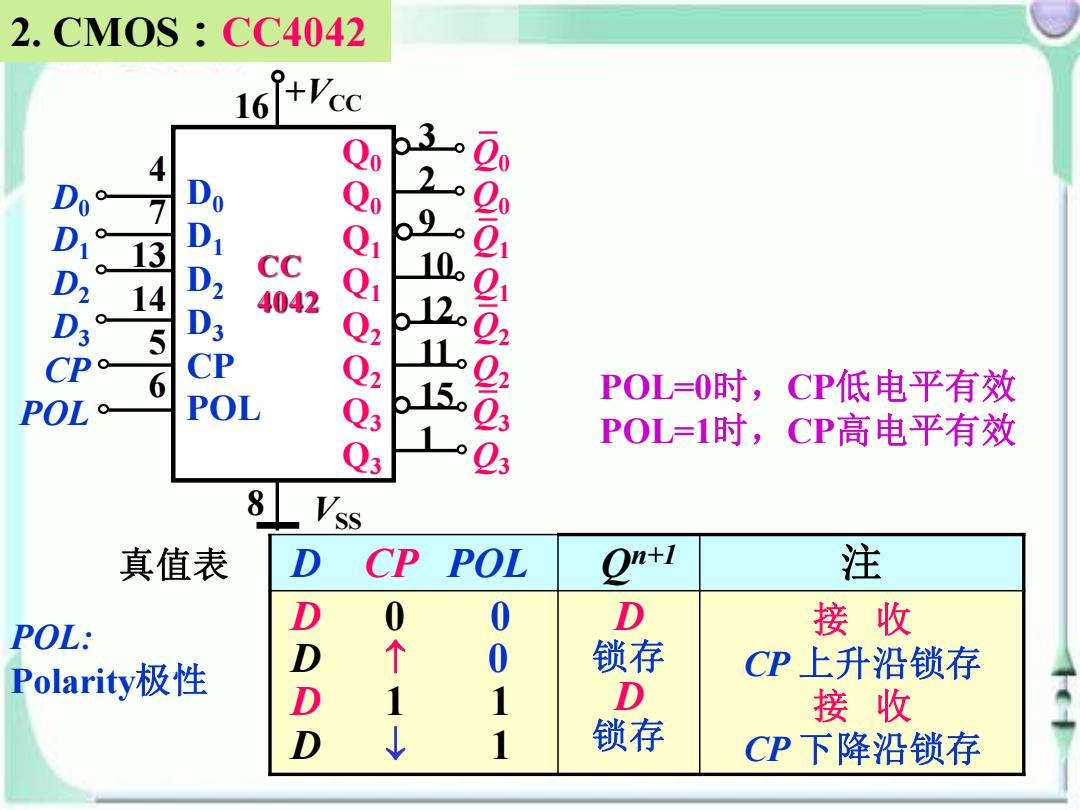

2.CM0S:CC4042 16 +Vcc 4 D 2 P PO 适220215L POL=0时,CP低电平有效 POL=1时,CP高电平有效 8 Vss 真值表 D CP POL 注 D 0 0 D POL: 接收 0 Polarity极性 D 个 锁存 CP上升沿锁存 D 1 1 D 接收 D ↓ 1 锁存 CP下降沿锁存+VCC D0 D1 D2 D3 CP POL Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3 4 7 13 14 5 6 3 2 9 10 12 11 15 1 Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3 – – – – D0 D1 D2 D3 CP POL 8 16 VSS CC 4042 真值表 D CP POL Qn+1 注 D 0 0 D 0 D 1 1 D 1 D 锁存 D 锁存 接 收 CP 上升沿锁存 接 收 CP 下降沿锁存 2. CMOS:CC4042 POL: Polarity极性 POL=0时,CP低电平有效 POL=1时,CP高电平有效