数字电子技术 5.2 同步触发器 基本RS触发器也被称为直接置位、复位触发器。 同步触发器:触发器的工作状态不仅受输入端(R、S) 控制,而且还受时钟脉冲(CP)的限制。 CP(Clock Pulse):时钟脉冲信号。 同步触发器: 同步RS触发器 同步D触发器 5.2.1同步RS触发器

同步触发器:触发器的工作状态不仅受输入端 (R、S) 控制,而且还受时钟脉冲(CP) 的限制。 CP (Clock Pulse): 时钟脉冲信号。 基本 RS 触发器也被称为直接置位、复位触发器。 同步触发器: 同步 RS 触发器 同步 D 触发器 5.2 同步触发器 5.2.1 同步 RS 触发器

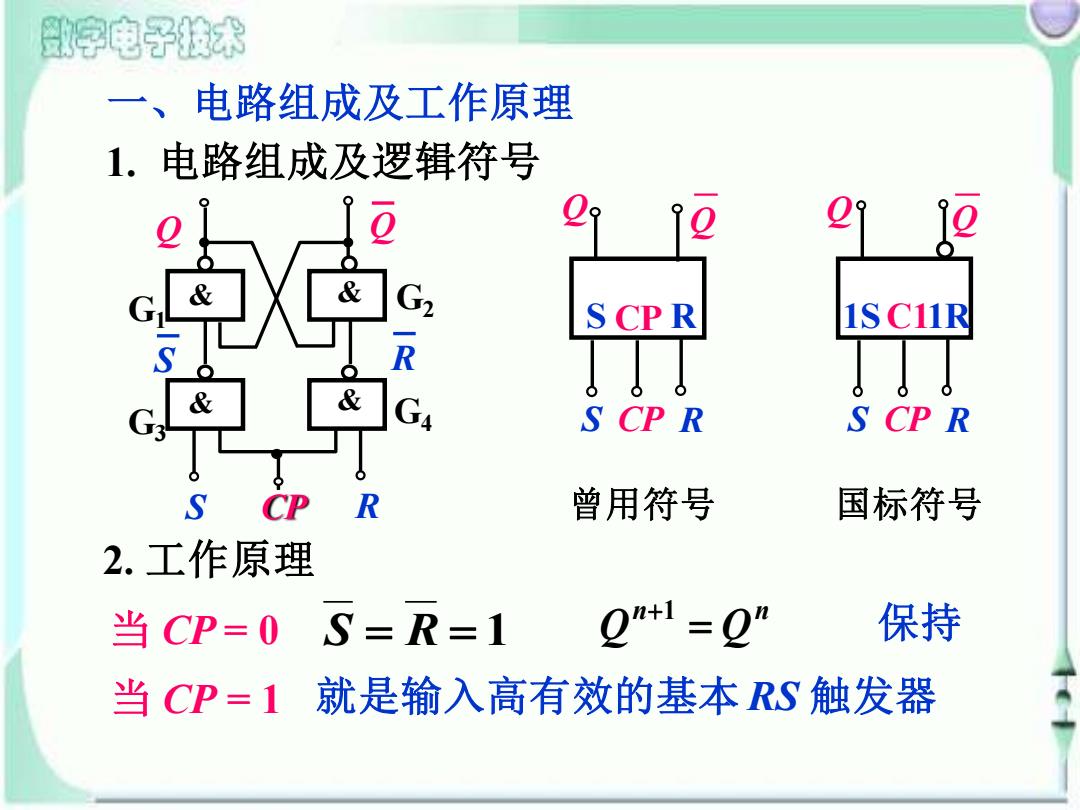

数字电子技术 一、电路组成及工作原理 1.电路组成及逻辑符号 & S CPR 1S C11R & & S CP R S CP R R 曾用符号 国标符号 2.工作原理 当CP=0S=R=1 2+1=Q” 保持 当CP=1就是输入高有效的基本RS触发器

一、电路组成及工作原理 1. 电路组成及逻辑符号 Q G1 R & & S Q G3 R & & S G2 G4 CP 曾用符号 Q Q S R S CP R CP 国标符号 Q Q 1S 1R S CP R C1 2. 工作原理 当 CP = 0 S = R = 1 n n Q = Q +1 保持 当 CP = 1 就是输入高有效的基本 RS 触发器

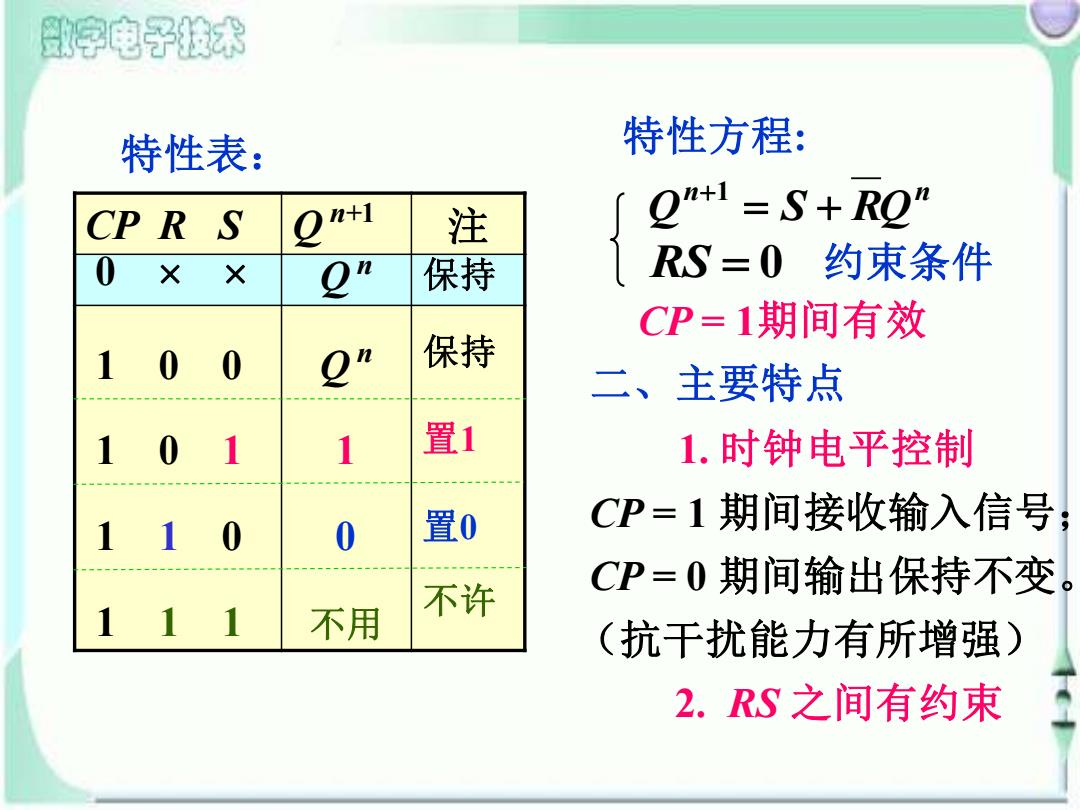

数字电子技术 特性表: 特性方程: CP R S 2 n+1 注 [2"+1=S+R0m × × On 保持 1RS=0约束条件 CP=1期间有效 保持 二、主要特点 1 置1 1.时钟电平控制 CP=1期间接收输入信号 0 0 置0 CP=0期间输出保持不变 不许 111 不用 (抗干扰能力有所增强) 2.RS之间有约束

特性表: CP R S Q n+1 注 0 Q n 保持 1 0 0 1 0 1 1 1 0 1 1 1 Q n 1 0 不用 保持 置1 置0 不许 特性方程: n n Q = S + RQ +1 RS = 0 约束条件 CP = 1期间有效 二、主要特点 1. 时钟电平控制 CP = 1 期间接收输入信号; CP = 0 期间输出保持不变。 (抗干扰能力有所增强) 2. RS 之间有约束

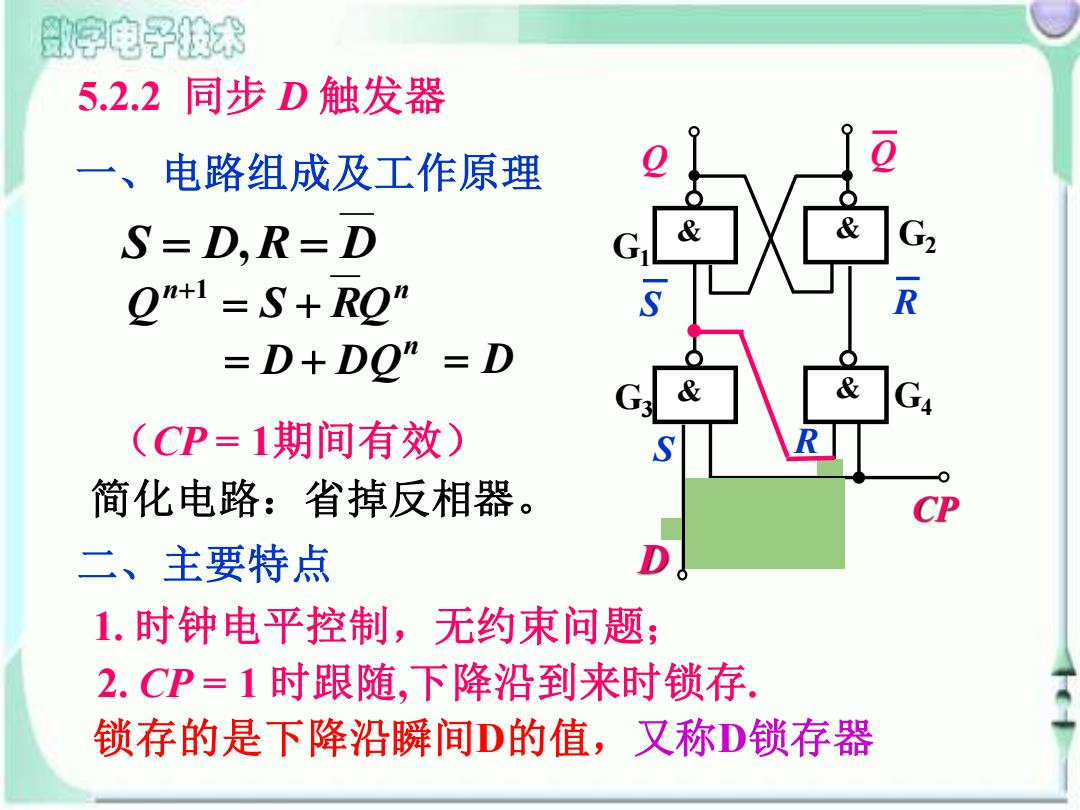

数字电子发术 5.2.2同步D触发器 一、电路组成及工作原理 S=D,R-D 2+1=S+Fg" R =D+DQ”=D & & (CP=1期间有效) 简化电路:省掉反相器 。 CP 二、主要特点 1.时钟电平控制,无约束问题; 2.CP=1时跟随,下降沿到来时锁存 锁存的是下降沿瞬间D的值,又称D锁存器

5.2.2 同步 D 触发器 一、电路组成及工作原理 Q G1 R & & S Q G3 R & & S G2 G4 1 CP D S = D,R = D n n Q = S + RQ +1 n = D + DQ = D (CP = 1期间有效) 简化电路:省掉反相器。 二、主要特点 1. 时钟电平控制,无约束问题; 2. CP = 1 时跟随,下降沿到来时锁存. 锁存的是下降沿瞬间D的值,又称D锁存器

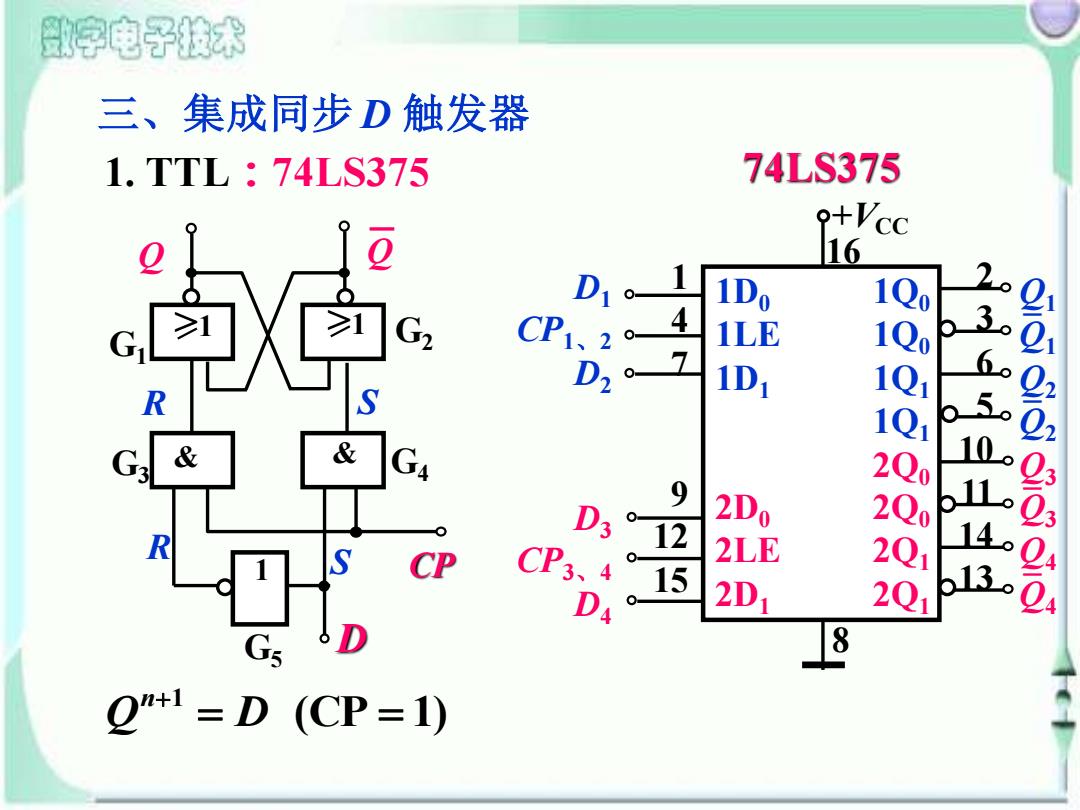

数字电子技术 三、集成同步D触发器 1.TTL:74LS375 74LS375 9+Vcc 16 1 1D0 CP 、2 1LE 1D1 R & & 4 9 D; R 12 CP3、4 2LE 15 4 2D1 201 Q Q+1=D(CP=1)

三、集成同步 D 触发器 1. TTL:74LS375 CP D Q G1 Q G3 R & & S G2 G4 1 >1 >1 G5 R S 1 (CP 1) n Q D + = = +VCC 74LS375 1D0 1LE 1D1 2D0 2LE 2D1 1Q0 1Q0 1Q1 1Q1 2Q0 2Q0 2Q1 2Q1 1 4 7 9 12 15 2 3 6 5 10 11 14 13 Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 – – – – D1 CP1、2 D2 D3 CP3、4 D4 8 16

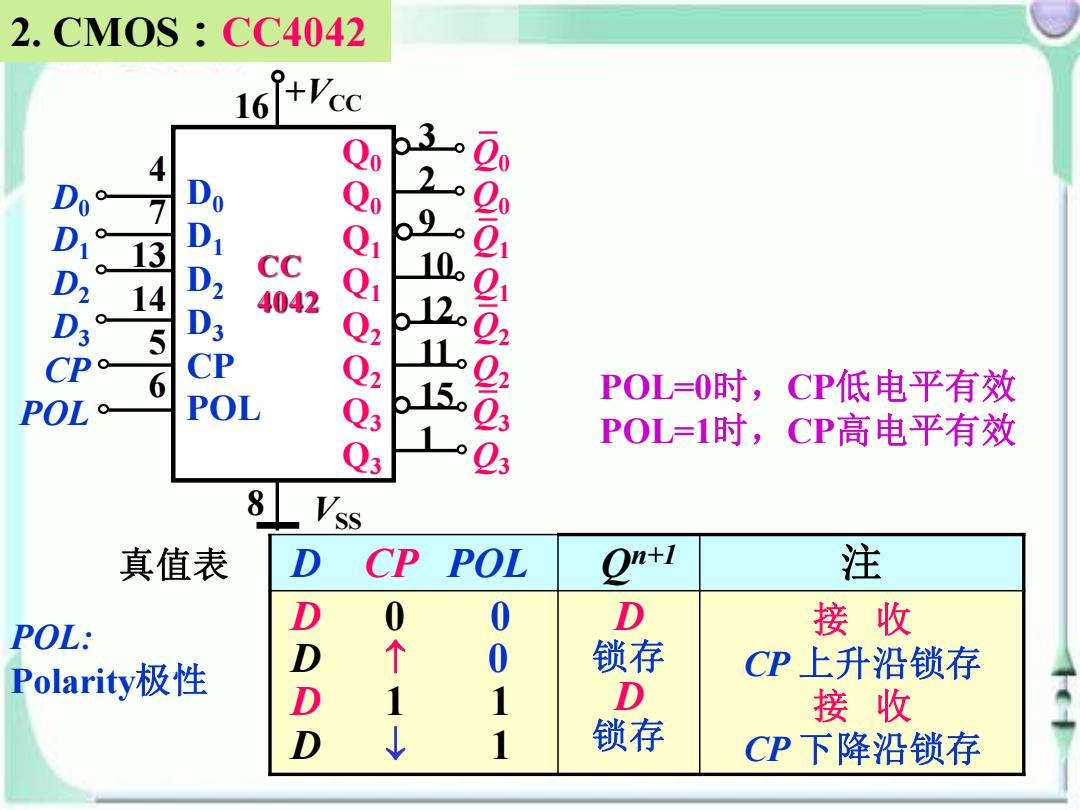

2.CM0S:CC4042 16 +Vcc 4 D 2 P PO 适220215L POL=0时,CP低电平有效 POL=1时,CP高电平有效 8 Vss 真值表 D CP POL 注 D 0 0 D POL: 接收 0 Polarity极性 D 个 锁存 CP上升沿锁存 D 1 1 D 接收 D ↓ 1 锁存 CP下降沿锁存

+VCC D0 D1 D2 D3 CP POL Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3 4 7 13 14 5 6 3 2 9 10 12 11 15 1 Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3 – – – – D0 D1 D2 D3 CP POL 8 16 VSS CC 4042 真值表 D CP POL Qn+1 注 D 0 0 D 0 D 1 1 D 1 D 锁存 D 锁存 接 收 CP 上升沿锁存 接 收 CP 下降沿锁存 2. CMOS:CC4042 POL: Polarity极性 POL=0时,CP低电平有效 POL=1时,CP高电平有效