数字电子技术 上一堂课的问题 0.触发器的0状态与1状态的定义。 1.写出RS触发器的特征方程 。 2.说出基本RS触发器与同步RS触发器的不同。 3.写出D触发器的特性方程。 4.说出同步D触发器和边沿D触发器的不同

上一堂课的问题 0.触发器的0状态与1状态的定义。 1.写出RS触发器的特征方程。 2.说出基本RS触发器与同步RS触发器的不同。 3.写出D触发器的特性方程。 4.说出同步D触发器和边沿D触发器的不同

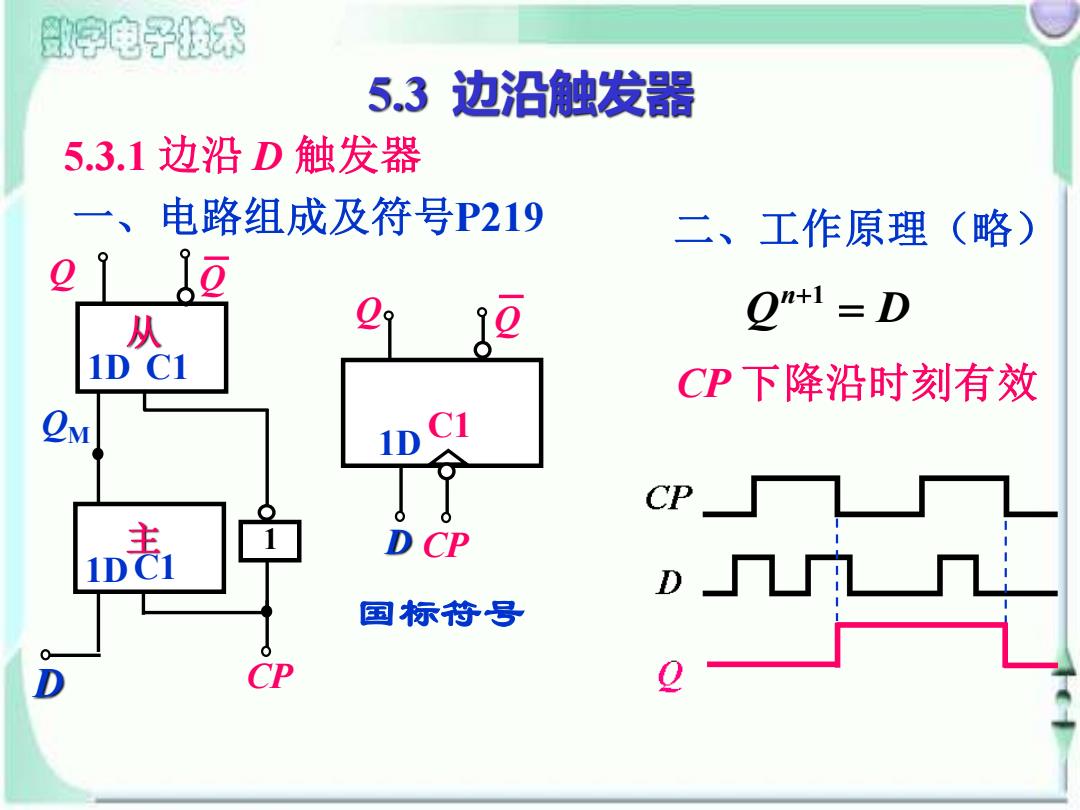

字电子技术 5.3 边沿触发器 5.3.1边沿D触发器 一、电路组成及符号P219 二、工作原理(略) 21 从 2 Q+1=D 1D C1 CP下降沿时刻有效 D CP 国标符号 CP

国标符号 5.3 边沿触发器 5.3.1 边沿 D 触发器 一、电路组成及符号P219 QM CP Q Q 1D C1 1D C1 1 D 从 主 Q Q CP C1 1D D 二、工作原理(略) n 1 Q D + = CP 下降沿时刻有效

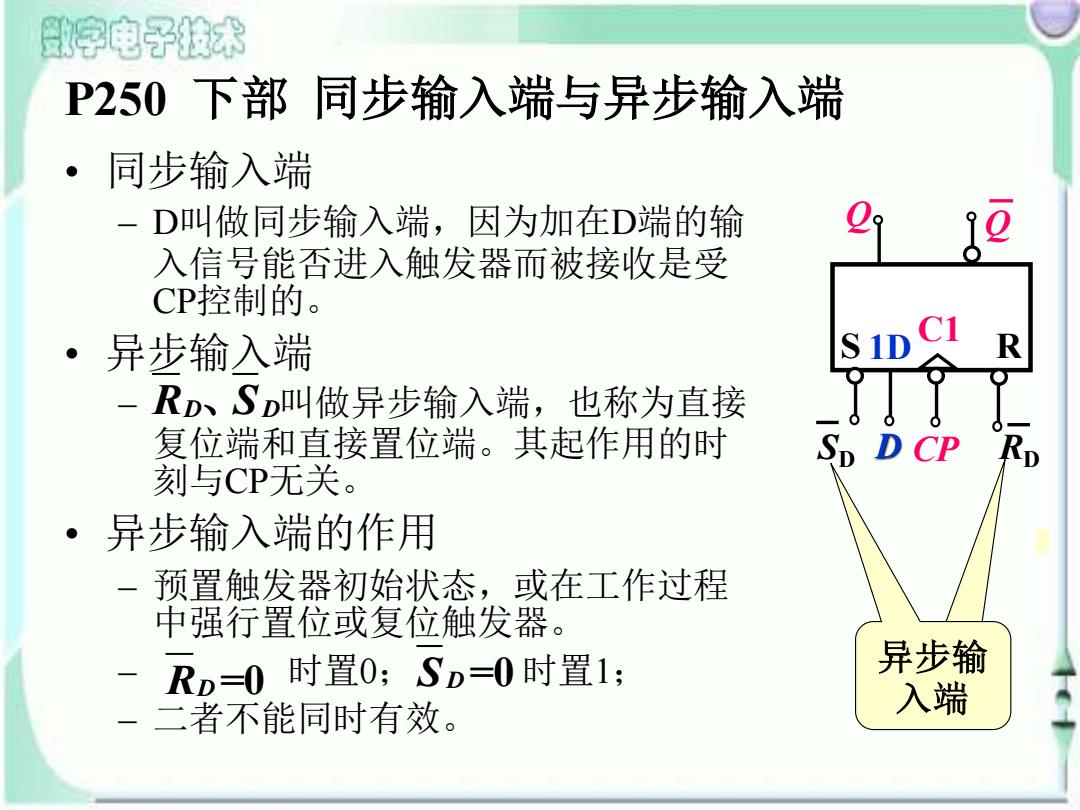

数字电子技术 P250下部同步输入端与异步输入端 同步输入端 D叫做同步输入端,因为加在D端的输 入信号能否进入触发器而被接收是受 CP控制的。 异步输入端 S1D R RD、SD叫做异步输入端,也称为直接 复位端和直接置位端。其起作用的时 D CP 刻与CP无关。 异步输入端的作用 预置触发器初始状态,或在工作过程 中强行置位或复位触发器。 RD=0时置0;SD=0时置1; 异步输 二者不能同时有效。 入端

P250 下部 同步输入端与异步输入端 • 同步输入端 – D叫做同步输入端,因为加在D端的输 入信号能否进入触发器而被接收是受 CP控制的。 • 异步输入端 – 叫做异步输入端,也称为直接 复位端和直接置位端。其起作用的时 刻与CP无关。 • 异步输入端的作用 – 预置触发器初始状态,或在工作过程 中强行置位或复位触发器。 – 时置0; 时置1; – 二者不能同时有效。 R S D、 D Q Q CP C1 1D D S R SD RD 异步输 RD =0 入端 S D =0

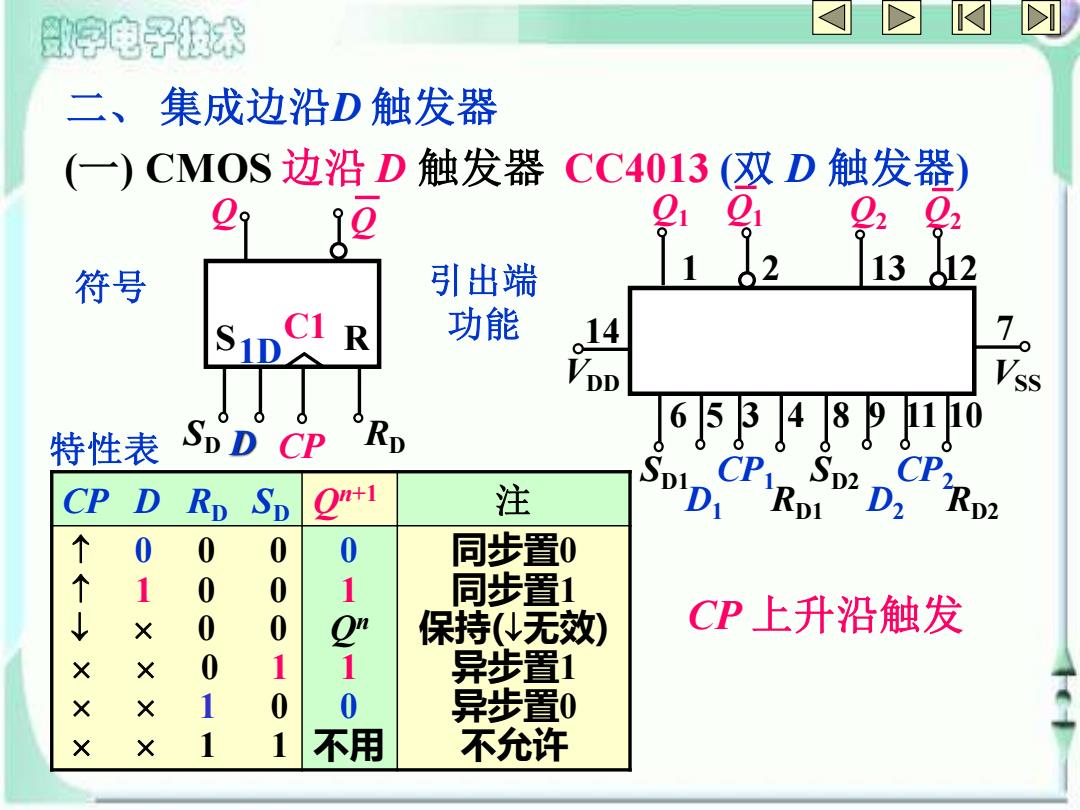

数字电子技术 二、集成边沿D触发器 (一)CMOS边沿D触发器 CC4013(双D触发器) 02 92 符号 引出端 2 13 12 C1 功能 14 1 DD 89 1110 特性表 SD D CP 6534 SD2 CP CP D Rp Sp Q+1 注 D 个 0 0 0 0 同步置0 个 1 0 0 1 同步置1 ↓ 0 0 保持无效) CP上升沿触发 × X 0 1 1 异步置1 × 1 0 0 异步置0 × X 1 1 不用 不允许

二、 集成边沿D 触发器 (一) CMOS 边沿 D 触发器 CC4013 (双 D 触发器) 符号 引出端 功能 Q1 Q1 VDD SD1 CP1 SD2 CP2 D1 RD1 D2 RD2 Q2 Q2 VSS 6 5 3 4 8 9 11 10 1 2 13 12 14 7 特性表 CP D RD SD Qn+1 注 0 0 0 1 0 0 0 0 0 1 1 0 1 1 0 1 Qn 1 0 不用 同步置0 同步置1 保持(无效) 异步置1 异步置0 不允许 CP 上升沿触发 Q Q CP C1 1D D S R SD RD

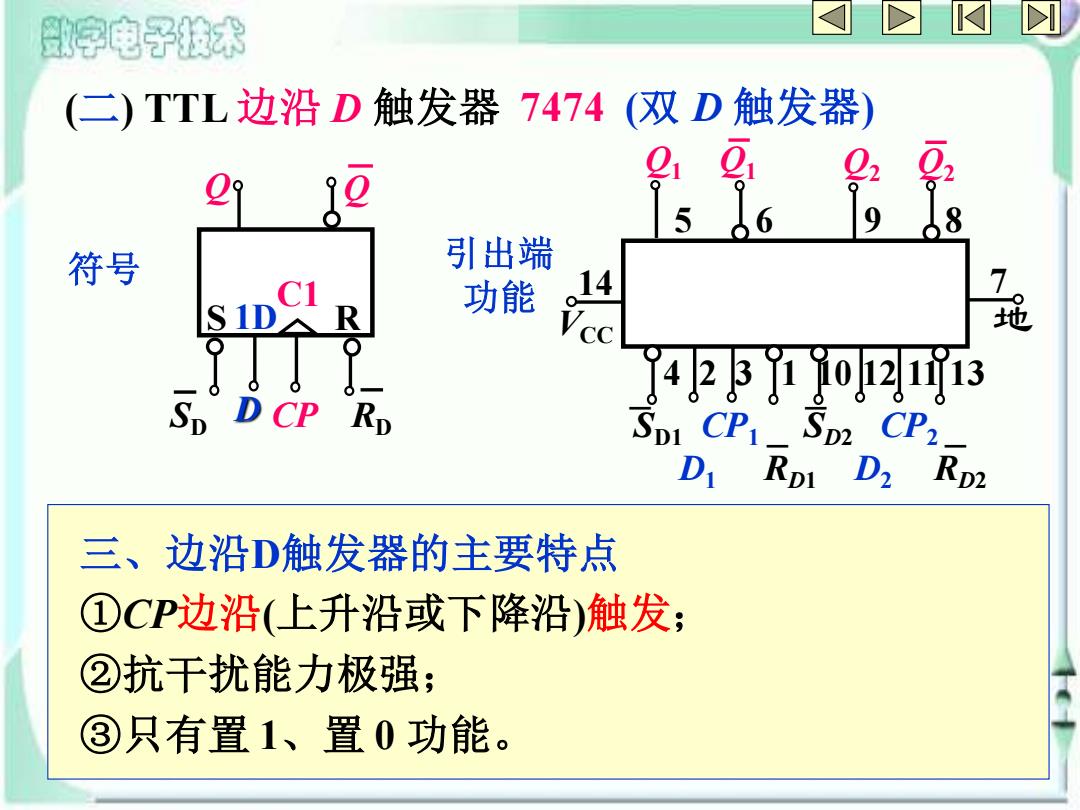

数字电子发术 (二)TTL边沿D触发器7474(双D触发器) 5 9 8 符号 引出端 C1 14 7 R 功能 地 42311023 D SD CP Rp CP2 D2 RD2 三、边沿D触发器的主要特点 ①CP边沿(上升沿或下降沿)触发; ②抗干扰能力极强; ③只有置1、置0功能

(二) TTL 边沿 D 触发器 7474 (双 D 触发器) 符号 引出端 功能 Q1 Q1 VCC SD1 CP1 SD2 CP2 D1 RD1 D2 RD2 Q2 Q2 地 4 2 3 1 10 12 11 13 5 6 9 8 14 7 – – – – 三、边沿D触发器的主要特点 ①CP边沿(上升沿或下降沿)触发; ②抗干扰能力极强; ③只有置 1、置 0 功能。 Q Q CP C1 1D D S R SD RD

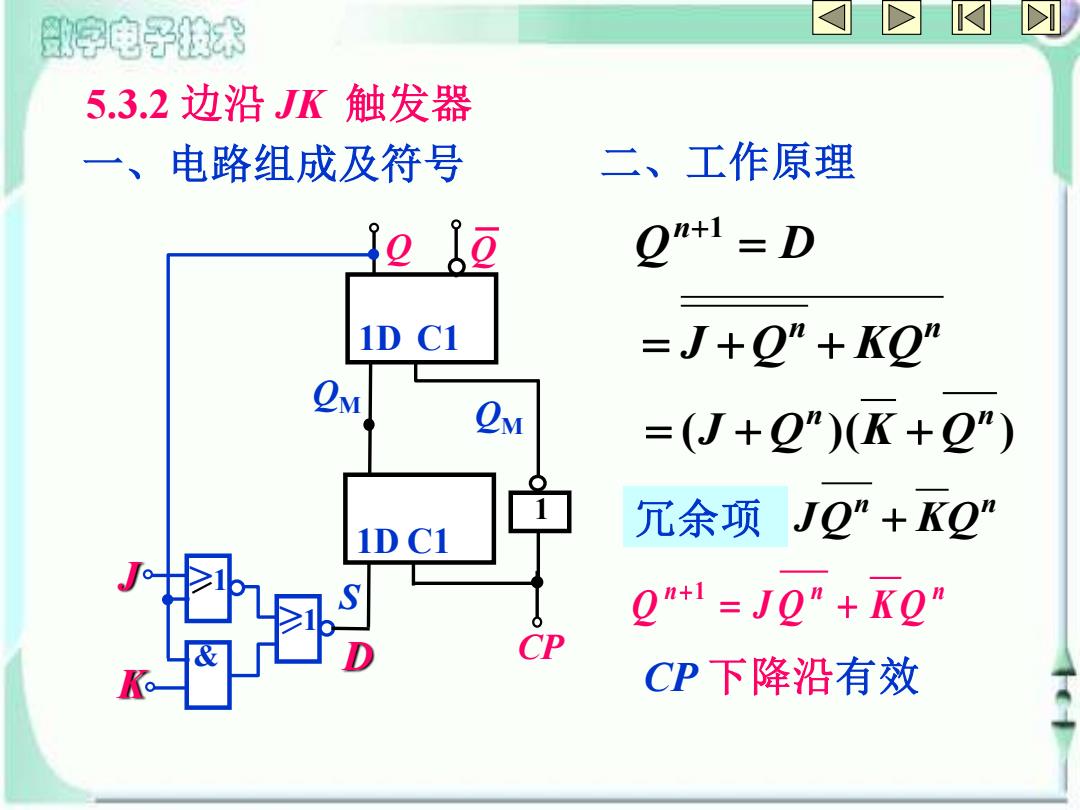

数字电子发术 5.3.2边沿JK触发器 一、电路组成及符号 二、工作原理 1 2"+1=D 1D C1 =J+Q”+KQ” =(J+2”)K+2”) 1D C1 冗余项JQ”+KQ” Q"+1=JQ”+KQ" CP K。 CP下降沿有效

5.3.2 边沿 JK 触发器 一、电路组成及符号 二、工作原理 QM QM CP S Q Q 1D C1 1D C1 1 D >1 >1 & J K Q D n = +1 n n = J +Q + KQ ( )( ) n n = J + Q K + Q n n = JK + JQ + KQ n n n Q = J Q + KQ +1 冗余项 CP 下降沿有效

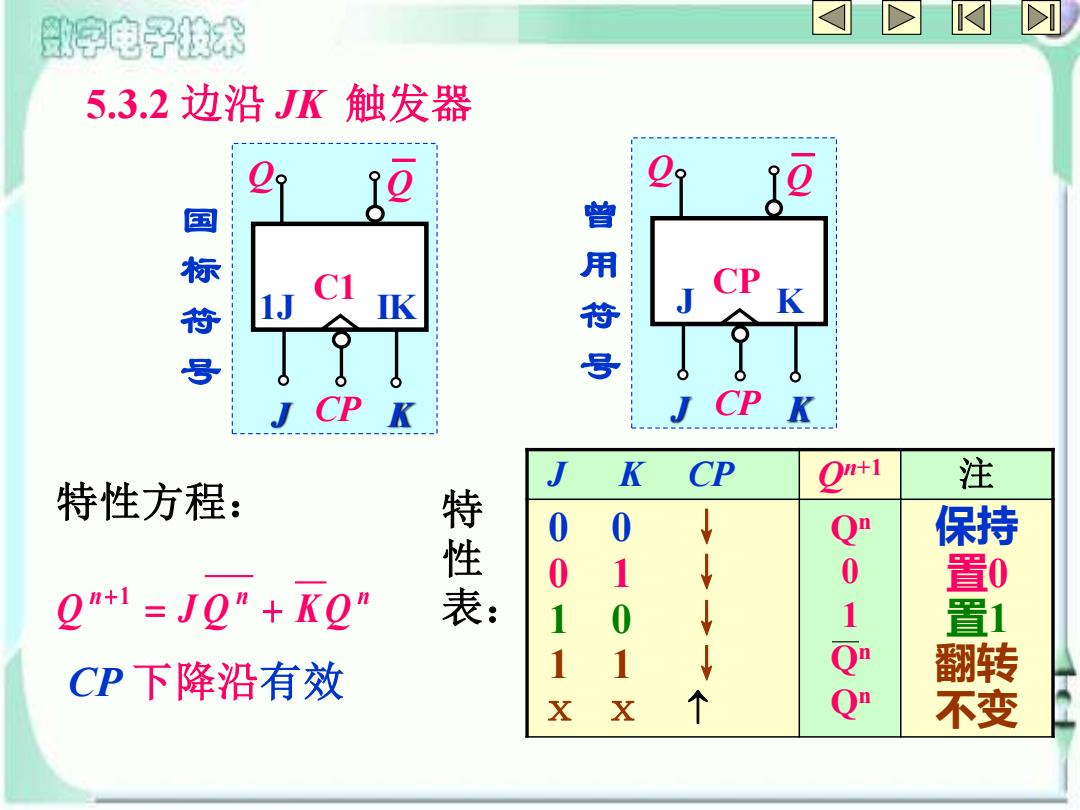

数字电子发术 5.3.2边沿JK触发器 标符号 1J C1 K 曾用符号 CP K CP K J K CP Q+1 注 特性方程: 特性表 0 0 保持 0 1 0 2"+1=J2”+KQ” 1 0 1 CP下降沿有效 1 1 翻转 X X 个 8 不

5.3.2 边沿 JK 触发器 n n n Q = J Q + KQ +1 CP 下降沿有效 Q Q CP CP J K J K 曾 用 符 号 国 标 符 号 Q Q CP C1 1J IK J K 特性方程: 特 性 表: J K CP Qn+1 注 0 0 ↓ 0 1 ↓ 1 0 ↓ 1 1 ↓ ⅹ ⅹ Qn 0 1 Qn Qn 保持 置0 置1 翻转 不变

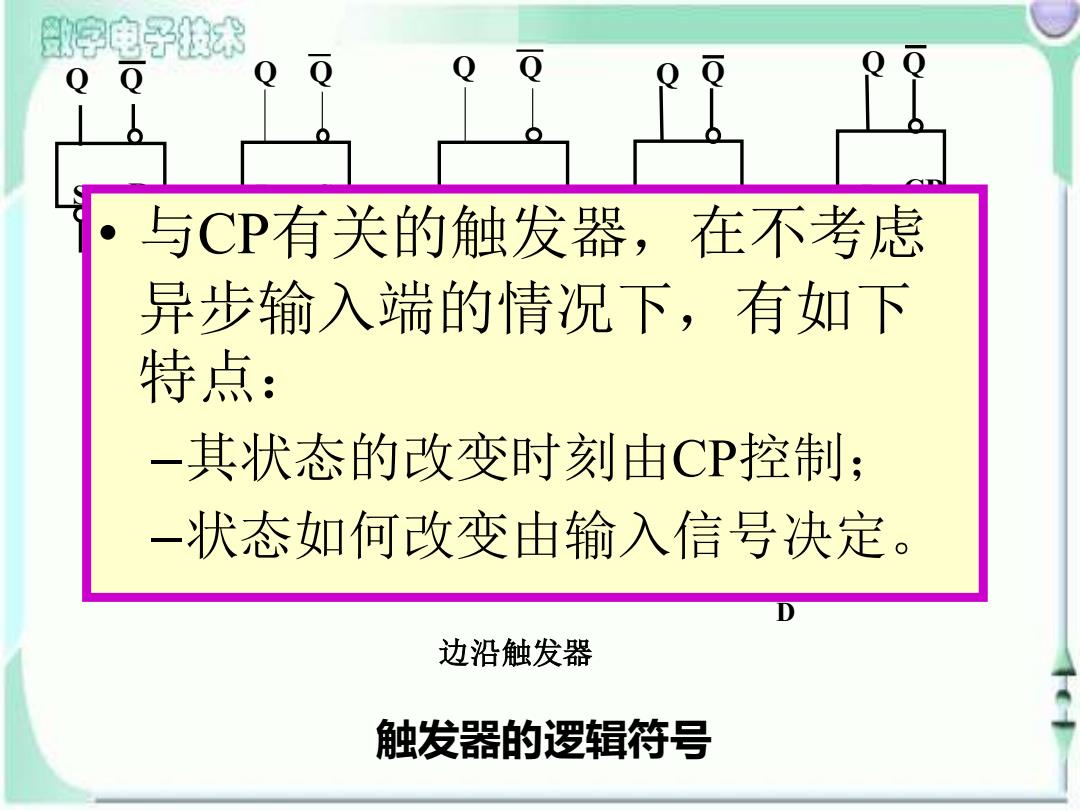

数字电子技术 与CP有关的触发器,在不考虑 异步输入端的情况下,有如下 特点: 一其状态的改变时刻由CP控制; 一状态如何改变由输入信号决定。 边沿触发器 触发器的逻辑符号

触发器的逻辑符号 1D Q Q C1 C1 1J 1K Q Q R S Q Q 基本触发器 Q S R Q D CP Q Q S R Q Q CP 同步触发器 RD SD C1 CP 1D D Q Q D Q Q CP • 与CP有关的触发器,在不考虑 异步输入端的情况下,有如下 特点: –其状态的改变时刻由CP控制; –状态如何改变由输入信号决定。 边沿触发器

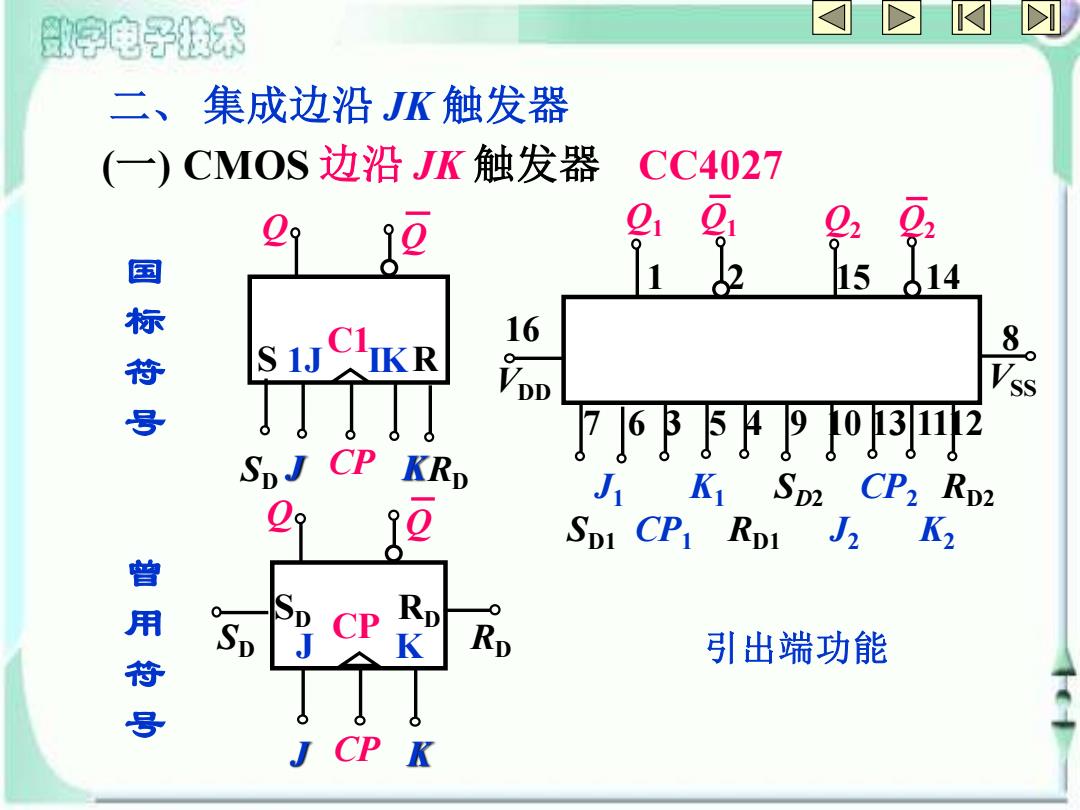

做字电子发术 二、集成边沿JK触发器 (一)CMOS边沿JK触发器 CC4027 ¥15 2 014 国标符号 S1JCIIKR 16 8 7635902 SpJ CP J K CP2 RD2 SDI CP1 RDI 曾用符号 Sp CP p Rp 引出端功能 CP K

二、 集成边沿 JK 触发器 (一) CMOS 边沿 JK 触发器 CC4027 国 标 符 号 曾 用 符 号 Q Q CP C1 1J IK J K S R SD RD Q Q CP CP J K J K SD RD SD RD 引出端功能 Q1 Q1 VDD J1 K1 SD2 CP2 RD2 SD1 CP1 RD1 J2 K2 Q2 Q2 VSS 7 6 3 5 4 9 10 13 1112 1 2 15 14 16 8

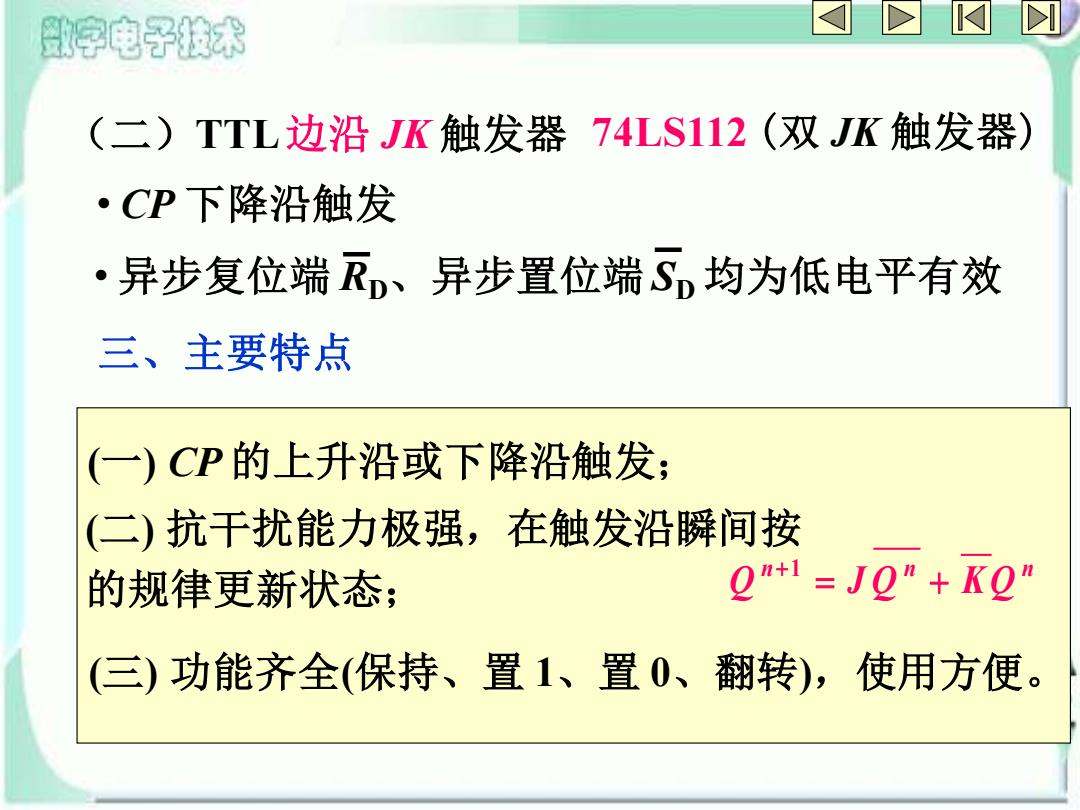

数字电子技术 (二)TTL边沿JK触发器74LS112(双JK触发器 ·CP下降沿触发 ·异步复位端RD、异步置位端SD均为低电平有效 三、主要特点 (一)CP的上升沿或下降沿触发; (二)抗干扰能力极强,在触发沿瞬间按 的规律更新状态; 2nt1=Jom+Ko (三)功能齐全(保持、置1、置0、翻转),使用方便

(二)TTL 边沿 JK 触发器 • CP 下降沿触发 • 异步复位端 RD、异步置位端 SD 均为低电平有效 74LS112 (双 JK 触发器) 三、主要特点 (一) CP 的上升沿或下降沿触发; (二) 抗干扰能力极强,在触发沿瞬间按 的规律更新状态; n n n Q = J Q + KQ +1 (三) 功能齐全(保持、置 1、置 0、翻转),使用方便