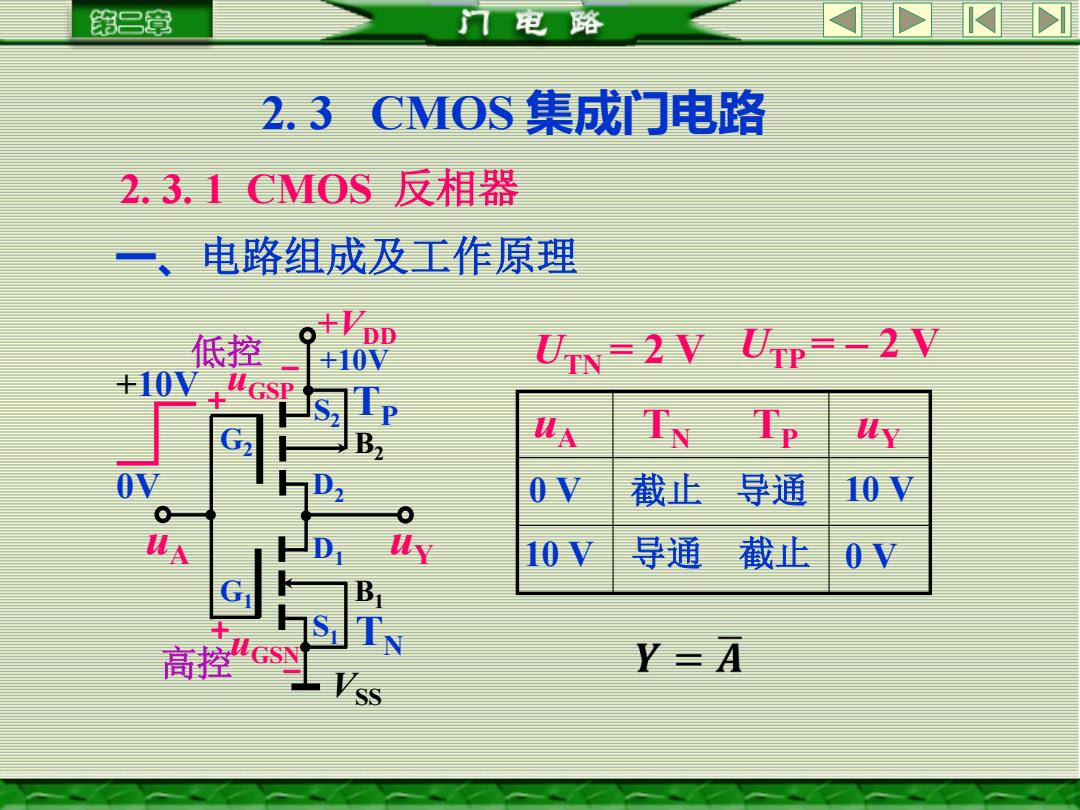

第二章 门电路 2.3CMOS集成门电路 2.3.1CM0S反相器 一、电路组成及工作原理 低控 +10V UTN=2Y UTP=-2Y +10V WGSP S, G TN TP 截止导通 10V D 10V 导通截止 G 高控Gs Y=A SS

+VDD +10V G1 B1 D1 S1 uA uY TN TP B2 D2 S2 G2 VSS + - uGSN + u - GSP 2. 3 CMOS 集成门电路 2. 3. 1 CMOS 反相器 一、电路组成及工作原理 0V +10V uA TN TP uY 0 V 截止 导通 10 V 10 V 导通 截止 0 V UTN = 2 V UTP = - 2 V 高控 低控

第二章 门■电路 二、静态特 本D 本D 1.输入特性 本D 正常工作时 0≤4,≤VpD (a) i≈0 uI VDD upF 或山,<-IlpF VDD+UDE 保护电路工作, 此时迅速增加。 (b) (c) U继续增加 反相器损环。 图2.3.3 CMOS反相器 (a)电路图 (b)示意图 (c)输入特性

二、静态特性 1.输入特性 正常工作时: 0 0 I DD I u V i 保护电路工作, 此时i I迅速增加。 uI继续增加, 反相器损坏。 I DD DF I DF u V u u u + 或 -

第二章 门电路 反相器外接负载时 +VpD 的两种情况 1.输出高电平,带 拉电流负载。(a) LO om能够输出的最大电 流,称为带拉电流负 (a) 载的能力。 +VpD 2.输出低电平,带 灌电流负载。(b) R R DD oL允许灌入的最大电 流,称为带灌电流负 载的能力。 Vo减小时,输出高电 平会下降,输出低电 (b) 平会上升。带负载能 变券

2.输出特性 反相器外接负载时 的两种情况: 1.输出高电平,带 拉电流负载。( a ) IOH能够输出的最大电 流,称为带拉电流负 载的能力。 2.输出低电平,带 灌电流负载。( b ) IOL允许灌入的最大电 流,称为带灌电流负 载的能力。 VDD减小时,输出高电 平会下降,输出低电 平会上升。带负载能 力变差

第二章 门电路 3传输特性 ()典型值 输入输出端高电平的典型值VoD,低电平的典 型值为0V。 (2)输入端噪声容限 噪声容限指o为规定值时,允许u波动的最大范围。 般取JNL-UNH0.3Vbo

3.传输特性 (1)典型值 输入/输出端高电平的典型值VDD,低电平的典 型值为0V。 (2)输入端噪声容限 噪声容限指uO为规定值时,允许uI波动的最大范围。 一般取UNL=UNH=0.3VDD

第二章 门电路 三、动态特性 1.传输延迟时间 t=2 +VpD 50% ---50% PHL EPLH (a) (b) 图2.3.6 CMOS反相器的传输时间 (a)电路图 (b)波形图

三、动态特性 1.传输延迟时间 2 PHL PLH pd t t t + =

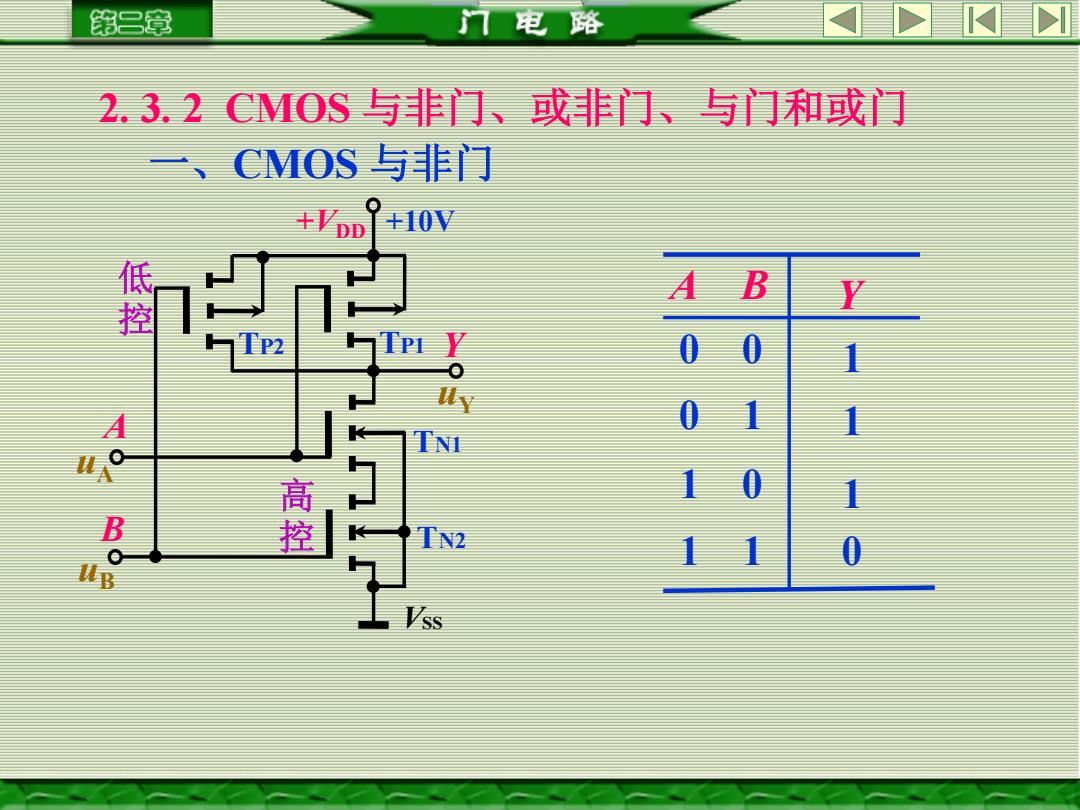

第吕章 门电路 2.3.2CM0S与非门、或非门、与门和或门 一、CMOS与非门 +10V 低控 A B TP2 00 0 意 TN2 0

2. 3. 2 CMOS 与非门、或非门、与门和或门 A B Y 0 0 0 1 1 0 1 1 1 1 1 0 一、CMOS 与非门 uA +VDD +10V VSS TP1 TN1 TP2 TN2 A B Y uB uY 高 控 低 控

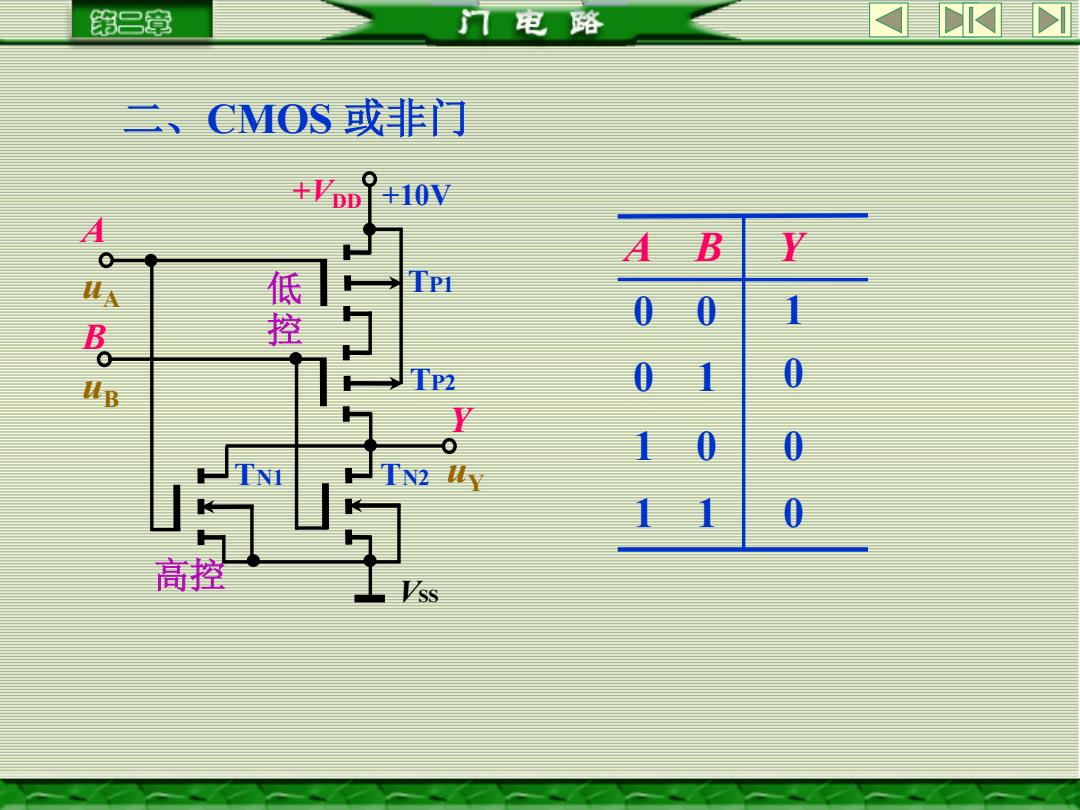

第吕章 门电路 二、CMOS或非门 DD +10V A A B 6 公 低控 0 0 露 TP2 0 0 0 高控

二、CMOS 或非门 u A + VDD +10V VSS TP1 TN1 TN2TP2 AB Y u B u Y A B Y 0 0 0 1 1 0 1 1 1000 高控 低控

第二章 门电路 ·与门由与非门和非门构成 ·或门由或非门和非门构成 ·与或非门由与非门和非门构成 ·异或门由或非门、与非门和非门构成

• 与门由与非门和非门构成 • 或门由或非门和非门构成 • 与或非门由与非门和非门构成 • 异或门由或非门、与非门和非门构成

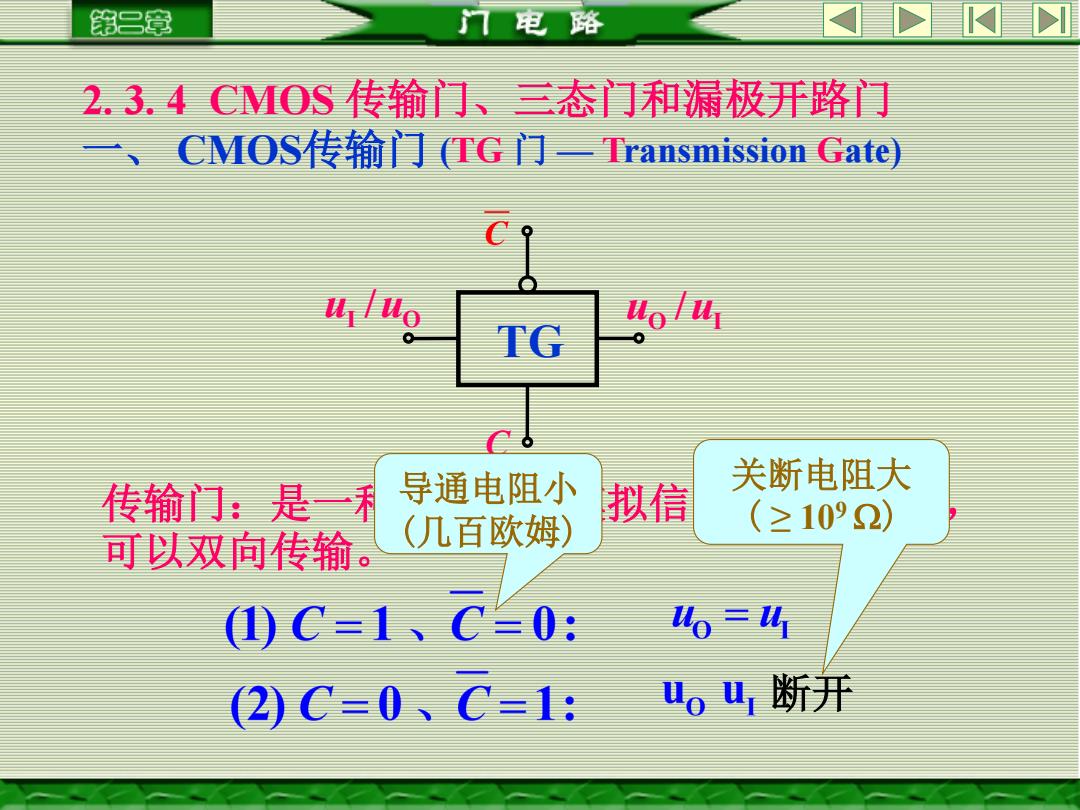

第二章 门电路 2.3.4CMOS传输门、三态门和漏极开路门 CMOS传输门(TG门一ransmission Gate) TG 关断电阻大 传输门:是一 导通电阻小 拟信 可以双向传输 (几百欧姆) (≥1092) 1)C-1、C=0: 6=4 2)C=0、C=1: o断开

2. 3. 4 CMOS 传输门、三态门和漏极开路门 一、 CMOS传输门 C O I uI /uO u / u TG 传输门:是一种能够传送模拟信号的压控开关, 可以双向传输。 (TG 门 — Transmission Gate) 断开 导通电阻小 (几百欧姆) 关断电阻大 ( ≥ 109 )

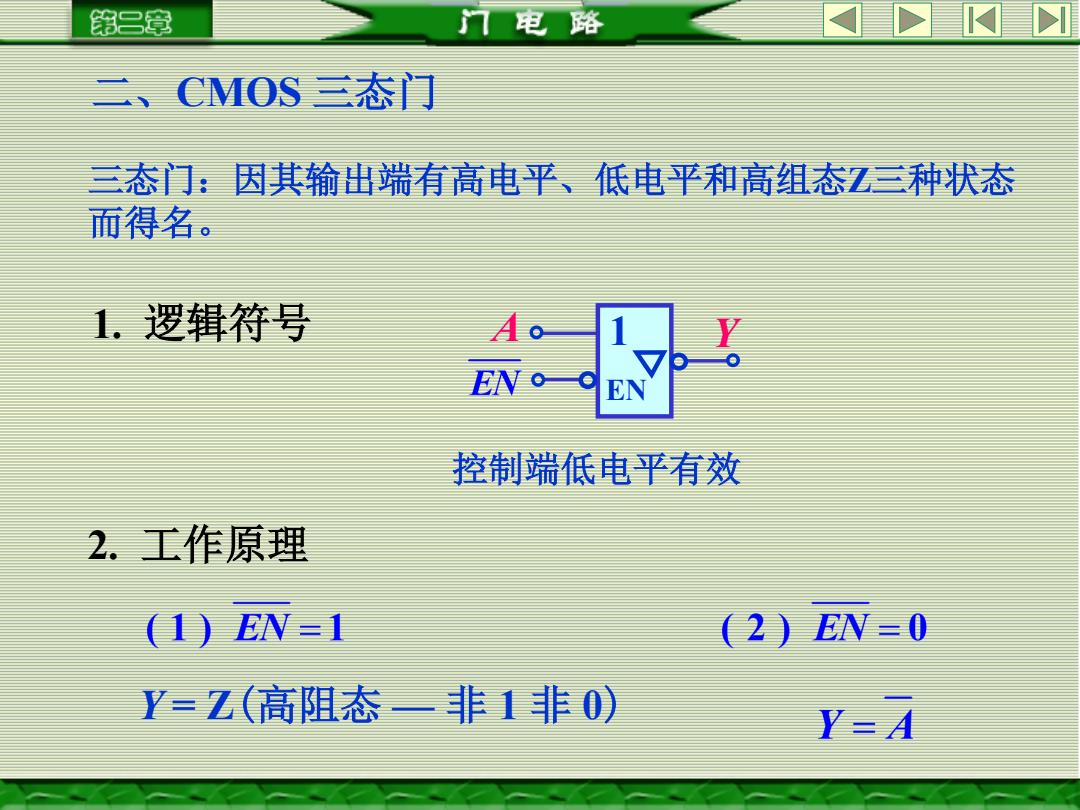

第二章 门电路 CMOS三态门 三态门:因其输出端有高电平、低电平和高组态☑三种状态 而得名。 1.逻辑符号 控制端低电平有效 2.工作原理 (1)N=1 (2)EN=0 Y=Z(高阻态一非1非0) Y=A

二、CMOS 三态门 2. 工作原理 Y = Z(高阻态 — 非 1 非 0) 控制端低电平有效 1. 逻辑符号 A 1 Y EN 三态门:因其输出端有高电平、低电平和高组态Z三种状态 而得名