数字电子技术 第五章 第五章小结 触发器和门电路一样,也是组成数字电路的基 本逻辑单元。它有两个基本特性: 1.有两个稳定的状态(0状态和1状态)。 2.在外信号作用下,两个稳定状态可相互转换;没 有外信号作用时,保持原状态不变。 因此,触发器具有记忆功能,常用来保存二进制信息。 二、触发器的逻辑功能 指触发器的次态Q+1与现态Q"及输入信号之间 的逻辑关系 。 其描述方法主要有特性表、卡诺图、特性方程、 状态图和时序图

第五章 触发器 第五章 小 结 一、触发器和门电路一样,也是组成数字电路的基 本逻辑单元。它有两个基本特性: 1. 有两个稳定的状态(0 状态和 1 状态)。 2. 在外信号作用下,两个稳定状态可相互转换;没 有外信号作用时,保持原状态不变。 因此,触发器具有记忆功能,常用来保存二进制信息。 二、触发器的逻辑功能 指触发器的次态 Qn+1 与现态 Qn 及输入信号之间 的逻辑关系。 其描述方法主要有特性表、卡诺图、特性方程、 状态图和时序图

数字电子技术 第五章 二、触发器的分类 1.根据电路结构不同,触发器可分为 (1)基本触发器: 输入信号电平直接控制。 特性方程 Q"1=S+RQ” RS=0(约束条件) (2)同步触发器:时钟电平直接控制。 CP=1(或0)时有效 2+1=S+RQ 特性方程 同步RS触发器 RS=0 Q =D 同步D触发器

第五章 触发器 二、触发器的分类 1. 根据电路结构不同,触发器可分为 (1)基本触发器:输入信号电平直接控制。 特性方程 RS = 0 n n Q = S + RQ +1 (2)同步触发器:时钟电平直接控制。 特性方程 RS = 0 n n Q = S + RQ +1 同步 RS 触发器 CP = 1(或 0)时有效 Q D n = +1 同步 D 触发器 (约束条件)

数字电子技术 第五章触发器 (3)边沿触发器:时钟边沿控制。 CP上升沿(或下降沿)时刻有效 特性方程 2+1=D 边沿D触发器 2"+1=J0”+KQ” 边沿JK触发器

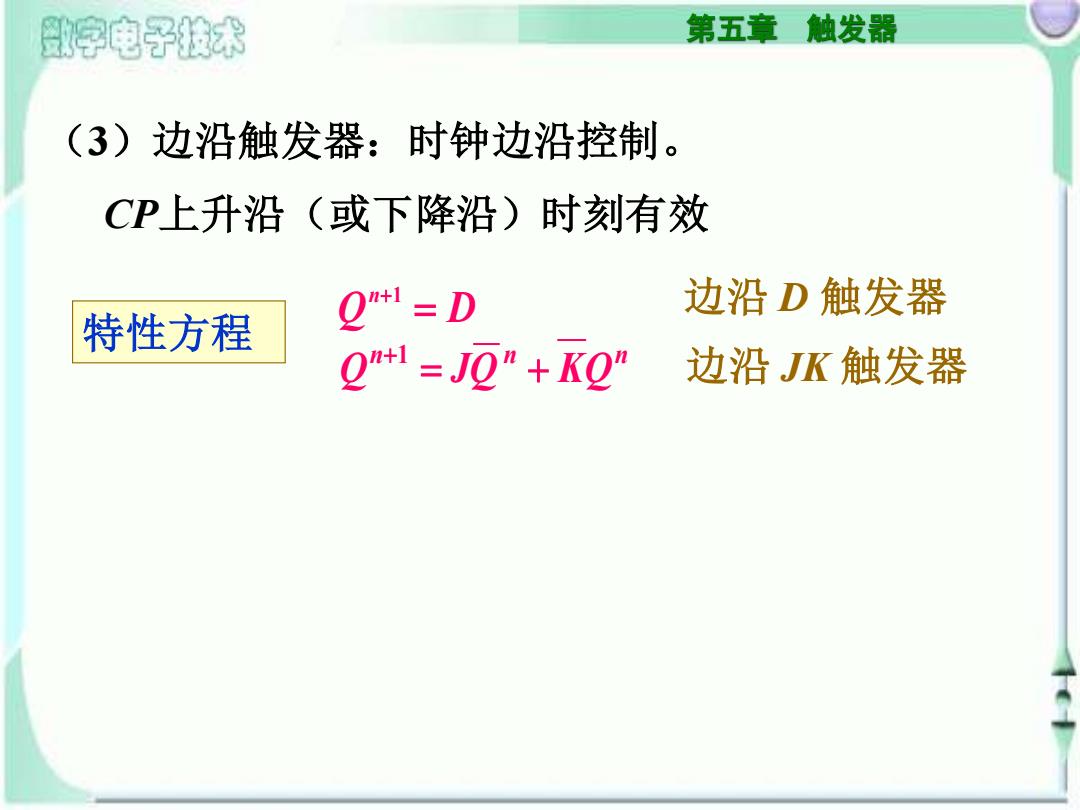

第五章 触发器 (3)边沿触发器:时钟边沿控制。 CP上升沿(或下降沿)时刻有效 特性方程 边沿 D 触发器 n n n Q = JQ + KQ +1 边沿 JK 触发器 Q D n = +1

数字电子技术 第五章 2.根据逻辑功能不同,时钟触发器可分为 (1)RS触发器 Q'=S+RQ” RS=0(约束条件) (2)JK触发器 0"+1=Jg"+KQ” (3)D触发器 Q"+'=D (4)T触发器 0+1=Tg"+Tg1 (5)T’触发器 Q+1=0

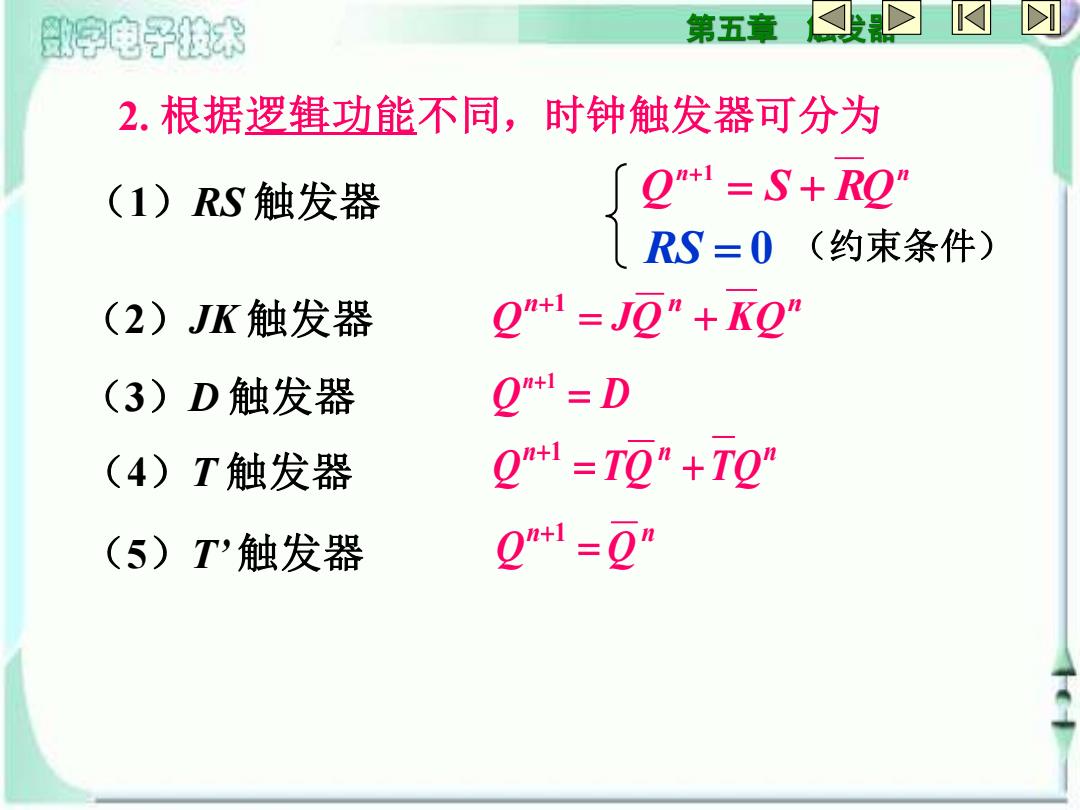

第五章 触发器 2. 根据逻辑功能不同,时钟触发器可分为 (1)RS 触发器 RS = 0 n n Q = S + RQ +1 (约束条件) n n n Q = JQ + KQ +1 (3)D 触发器 Q D n = +1 (4)T 触发器 n n n Q = TQ +TQ +1 (5)T’ 触发器 n n Q = Q +1 (2)JK 触发器

数字电子技术 第五章 [练习]在图中所示的CC4013边沿D触发器中, CP、D、SD、RD的波形见图,试画出O、Q的波形。 [解】SD、R,一异步置位(置1)、复位(置0)端 CP一上升沿触发。 CP D Sp S 1D R Rp Sp D CP Rp

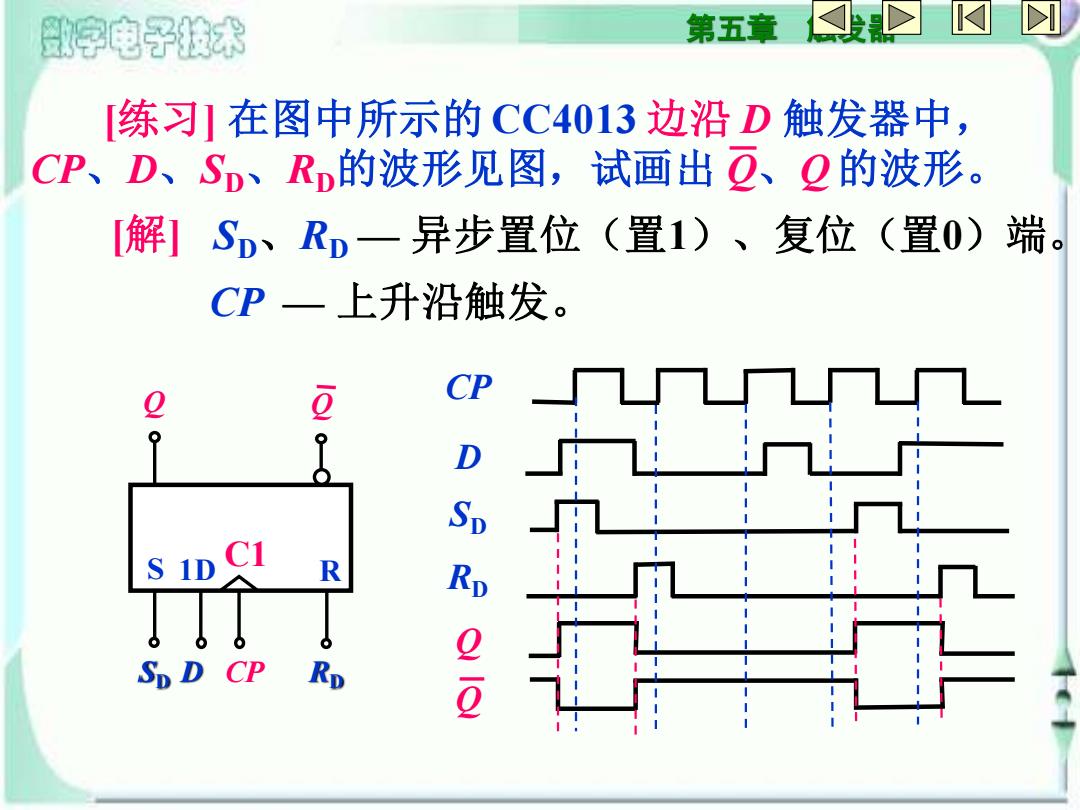

第五章 触发器 [练习] 在图中所示的 CC4013 边沿 D 触发器中, CP、D、SD、RD的波形见图,试画出 Q、Q 的波形。 [解] Q Q CP C1 1D D S SD R RD SD、RD — 异步置位(置1)、复位(置0)端。 CP — 上升沿触发。 CP D SD RD Q Q