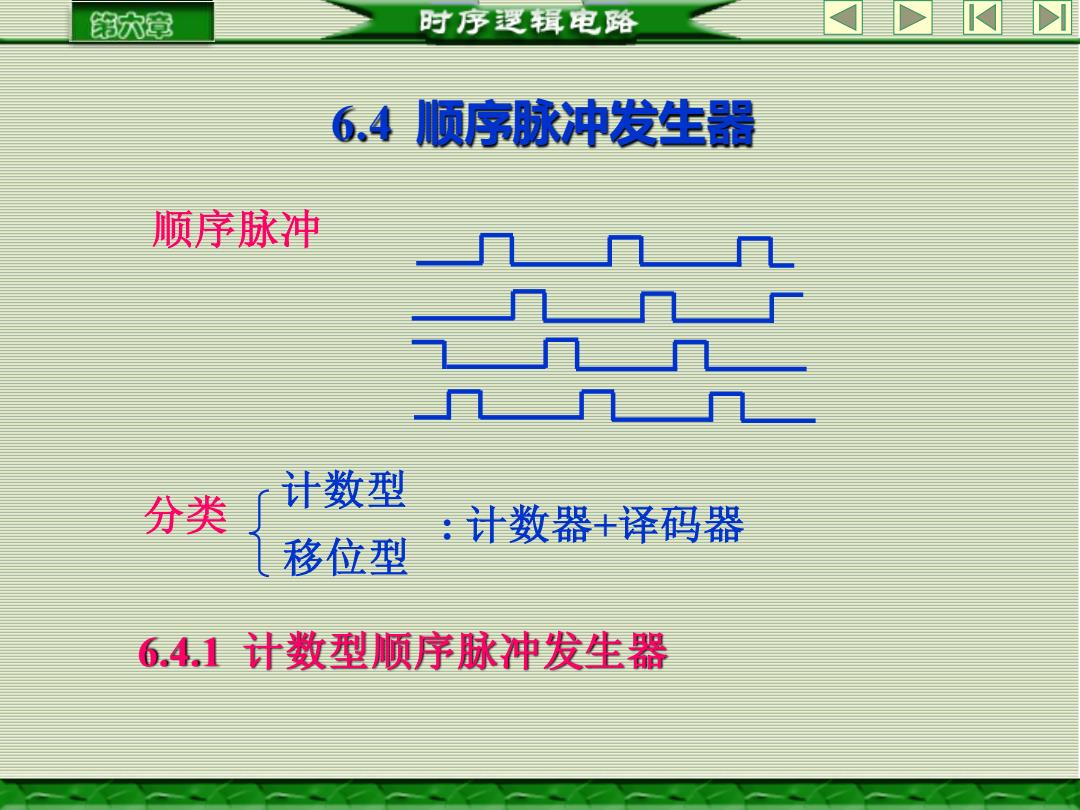

第六草 时序逻辑电路 6.4顺序脉冲发生器 顺序脉冲 分类 计数型 :计数器+译码器 移位型 6.4.1计数型顺序脉冲发生器

6.4 顺序脉冲发生器 6.4.1 计数型顺序脉冲发生器 顺序脉冲 分类 计数型 移位型 : 计数器+译码器

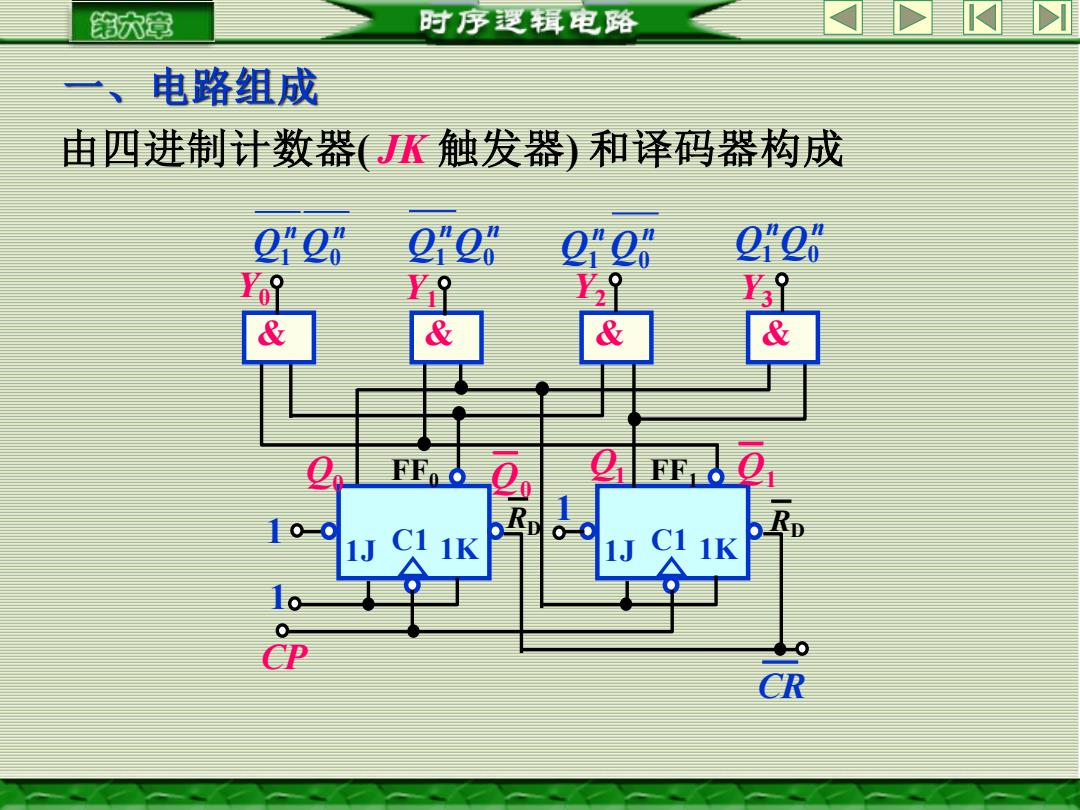

第六章 时序题辑电路 一、电路组成 由四进制计数器(K触发器)和译码器构成 Q06 0"06 226 Y & & & & 0. 1J C1 1K △ 0 CR

一、电路组成 由四进制计数器( JK 触发器) 和译码器构成 Y0 CP 1J C1 1K Q0 Q0 FF0 1J C1 1K Q1 FF1 Q1 & 1 R 1 D RD 1 CR & & & Y1 Y2 Y3 n n Q1 Q0 n n Q1 Q0 n n Q1 Q0 n n Q1 Q0

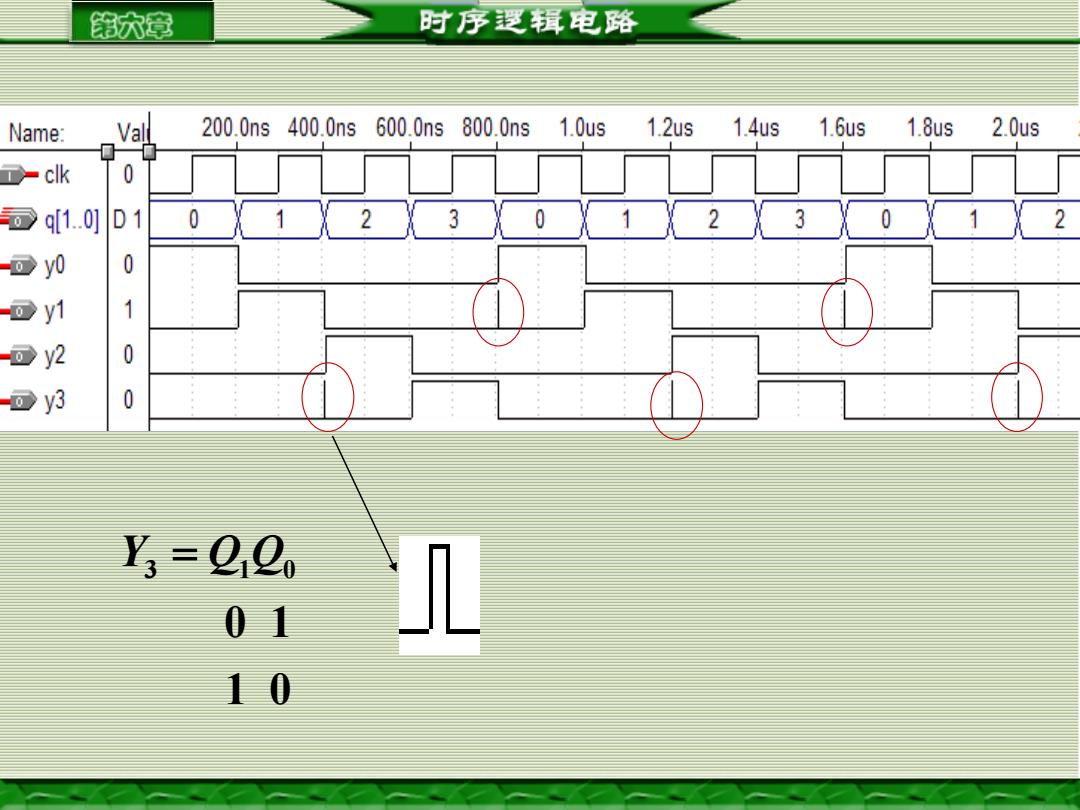

第六草 时序题辑电路 Name: Vall 200.0ns400.0ns600.0ns800.0ns 1.0us 1.2us 1.4us 1.6us 1.8us 2.0us 工-clk 0 g1.0]D1 0 1 2 3 0 1 2 3 0 1 2 可y0 0 -@y1 1 -y2 0 y3 0 Y3=2C0 01 0

3 1 0 0 1 1 0 Y Q Q =

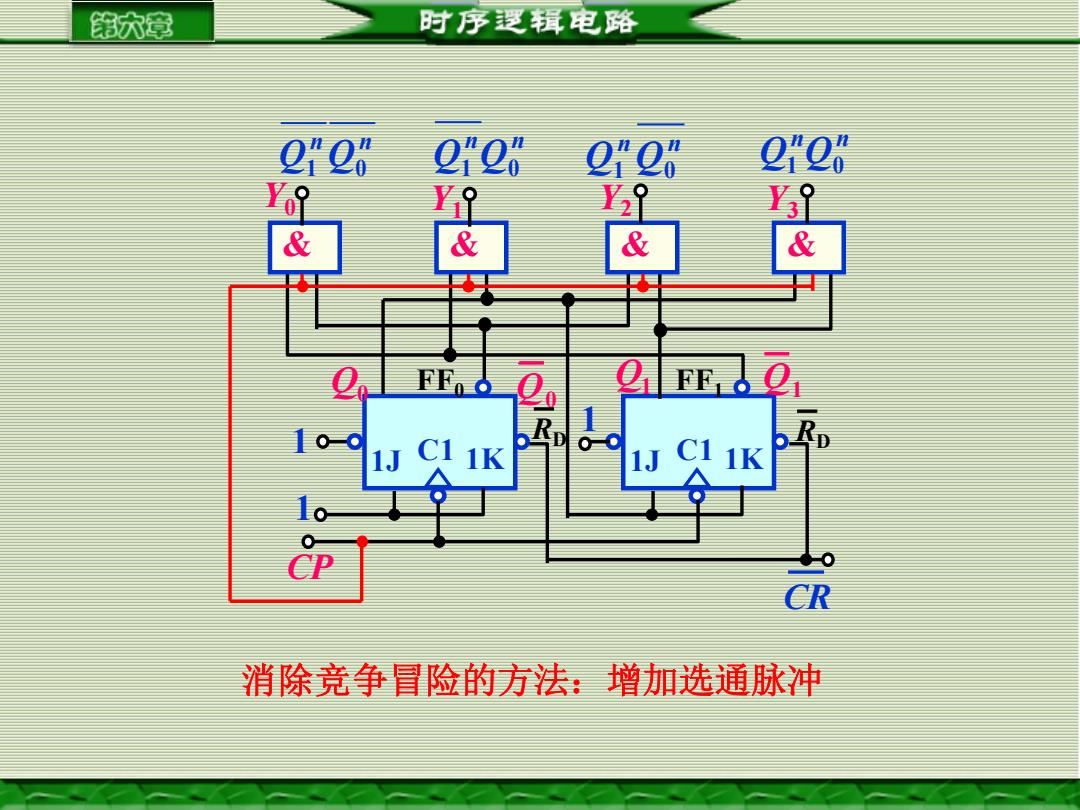

第六草 时序遐辑电路 Q'0 Q26 Q26 & & & 00 1J C1 1K 1J C1 1K p CR 消除竞争冒险的方法:增加选通脉冲

Y0 CP 1J C1 1K Q0 Q0 FF0 1J C1 1K Q1 FF1 Q1 & 1 R 1 D RD 1 CR & & & Y1 Y2 Y3 n n Q1 Q0 n n Q1 Q0 n n Q1 Q0 n n Q1 Q0 消除竞争冒险的方法:增加选通脉冲

第六草 时序题辑电路 Name: Vall 200,0ns400.0ns600,0ns800.0ns1.0us 1.2us 1.4us 1.6us 1.8us 2.0us clk 0 司q10D1 0 1 2 3 0 1 2 3 0 1 2 -y0 0 @y1 1 -@y2 0 I @y3 0

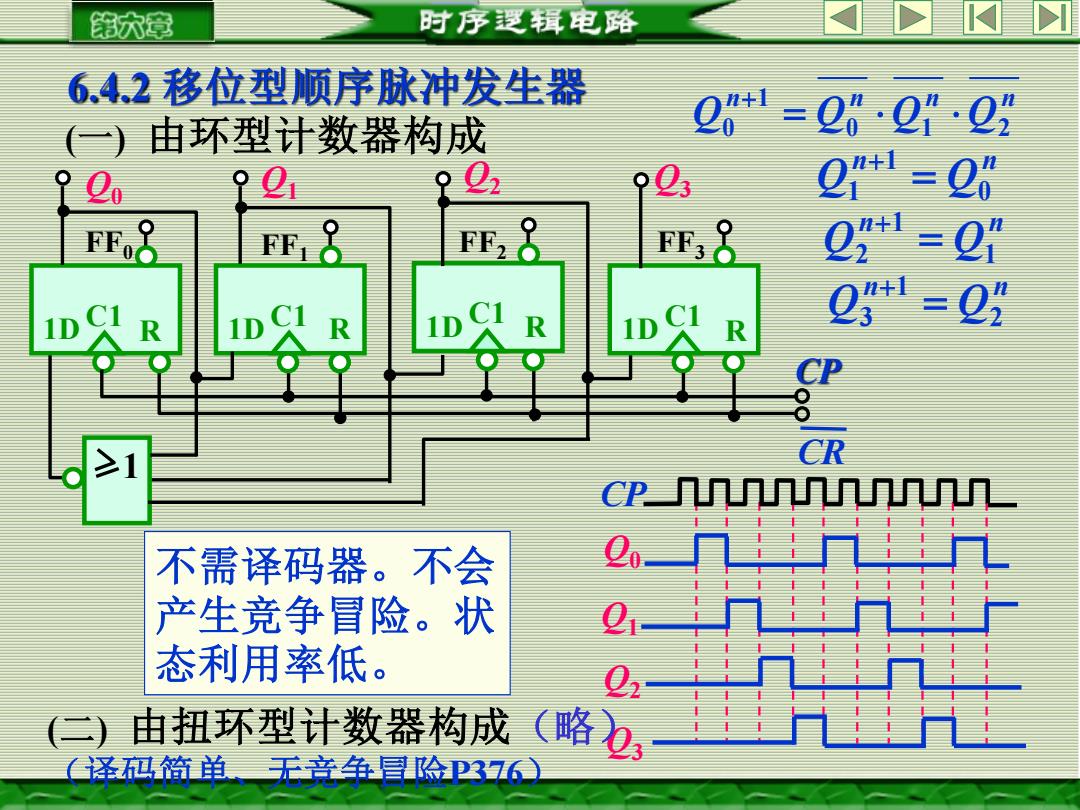

第六章 时序逻辑电路 6.4.2移位型顺序脉冲发生器 ()由环型计数器构成 0=Q60”.05 00 1 9 902 o0 Q"1=Q6 FFo8 1D R 1D 1D R CP ≥1 CR CP. 不需译码器。不会 0, 产生竞争冒险。状 态利用率低。 0 (二由扭环型计数器构成 (略0, (译码简单、无竞争冒险P376

6.4.2 移位型顺序脉冲发生器 n n n n Q Q0 Q1 Q2 1 0 = + n n Q Q0 1 1 = + n n Q Q1 1 2 = + n n Q Q2 1 3 = + C1 1D Q0 C1 1D Q1 C1 1D Q2 C1 1D Q3 FF0 FF1 FF2 FF3 CP CR R R R R 1 不需译码器。不会 产生竞争冒险。状 态利用率低。 (一) 由环型计数器构成 CP Q0 Q1 Q2 Q3 (二) 由扭环型计数器构成(略) (译码简单、无竞争冒险P376)

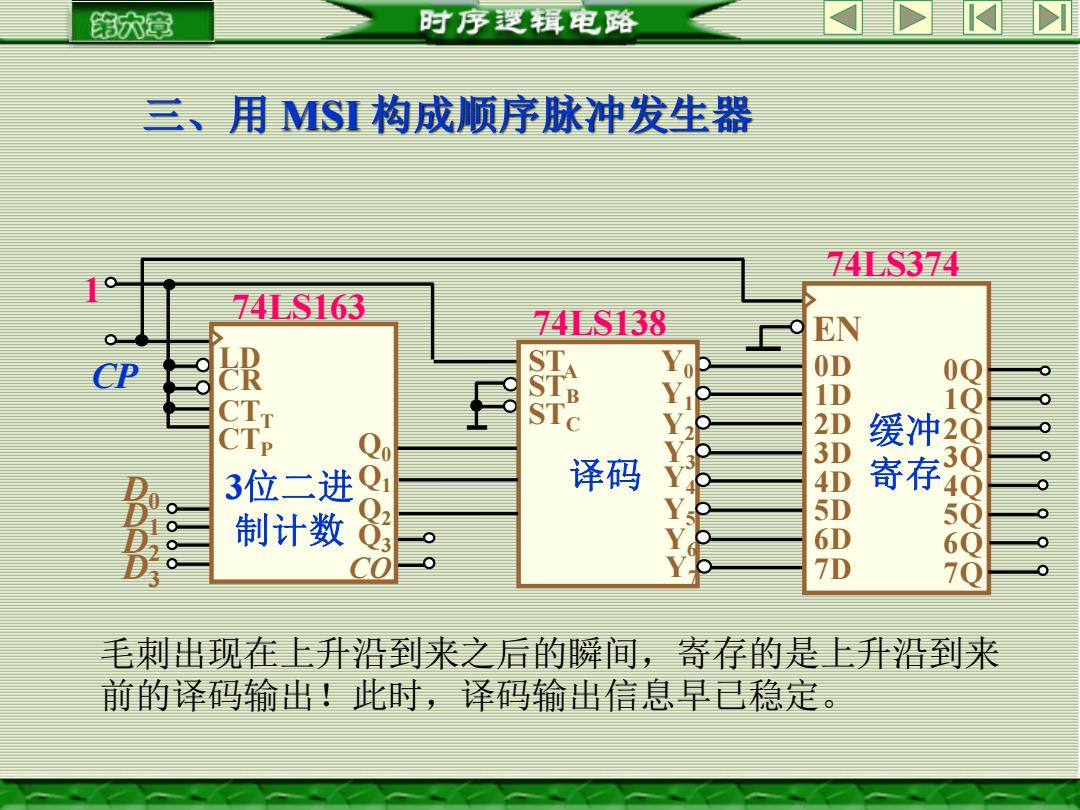

第六章 时序遐辑电路 三、用MSI构成顺序脉冲发生器 74S374 74S163 74S138 EN CP 3位二 制计数 Q0 译码 010000100 00900000 舞 0 毛刺出现在上升沿到来之后的瞬间,寄存的是上升沿到来 前的译码输出此时,译码输出信息早已稳定

三、用 MSI 构成顺序脉冲发生器 D0 D1 D2 D3 LD CR CTT CTP Q0 Q1 Q2 Q3 CO 74LS163 74LS138 STA STB STC Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 0D 1D 2D 3D 4D 5D 6D 7D CP 1 74LS374 EN 0Q 1Q 2Q 3Q 4Q 5Q 6Q 7Q 3位二进 制计数 译码 缓冲 寄存 毛刺出现在上升沿到来之后的瞬间,寄存的是上升沿到来 前的译码输出!此时,译码输出信息早已稳定

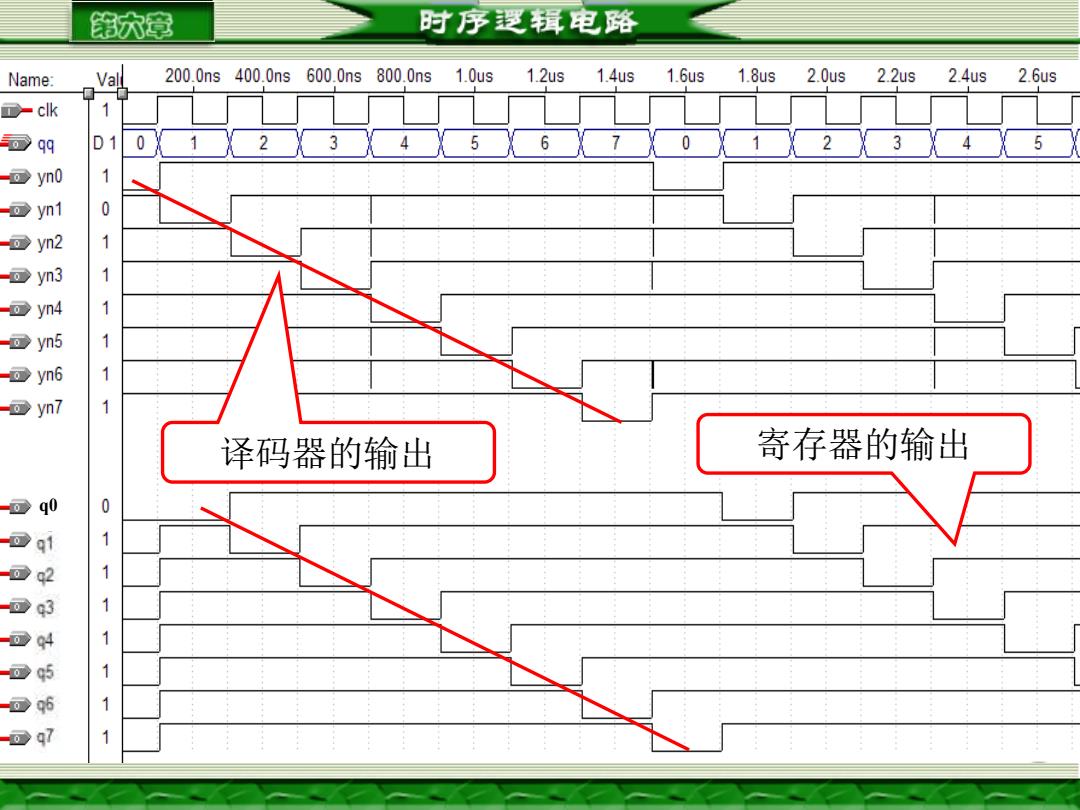

第六章 时序遐辑电路 Name: Val 200.0ns400.0ns600.0ns800.0ns1.0us 1.2us 1.4us 1.6us 1.8us 2.0us 2.2us 2.4us 2.6us clk 1 qq D1 0 1 2 3 4 5 6 7 0 1 2 3 4 5 yn0 0 1 译码器的输出 寄存器的输出 q0 0 1 1 1 q7 1

译码器的输出 寄存器的输出 q0

第六草 时序逻辑电路 ·从仿真波形可知: 增加了寄存器可以滤除尖峰脉冲,得到 的将是带后一个时钟周期的“干净”的 顺序脉冲

• 从仿真波形可知: 增加了寄存器可以滤除尖峰脉冲,得到 的将是滞后一个时钟周期的“干净”的 顺序脉冲