第六障 时序逻辑电路 6.2计数器(Counter) 6.2.计数器的特点和分类 一、数字电路中的计数器 1.定义 在数字电路中,把记忆输入CP脉冲个数的操作叫 做计数,能实现计数操作的电子电路称为计数器。 2.特点 A.主要组成单元是时钟触发器。 B.一般为Moore型时序电路,计数脉冲CP为 触发器时钟信号

6.2.1 计数器的特点和分类 一、数字电路中的计数器 1.定义 在数字电路中,把记忆输入CP脉冲个数的操作叫 做计数,能实现计数操作的电子电路称为计数器。 2.特点 A. 主要组成单元是时钟触发器。 B. 一般为Moore 型时序电路,计数脉冲CP为 触发器时钟信号

第六障 时序逻辑电路 三、计数器的分类 按数制分: 二进制计数器 十进制计数器 N进制(任意进制)计数器 按计数 加法计数器 方式分: 减法计数器 可逆计数(Up-Down Counter) 按时钟 同步计数器 (Synchronous ~ 控制分: 异步计数器(Asynchronous~) 按开关 TTL计数器 元件分: CMOS计数器

三、 计数器的分类 按数制分: 二进制计数器 十进制计数器 N 进制(任意进制)计数器 按计数 方式分: 加法计数器 减法计数器 可逆计数 (Up-Down Counter) 按时钟 控制分: 同步计数器 (Synchronous ) 异步计数器 (Asynchronous ) 按开关 元件分: TTL 计数器 CMOS 计数器

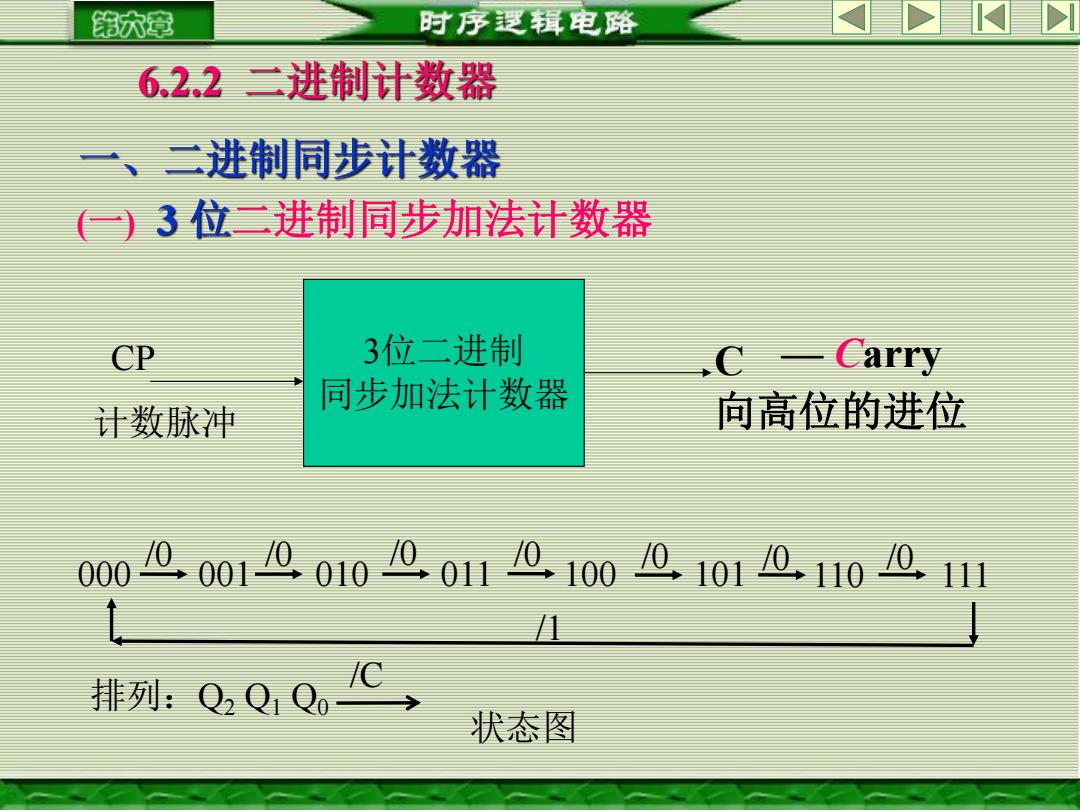

第六章 时序逻辑电路 6.2.2 二进制计数器 一、二进制同步计数器 (一)3位二进制同步加法计数器 CP 3位二进制 .C - Carry 同步加法计数器 计数脉冲 向高位的进位 0000. 0010010001101000. 10101100111 /1 排列:Q2Q1Q0C 状态图

(一) 二进制同步加法计数器 C — Carry 向高位的进位 3位二进制 同步加法计数器 CP 计数脉冲 000 001 010 011 100 101 110 111 /0 /0 /0 /0 /0 /0 /0 /1 排列:Q2 Q1 Q0 状态图 /C

第六障 时序遐辑电路 0000,00100100010100010101100 111 排列:Q2Q1Q, 设计方法一:按前述设计步骤进行 (P258.259) 得结果如下: Jo=Ko=1 J2-K2=0"100 C=0n00 J=K1=O"0 & 里a 0小0 J C1 C1 1K 1K 1K CP

设计方法一: 按前述设计步骤进行 (P258 259) 得结果如下: 000 001 010 011 100 101 110 111 /0 /0 /0 /0 /0 /0 /0 /1 排列:Q2 Q1 Q0 CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF2 & & C Q0 Q1 Q2 Q0 Q1 Q2 J0= K0 =1 J1= K1 = Qn 0 J2= K2 = Qn 1Qn 0 C = Q2 n Q1 n Q0 n

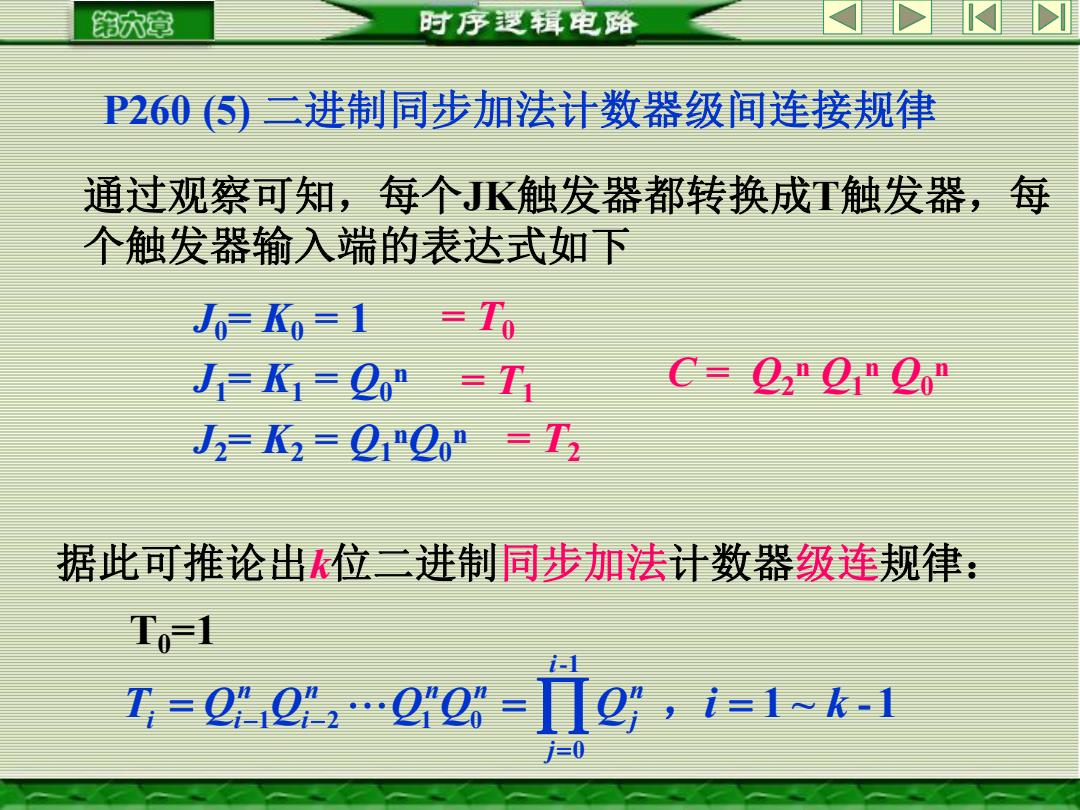

第六障 时序逻辑电路 P260⑤二进制同步加法计数器级间连接规律 通过观察可知,每个JK触发器都转换成T触发器,每 个触发器输入端的表达式如下 J0K0=1=T0 JI=K1=C0 =T C-0n000 J2=K2=000"=T, 据此可推论出k位二进制同步加法计数器级连规律: T0= T,=Q%2%…QQ=∏2,i-1~k-1 j=0

C = Q2 n Q1 n Q0 n 通过观察可知,每个JK触发器都转换成T触发器,每 个触发器输入端的表达式如下 J0= K0 = 1 J1= K1 = Q0 n J2= K2 = Q1 nQ0 n = T0 = T1 = T2 据此可推论出k位二进制同步加法计数器级连规律: -1 1 2 1 0 0 1 ~ -1 i n n n n n i i i j j T Q Q Q Q Q i k , P260 (5) 二进制同步加法计数器级间连接规律 T0=1

第六障 时序遐辑电路 (7)计数器计数长度、进制或模的概念:P300下部 指计数器能够记忆输入脉冲的数目,即电路的有 效状态数M 3位二进制同步加法计数器: 000 M=23=8 4位二进制同步加法计数器: M=24=16 0000 n位二进制同步加法计数器: M=2

(7)计数器计数长度、进制或模的概念:P300下部 指计数器能够记忆输入脉冲的数目,即电路的有 效状态数 。 3 位二进制同步加法计数器: 2 8 3 M 0000 1111 /1 4 位二进制同步加法计数器: 000 111 /1 2 16 4 M n 位二进制同步加法计数器: n M 2

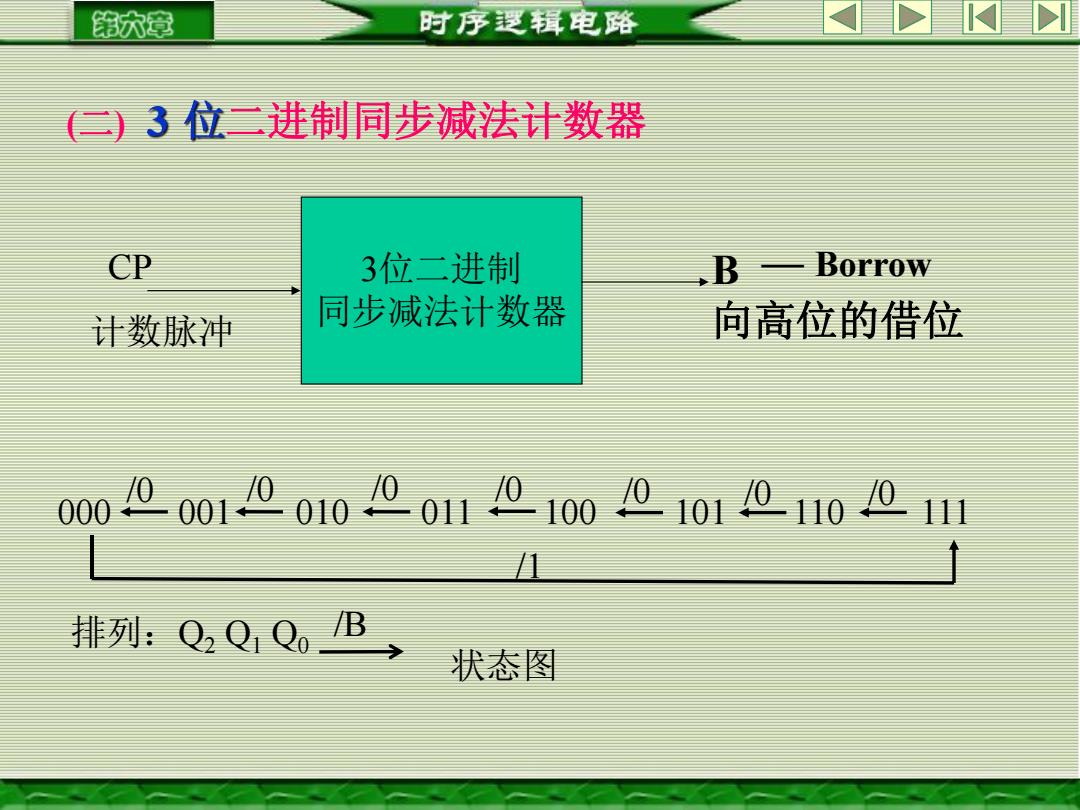

第六障 时序遐辑电路 (→3位二进制同步减法计数器 CP 3位二进制 B一 Borrow 计数脉冲 同步减法计数器 向高位的借位 00000010010000100001010年 排列:Q,Q1QB 状态图

B — Borrow 向高位的借位 3位二进制 同步减法计数器 CP 计数脉冲 (二) 二进制同步减法计数器 000 001 010 011 100 101 110 111 /0 /0 /0 /0 /0 /0 /0 /1 排列:Q2 Q1 Q0 状态图 /B

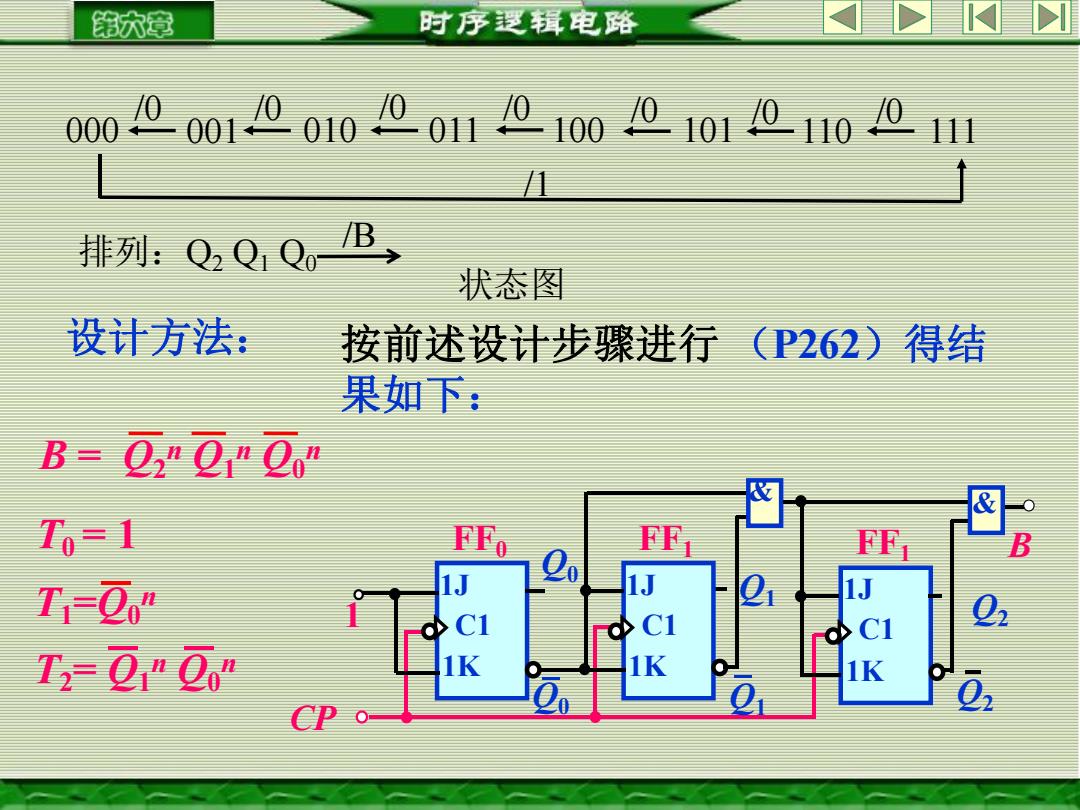

第六障 时序题辑电路 0000001001000010001010001 排列.Q2Q1Q B 状态图 设计方法 按前述设计步骤进行(P262)得结 果如下: B=0"0"0'" & ● T6=1 FFo B 0 T0" 1J 1J C1 C1 C1 02 T-00 1K 1K 1K 0

设计方法: 按前述设计步骤进行 (P262)得结 果如下: 000 001 010 011 100 101 110 111 /0 /0 /0 /0 /0 /0 /0 /1 排列:Q2 Q1 Q0 状态图 /B B = Q2n Q1n Q0n T0 = 1 T1=Q0n T2= Q1n Q0n CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF1 & & B Q0 Q1 Q2 Q0 Q1 Q2

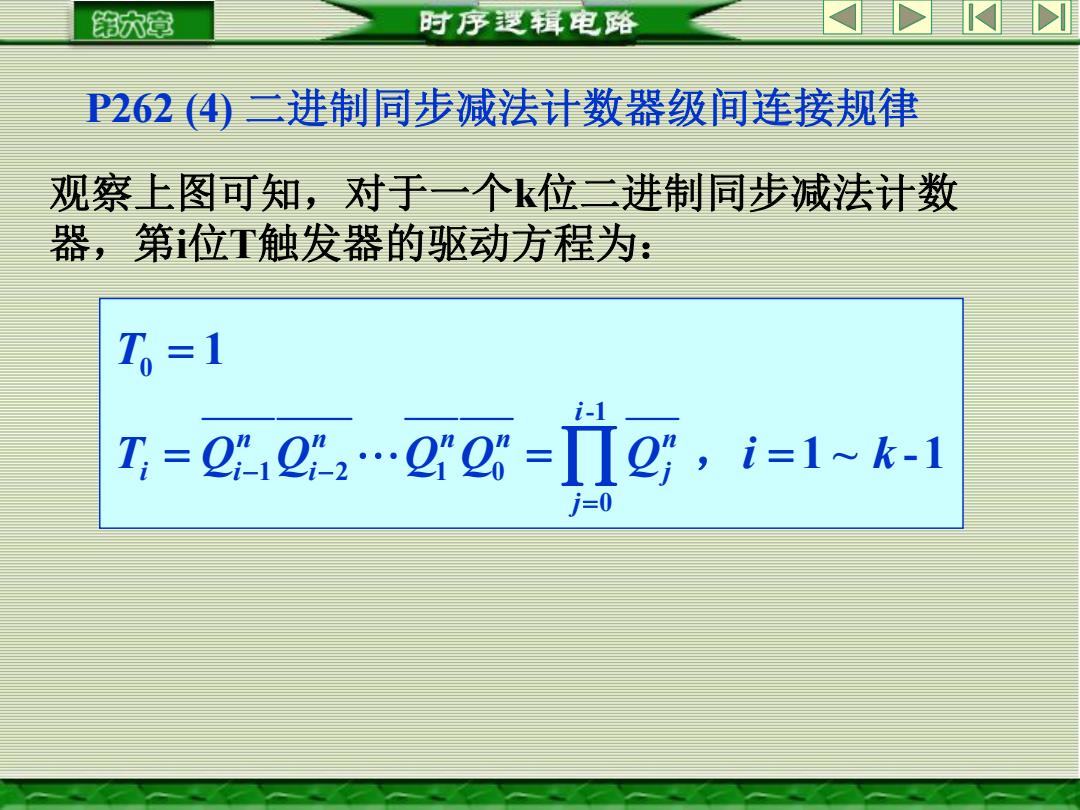

第六障 时序逻辑电路 P262④二进制同步减法计数器级间连接规律 观察上图可知,对于一个k位二进制同步减法计数 器,第位T触发器的驱动方程为: T,=1 i-1 T=2”122…22=Π25,i=1~k-1 j=0

观察上图可知,对于一个k位二进制同步减法计数 器,第i位T触发器的驱动方程为: P262 (4) 二进制同步减法计数器级间连接规律 0 -1 1 2 1 0 0 1 1 ~ -1 i n n n n n i i i j j T T Q Q Q Q Q i k ,

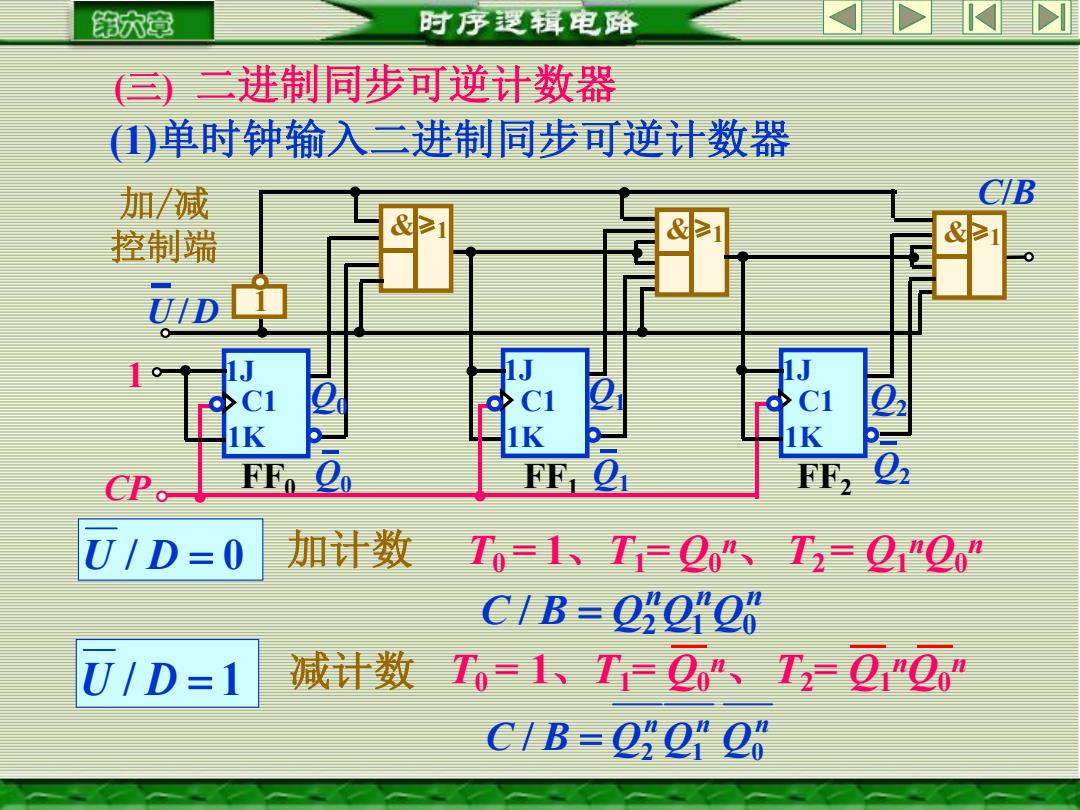

第六障 时序逻辑电路 (三二进制同步可逆计数器 )单时钟输入二进制同步可逆计数器 加/减 CIB 控制端 &1 & & UID 1J 1J C1 1K 1K 1K CP。 FFo_ FF U/D=0 加计数 T0=1、T=00"、T2-0'0/ C/B=Q5Q'06 U/D=1 减计数T0=1、T-O"、T2-Q"Qo" C/B=2026

(三) 二进制同步可逆计数器 (1)单时钟输入二进制同步可逆计数器 加/减 控制端 U / D 0 加计数 T0 = 1、T1= Q0n 、 T2= Q1nQ0n / 2 1 0 n n n C B Q Q Q U / D 1 减计数 T0 = 1、T1= Q0n 、 T2= Q1nQ0n n n n C B Q2 Q1 Q0 / CP Q0 1J 1K C1 FF0 1 Q0 Q2 1J 1K C1 FF2 Q2 Q1 1J 1K C1 FF1 Q1 U / D 1 & 1 & 1 & 1 C/B