第六章 时序遐辑电路 6.3寄存器和读/写存储器 (Register and Random Access Memory) 6.31寄存器的主要特点和分类 、 概念和特点 )概念 寄存:把二进制数据或代码暂时存储起来的操作。 寄存器:具有寄存功能的电路 并行输出 (二)特点 串行 串行 组成:主要由同一类 输入 FFo FF1…FFm-1 输出 型的触发器(基本 同步边沿)构成。 控制信号 Do D 功能:只暂时存储一般不处理。 并行输入

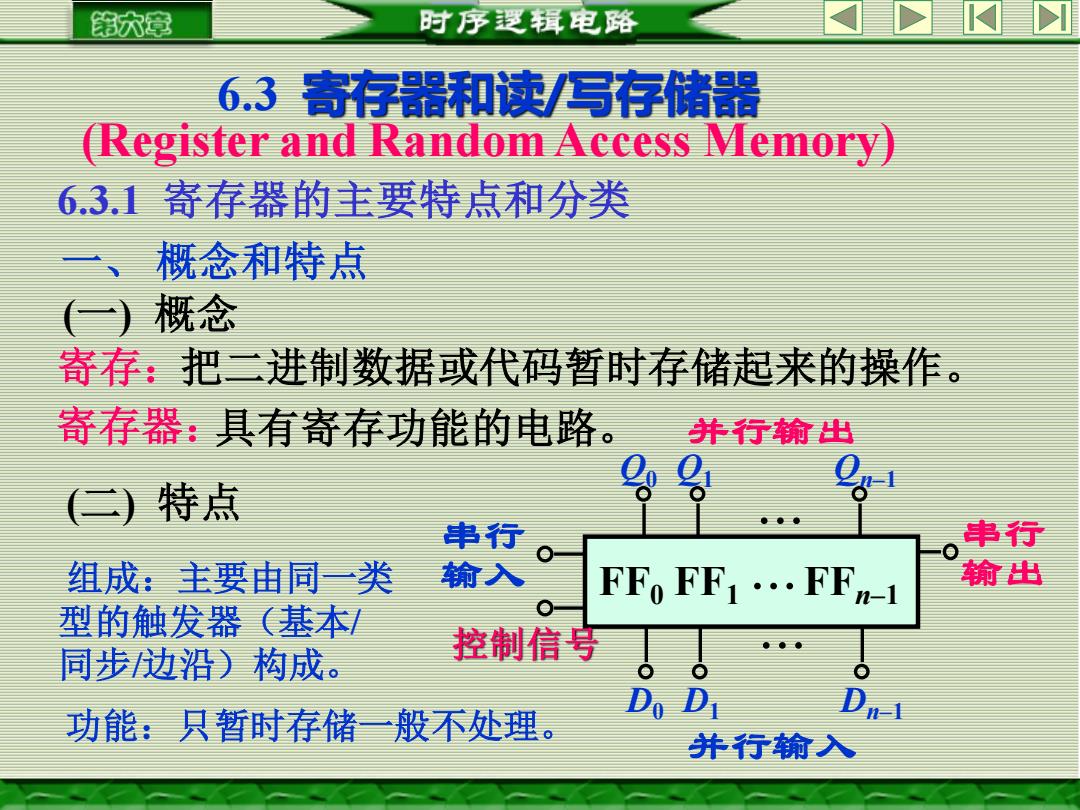

6.3 寄存器和读/写存储器 (Register and Random Access Memory) 6.3.1 寄存器的主要特点和分类 一、 概念和特点 (一) 概念 寄存:把二进制数据或代码暂时存储起来的操作。 寄存器:具有寄存功能的电路。 (二) 特点 组成:主要由同一类 型的触发器(基本/ 同步/边沿)构成。 并行输入 并行输出 FF0 FF1 FFn–1 D0 D1 Dn–1 Q0 Q1 Qn–1 控制信号 串行 输入 串行 输出 功能:只暂时存储一般不处理

第六章 时序逻辑电路 二、分类 基本寄存器 (只能并入并出;基本、 (一)按功能分 同步、边沿触发器) 移位寄存器 (并入并出、并入串出、 串入并出、串入串出; 只能边沿触发器, 二)按开关元件分 TTL寄存器 CMOS寄存器

二、 分类 (一) 按功能分 基本寄存器 移位寄存器 (只能并入并出;基本、 同步、边沿触发器) (并入并出、并入串出、 串入并出、串入串出; 只能边沿触发器) (二) 按开关元件分 TTL 寄存器 CMOS 寄存器

第六章 时序题辑电路 表6.3.1 TTL寄存器的分类 数码寄存器 基本寄存器 移位寄存器 只能并入并出 多位D型 触发器 锁存器 寄存器阵列 单向移位 双向移位 寄存器 寄存器 74175 74LS375 74170 74195 74LS175 74194 74278 74LS170 74LS195 74LS194 哈装 74173 74116 74LS670 74LS173 74LS395 7495 74LS373 74172 74174 74164 74LS95 74LS174 D锁移装 74165 74198 74177 74166 74LS374 领瓷 74199

只能并入并出

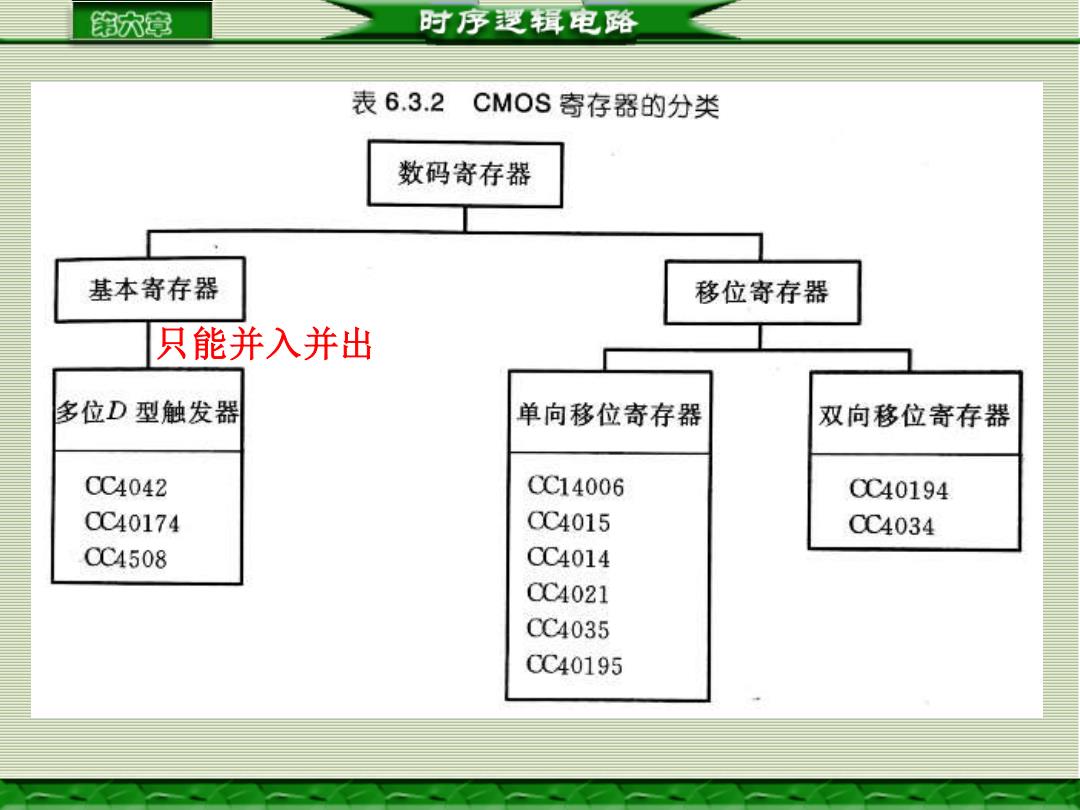

第六障 时序遐辑电路 表6.3.2CMOS寄存器的分类 数码寄存器 基本寄存器 移位寄存器 只能并入并出 多位D型触发器 单向移位寄存器 双向移位寄存器 CC4042 CC14006 C040194 CC40174 QC4015 CC4034 C℃4508 CC4014 CC4021 CC4035 CC40195

只能并入并出

第六章 时序逻辑电路 6.3.2 基本寄存器 一个触发器可以存储1位二进制信号;寄存位 二进制数码,需要1个触发器。 、4边沿D触发器(74175、74LS175 do d d d 01 C1 0202 0303 里8 D D, CR 特点 保持 并入并出,结构简单,各触发器存储信息相互独立

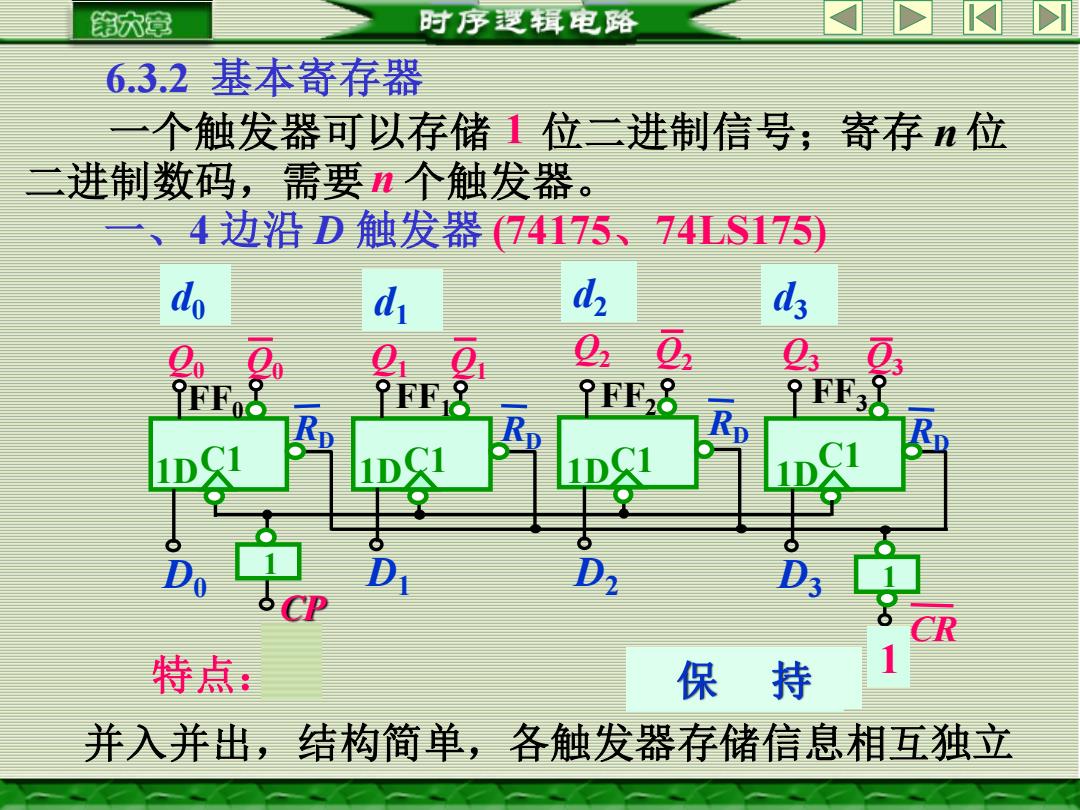

6.3.2 基本寄存器 一个触发器可以存储 位二进制信号;寄存 n 位 二进制数码,需要 个触发器。 1 n 一、4 边沿 D 触发器 (74175、74LS175) C1 1D D0 Q0 Q0 RD C1 1D D1 Q1 Q1 C1 1D D2 Q2 Q2 C1 1D D3 Q3 Q3 RD RD RD FF0 FF1 FF2 FF3 1 1 CP CR 异步清零 0 0 0 0 0 同步送数 1 d0 d1 d2 d3 特点: 保 持 并入并出,结构简单,各触发器存储信息相互独立

第六章 时序墅辑电路 二、双4位锁存器(门4116① Latch 一)引脚排列图和逻辑功能示意图 6c202D,202D22012D12002D.2LE2LL2CR 9.Q.Q,四数码并僧输出 24 23 2221 16 15 1413 送数 控制正Ro 之74116 CR 异步清零 9 10 1112 CR ILEAILER1D0 1001D11Q1D2 IO2 1Ds 10 二)逻辑功能 清零 CR=0 03020120=0000 送数 CR=1 LEA+LEB=0 00000=43ll1d0 保持 CR=1 LEA+LEB =1 Q0010不变

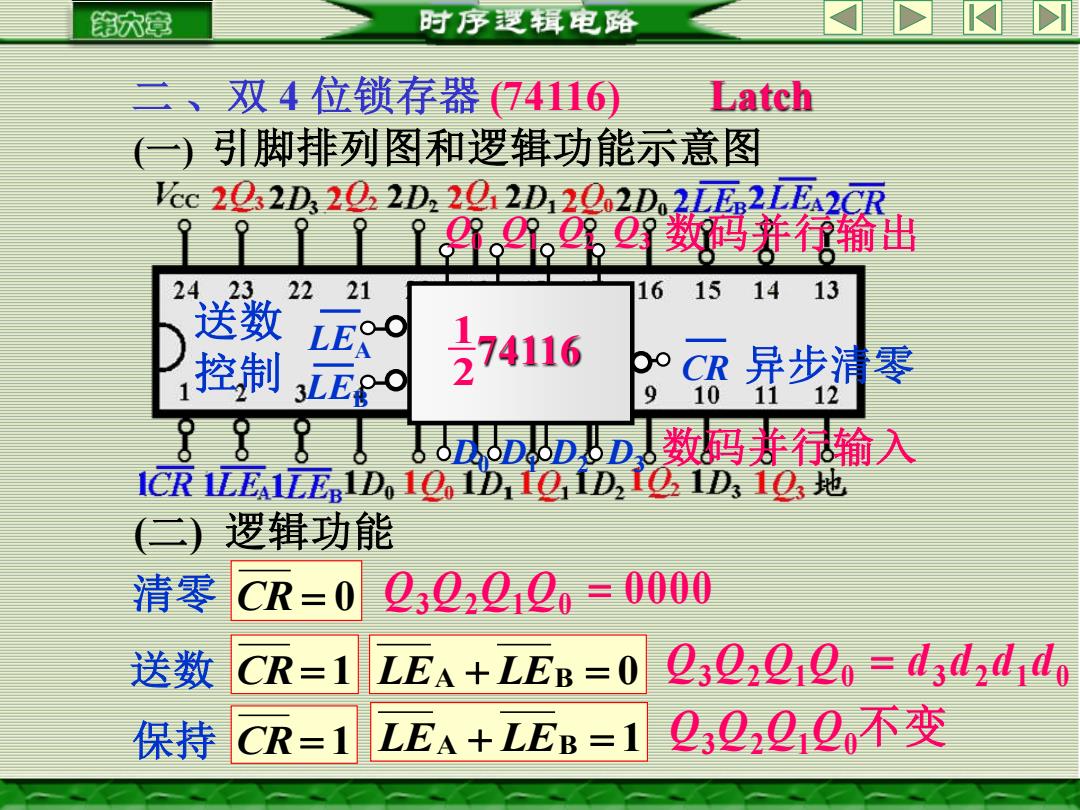

二 、双 4 位锁存器 (74116) Latch (一) 引脚排列图和逻辑功能示意图 74116 Q0 Q1 Q2 Q3 CR LEA D0 D1 D2 D3 LEB 2 1 异步清零 送数 控制 数码并行输入 数码并行输出 (二) 逻辑功能 清零 CR = 0 送数 0000 Q3 Q2 Q1 Q0 = CR= 1 LEA + LEB = 0 3 2 1 0 3 2 1 0 Q Q Q Q = d d d d 保持 CR= 1 LEA + LEB = 1 Q3 Q2 Q1 Q0 不 变

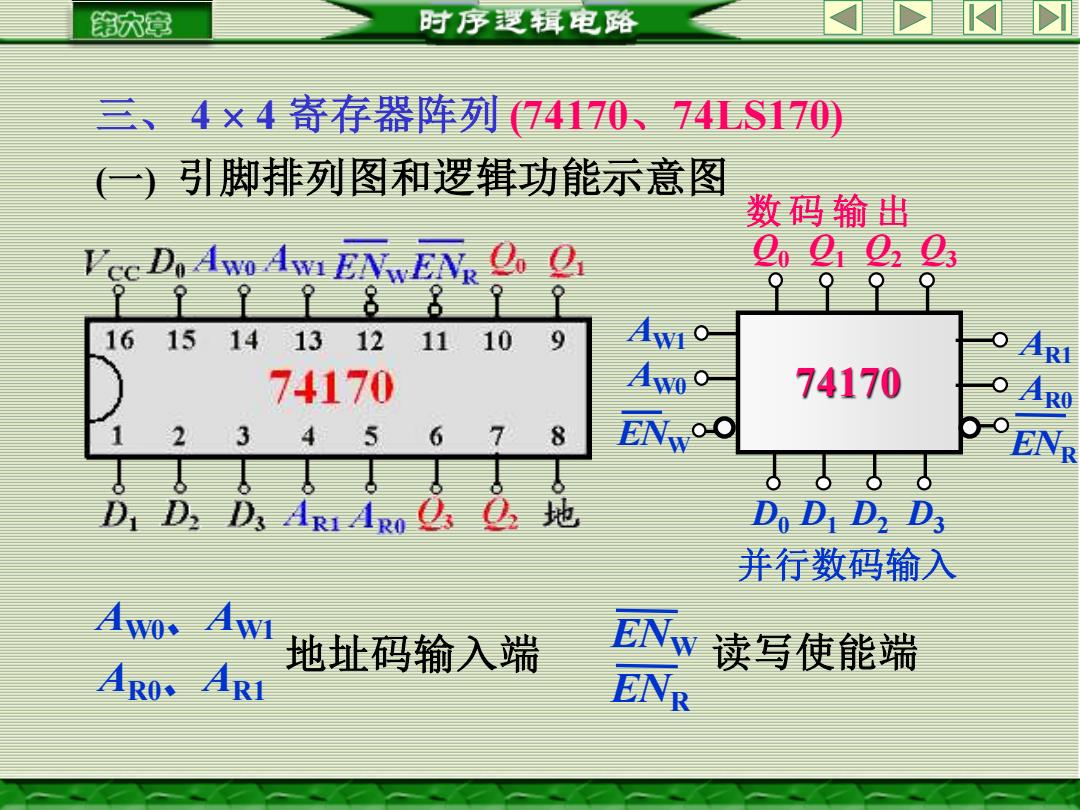

第六章 时序逻辑电路 三、4×4寄存器阵列(门470、74LS170) ()脚排列图和逻辑功能示意图 数码输山 06010210 16151413 121110 9 74170 74170 RO 23 45 6 78 ENR D1D,D3ARo凸2地 Do DI D2 D3 并行数码输入 Awo.Aw 地址码输入端 ENw 读写使能端 ARO.ARI ENR

三、 4 4 寄存器阵列 (74170、74LS170) (一) 引脚排列图和逻辑功能示意图 74170 Q0 Q1 Q2 Q3 ENR D0 D1 D2 D3 ENW AW0 AW1 AR0 AR1 并行数码输入 数 码 输 出 AW0、AW1 AR0、AR1 地址码输入端 ENW ENR 读写使能端

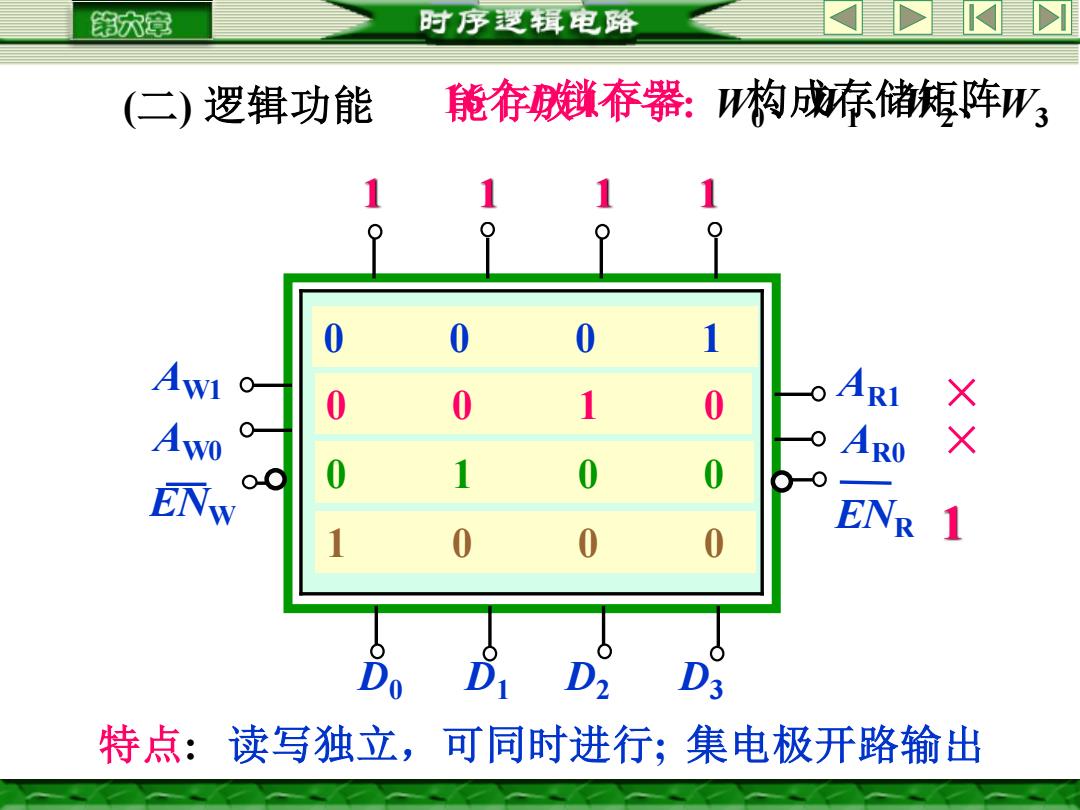

第六章 时序遐辑电路 (二)逻辑功能 能存熾存器:W构成东储想阵W3 0 0 1 Aw 0 0 1 0 ARI × Awo × 1 0 E不w ENR 1 0 0 0 Do 特点:读写独立,可同时进行;集电极开路输出

(二) 逻辑功能 16能存放个D锁存器 4个字: W构成存储矩阵 0、W1、W2、W3 Q0 Q1 Q2 Q3 ENR D0 D1 D2 D3 ENW AW0 AW1 AR0 AR1 FF00 FF01 FF02 FF03 FF10 FF11 FF12 FF13 FF20 FF21 FF22 FF23 FF30 FF31 FF32 FF33 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 0 0 0 1 0 1 0 0 1 0 0 0 1 0 0 1 1 0 0 0 1 0 0 0 1 × × 写 入 禁 止 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 0 0 1 1 0 0 0 1 × × 1 1 1 1 特点: 读写独立,可同时进行; 集电极开路输出

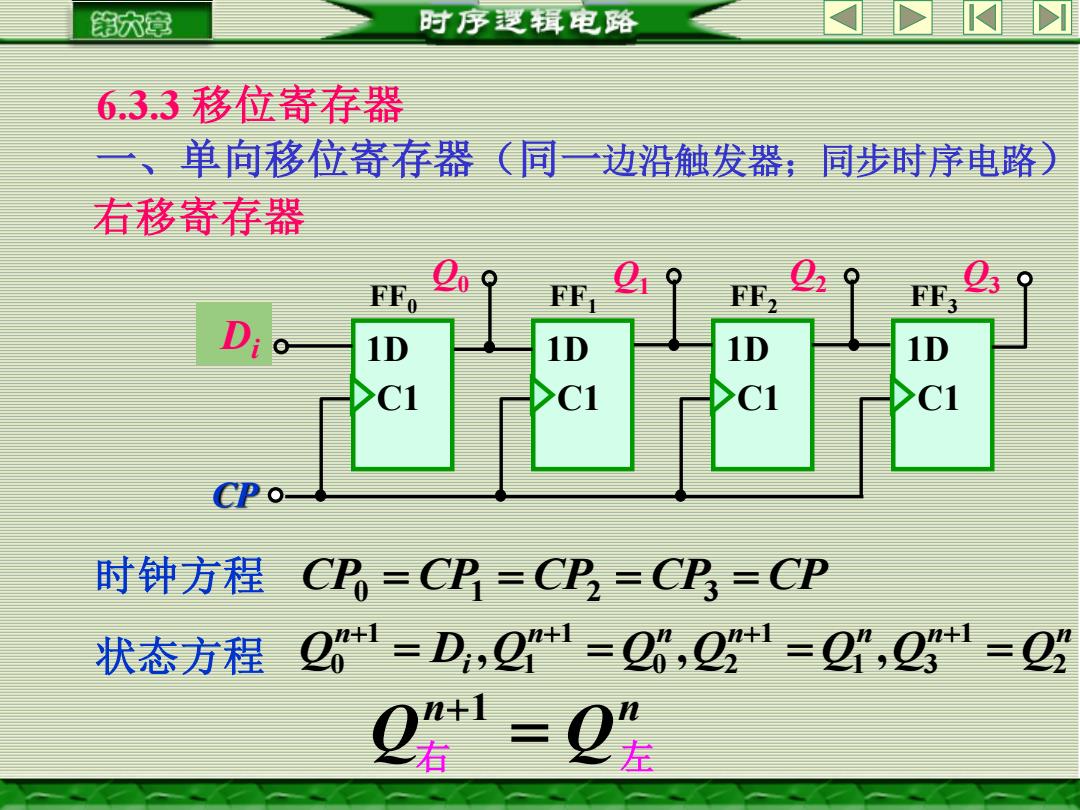

第六章 时序遐辑电路 633移位寄存器 、单向移位寄存器 (同一边沿触发器;同步时序电路) 右移寄存器 FFo 069 029 0 1D 1D C1 C1 C1 C1 时钟方程 CR=CP=CP=C卫3=CP 状态方程 Q1=D,Q1=Q6,Q1=Q,Q+1=Q 0

6.3.3 移位寄存器 一、单向移位寄存器(同一边沿触发器;同步时序电路) 右移寄存器 Q0 Q1 Q2 Q3 C1 1D FF0 CP C1 1D FF1 C1 1D FF2 C1 1D FF3 时钟方程 CP0 = CP1 = CP2 = CP3 = CP 状态方程 n n n n n n i n Q D Q Q Q Q Q Q2 1 1 3 1 0 2 1 1 1 0 = , = , = , = + + + + Di n n 1 Q Q + = 右 左

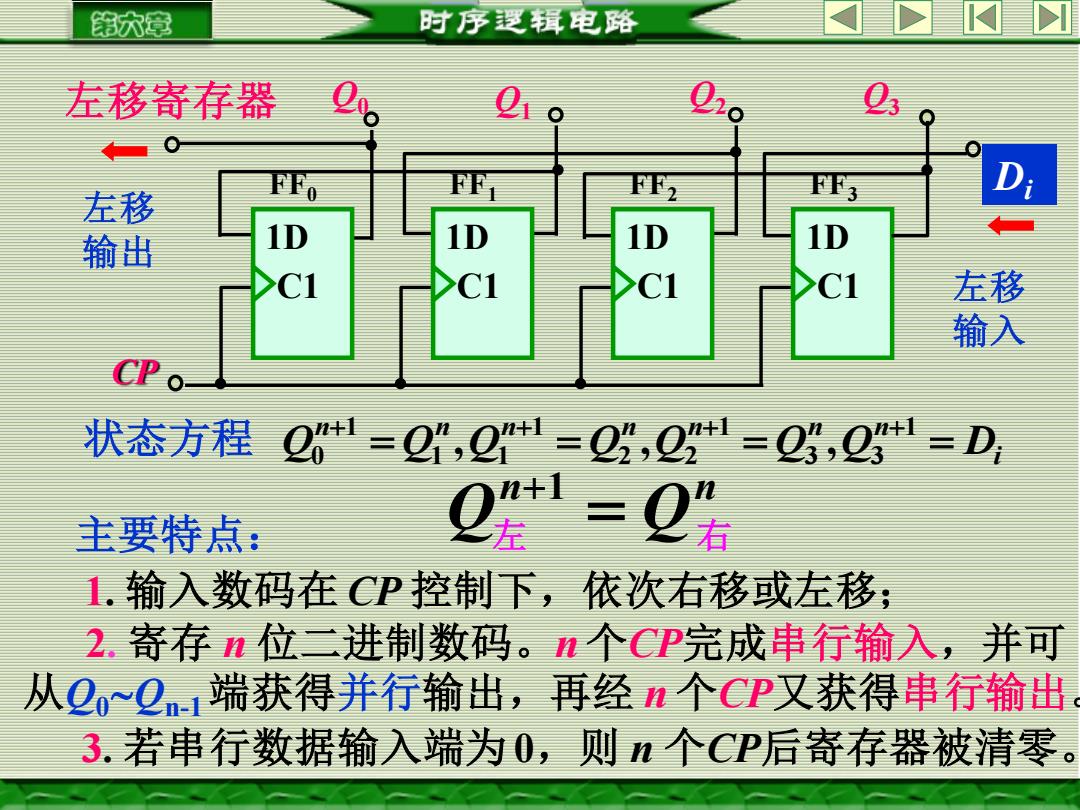

第六章 时序遐辑电路 左移寄存器 09 020 0 FFo 2 D 左移 输出 1D 1D 1D 1D C1 C1 C1 左移 输入 状态方程 Q6-Q,Q-Q,Q=Q%,Q-D 主要特点: 1.输入数码在CP控制下,依次右移或左移, 2寄存1位二进制数码。1个CP完成串行输入,并可 从Qo~Q1端获得并行输出,再经n个CP又获得串行输出 3.若串行数据输入端为0,则n个CP后寄存器被清零

左移寄存器 Di 左移 输入 左移 输出 状态方程 i n n n n n n n Q = Q Q = Q Q = Q Q = D + + + +1 3 3 1 2 2 1 1 1 1 0 , , , 主要特点: 1. 输入数码在 CP 控制下,依次右移或左移; 2. 寄存 n 位二进制数码。n 个CP完成串行输入,并可 从Q0Qn-1 端获得并行输出,再经 n 个CP又获得串行输出。 3. 若串行数据输入端为 0,则 n 个CP后寄存器被清零。 Q3 CP Q0 Q1 Q2 C1 1D FF0 C1 1D FF1 C1 1D FF2 C1 1D FF3 n n 1 Q Q + = 左 右