正在加载图片...

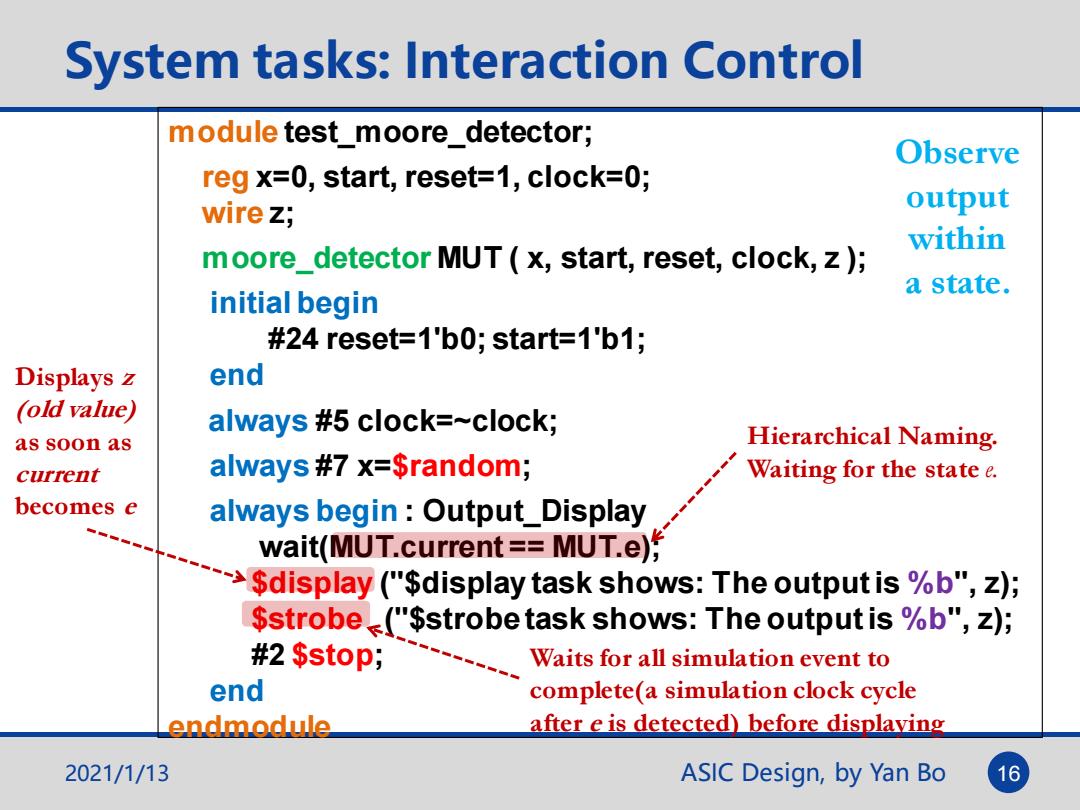

System tasks:Interaction Control module test moore_detector; Observe reg x=0,start,reset=1,clock=0; wire Z; output within moore_detector MUT (x,start,reset,clock,z ) a state. initial begin #24 reset=1'b0;start=1'b1; Displays z end (old value) always #5 clock=~clock; as soon as Hierarchical Naming. current always #7 x=Srandom; Waiting for the state e. becomes e always begin:Output_Display wait(MUT.current =MUT.e) $display ("$display task shows:The output is %b",z); $strobe ("$strobe task shows:The output is %b",z); #2 $stop; Waits for all simulation event to end complete(a simulation clock cycle endmodule after e is detected)before displaving 2021/1/13 ASIC Design,by Yan Bo 16ASIC Design, by Yan Bo 16 System tasks: Interaction Control module test_moore_detector; reg x=0, start, reset=1, clock=0; wire z; moore_detector MUT ( x, start, reset, clock, z ); initial begin #24 reset=1'b0; start=1'b1; end always #5 clock=~clock; always #7 x=$random; always begin : Output_Display wait(MUT.current == MUT.e); $display ("$display task shows: The output is %b", z); $strobe ("$strobe task shows: The output is %b", z); #2 $stop; end endmodule Hierarchical Naming. Waiting for the state e. Displays z (old value) as soon as current becomes e Waits for all simulation event to complete(a simulation clock cycle after e is detected) before displaying Observe output within a state. 2021/1/13