正在加载图片...

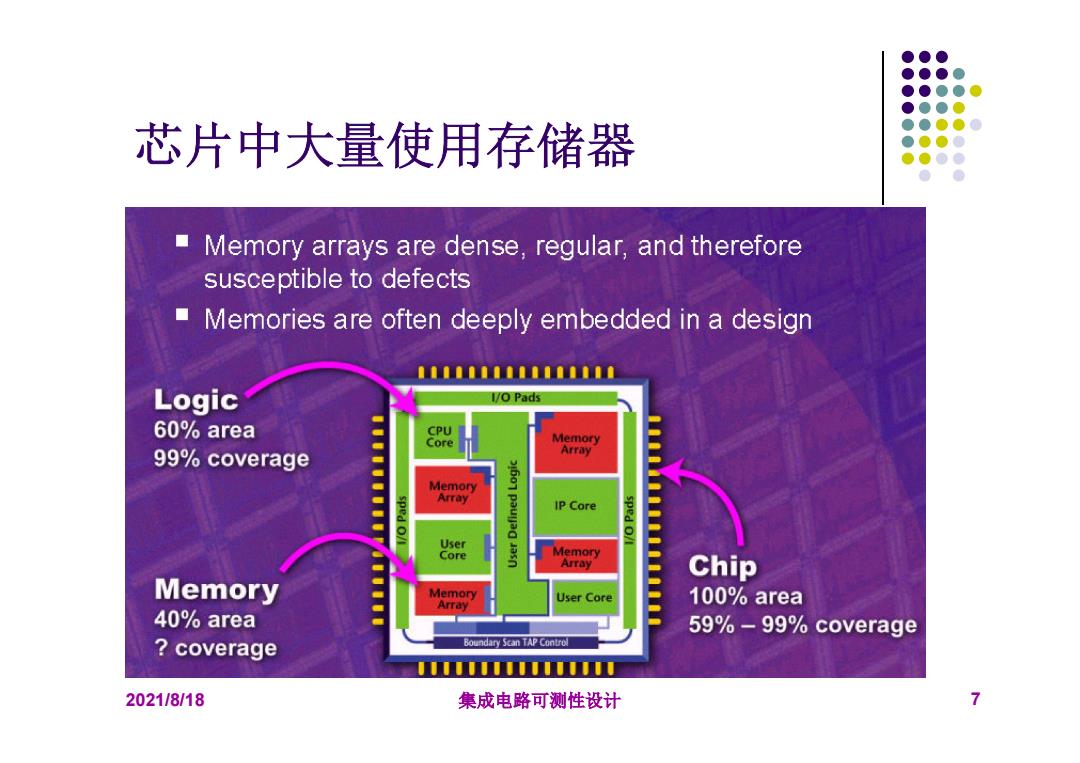

● ● 芯片中大量使用存储器 ●0 ●●●● ●●●● ■ Memory arrays are dense,regular,and therefore susceptible to defects Memories are often deeply embedded in a design Logic I/O Pads 60%area CPU Core Memory 99%coverage Array : Memory Array IP Core sped User Core Memory Array Chip Memory Memory User Core Array 100%area 40%area 59%-99%coverage coverage 2021/8/18 集成电路可测性设计 72021/8/18 集成电路可测性设计 7 芯片中大量使用存储器