●●● ●● ●●●● ●●● 第十一章存储器测试 子料战女学 /966 University of Electronic Science and Technology of China

2021/8/18 集成电路可测性设计 2 第十一章 存储器测试

●●● ●● ●●●● 内容提要 ●●0● ●●o● ① 概述 ② 存储器模型 ③ 失效机制和故障模型 ④ 存储器的测试算法 2021/8/18 集成电路可测性设计 3

2021/8/18 集成电路可测性设计 3 内容提要 ① 概述 ② 存储器模型 ③ 失效机制和故障模型 ④ 存储器的测试算法

●●●● 0●●●● ●●●● ●●●● ●●0● ●●0● ●● 11.1概述 2021/8/18 集成电路可测性设计 4

2021/8/18 集成电路可测性设计 4 11.1 概述

● ●● 11.1概述 ●●●● ●●● o Memories (esp.RAM)are at the forefront of commercial electronic designs DRAMs are the technology driver for the semiconductor industry Memories are the most numerous IPs used in SOC designs (hundreds and >90%of an SoC in 2010) 2021/8/18 集成电路可测性设计 5

2021/8/18 集成电路可测性设计 5 11.1 概述 Memories (esp. RAM) are at the forefront of commercial electronic designs DRAMs are the technology driver for the semiconductor industry Memories are the most numerous IPs used in SOC designs (hundreds ! and >90% of an SoC in 2010)

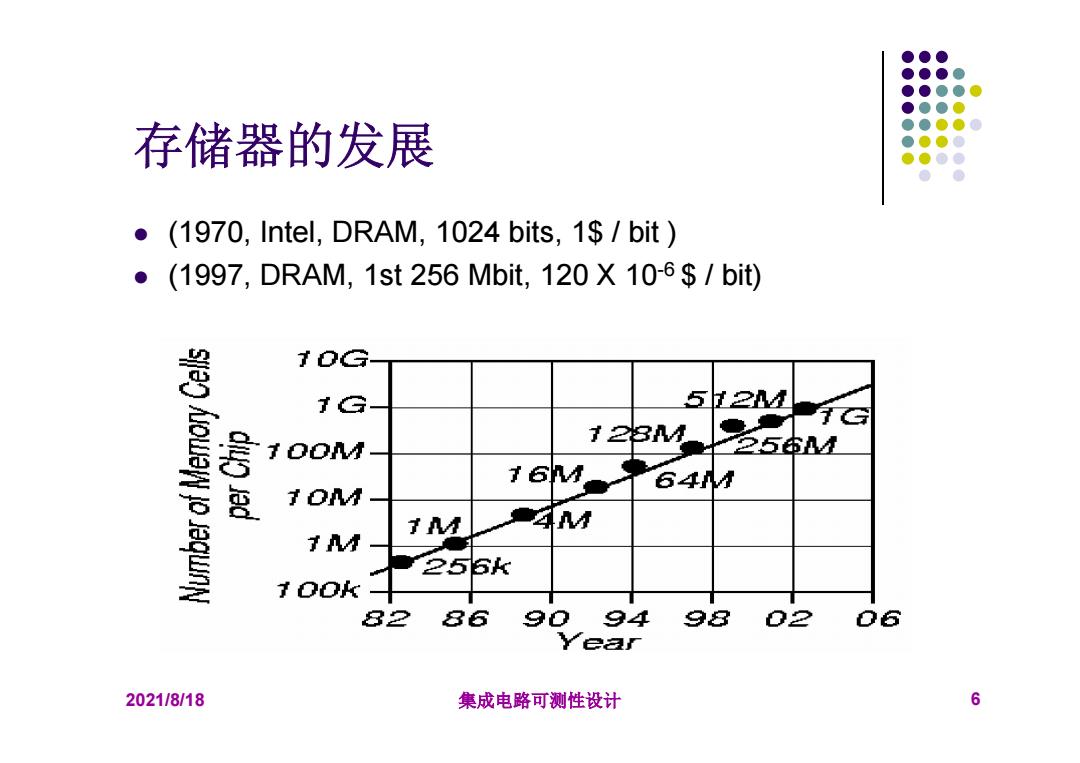

●● ●● 存储器的发展 ●● ●● ●● ●(1970,Intel,.DRAM,1024bits,1$/bit) ●(1997,DRAM,1st256Mbit,120X10-6$/bit) 邑 10G 1G 512M G 123nH 1O0M 5 16M ⑧ 64i 1OM 1M 4几A i几i 255k 1ook 82 36 994 02 06 Year 2021/8/18 集成电路可测性设计 6

2021/8/18 集成电路可测性设计 6 (1970, Intel, DRAM, 1024 bits, 1$ / bit ) (1997, DRAM, 1st 256 Mbit, 120 X 10-6 $ / bit) 存储器的发展

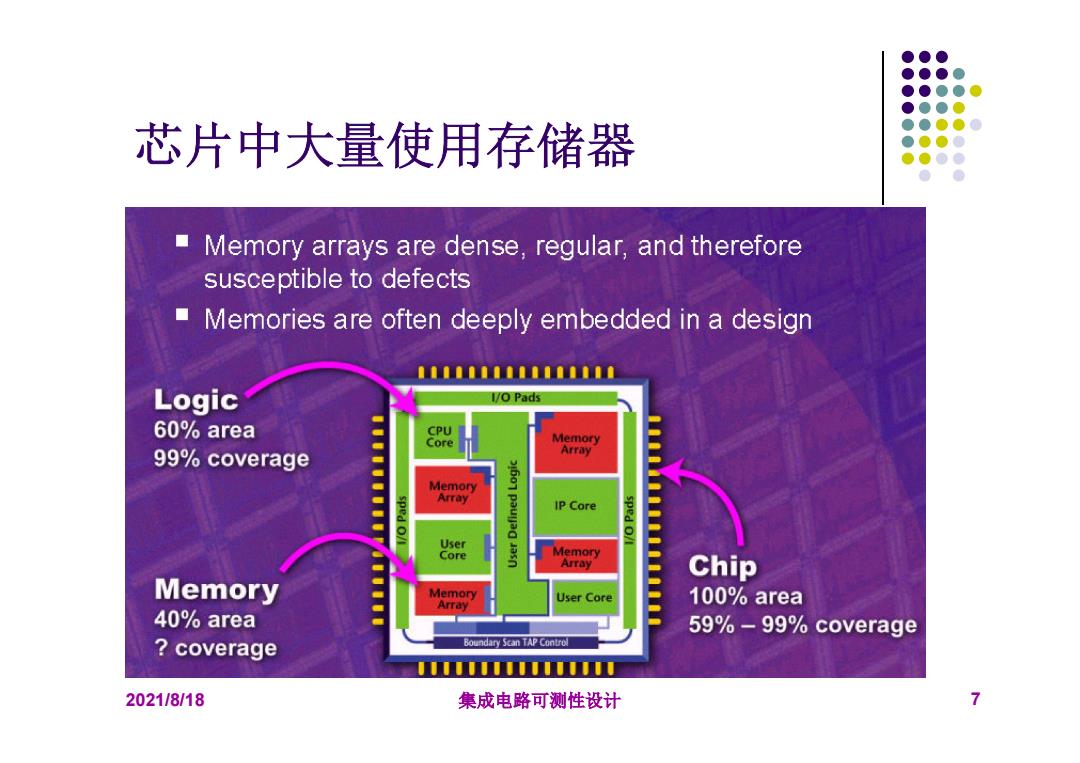

● ● 芯片中大量使用存储器 ●0 ●●●● ●●●● ■ Memory arrays are dense,regular,and therefore susceptible to defects Memories are often deeply embedded in a design Logic I/O Pads 60%area CPU Core Memory 99%coverage Array : Memory Array IP Core sped User Core Memory Array Chip Memory Memory User Core Array 100%area 40%area 59%-99%coverage coverage 2021/8/18 集成电路可测性设计 7

2021/8/18 集成电路可测性设计 7 芯片中大量使用存储器

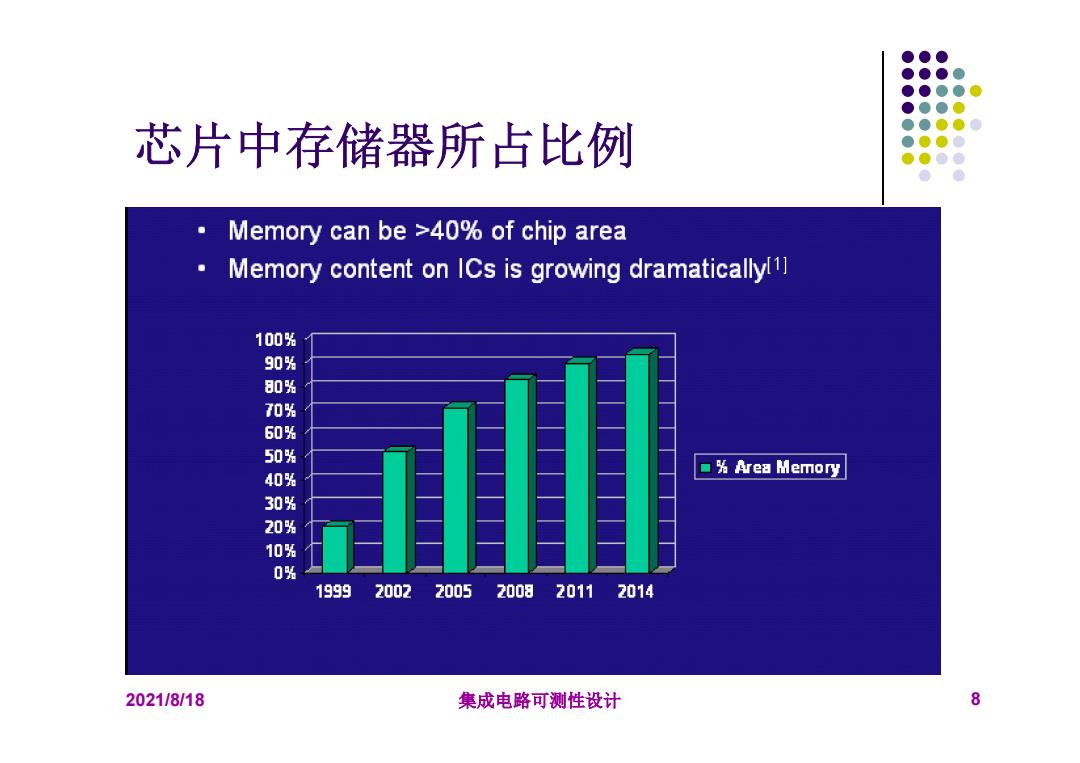

●0 ● ●●0 芯片中存储器所占比例 ●●●● ●●●● Memory can be >40%of chip area Memory content on ICs is growing dramatically[1] 100% 第1】1破040第14第第1假 ■%ea Memory 199920022005200820112014 2021/8/18 集成电路可测性设计 8

2021/8/18 集成电路可测性设计 8 芯片中存储器所占比例

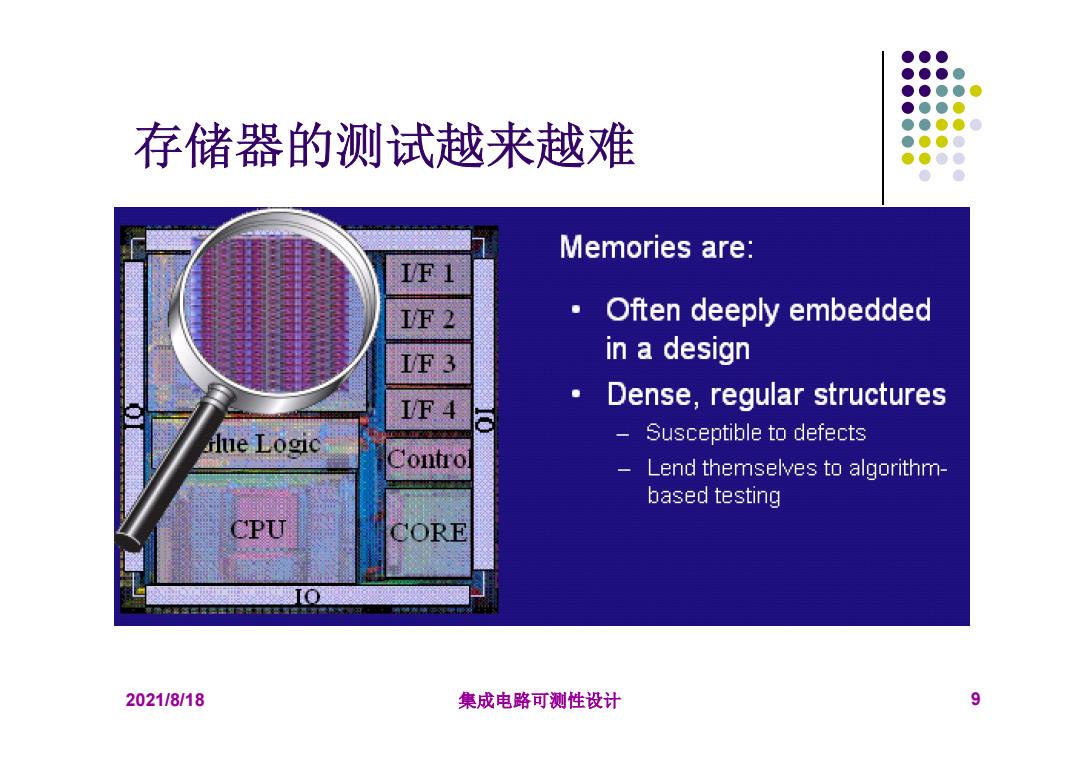

●0 ● ●●0 存储器的测试越来越难 ●●● ●●●● Memories are: Often deeply embedded 3 in a design Dense,regular structures rlue Logic Susceptible to defects ontro Lend themselves to algorithm- based testing CORE 2021/8/18 集成电路可测性设计 9

2021/8/18 集成电路可测性设计 9 存储器的测试越来越难

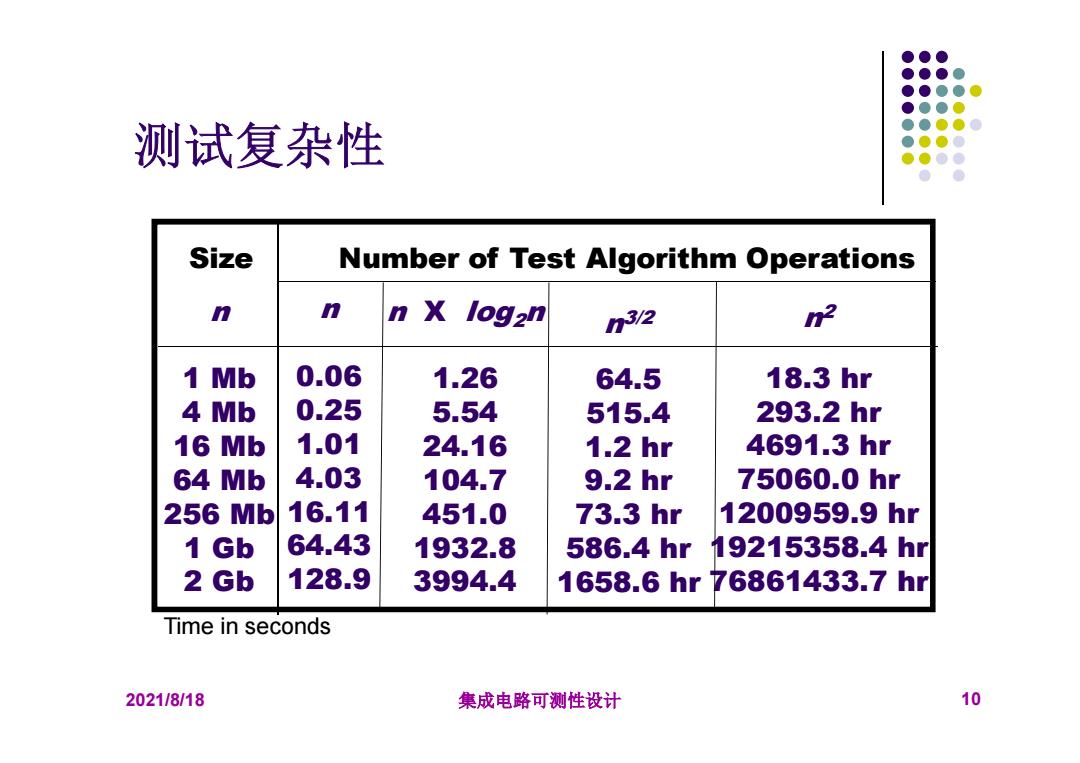

● ●0 测试复杂性 ●●●● ●●● Size Number of Test Algorithm Operations X log2n m32 2 1Mb 0.06 1.26 64.5 18.3hr 4 Mb 0.25 5.54 515.4 293.2hr 16 Mb 1.01 24.16 1.2hr 4691.3hr 64 Mb 4.03 104.7 9.2hr 75060.0hr 256Mb 16.11 451.0 73.3hr 1200959.9hr 1Gb 64.43 1932.8 586.4hr 19215358.4hr 2 Gb 128.9 3994.4 1658.6hr76861433.7 hr Time in seconds 2021/8/18 集成电路可测性设计 10

2021/8/18 集成电路可测性设计 10 n 1 Mb 4 Mb 16 Mb 64 Mb 256 Mb 1 Gb 2 Gb n 0.06 0.25 1.01 4.03 16.11 64.43 128.9 n X log2n 1.26 5.54 24.16 104.7 451.0 1932.8 3994.4 n3/2 64.5 515.4 1.2 hr 9.2 hr 73.3 hr 586.4 hr 1658.6 hr n2 18.3 hr 293.2 hr 4691.3 hr 75060.0 hr 1200959.9 hr 19215358.4 hr 76861433.7 hr Size Number of Test Algorithm Operations 测试复杂性 Time in seconds

●● ●●● ●●● ●●●0 存储器种类 ●●●● ■ SRAM DRAM High-speed read and write ·Read and write ·Volatile ·High density ■Register file 。 Volatile ·ide and shallow Flash ·Less dense ·Read and write ·Volatile Non-volatile ROM ·Read only Non-volatile 2021/8/18 集成电路可测性设计 11

2021/8/18 集成电路可测性设计 11 存储器种类