教材和参考资料 冬教材 -雷绍充,邵志标,梁峰,《超大规模集成电路测试》,电子工业出 版社2008.5 -在线教材网址: >https://www.keledge.com/wrap/details/book?id=193571 ?参考资料 -VLSI Test Principles and Architectures),L.T.Wang,C.W. Wu,and X.Wen,Morgan Kaufmann,2006. Digital Systems Testing and Testable Design>, M.Abramovici,M.A.Breuer,A.D.Friedman,Computer Science Press,1995 Testing of Digital Systems),Niraj,Sandeep Gupta, Cambridge University Press,2003 。软件 VCS,DFT Compiler,TetraMax 2020/9/4 集成电路可测性设计 2

2020/9/4 集成电路可测性设计 2 教材和参考资料 教材 雷绍充,邵志标,梁峰,《超大规模集成电路测试》,电子工业出 版社 2008.5 在线教材网址: https://www.keledge.com/wrap/details/book?id=193571 参考资料 《VLSI Test Principles and Architectures》, L.T. Wang, C.W. Wu, and X. Wen, Morgan Kaufmann, 2006. 《Digital Systems Testing and Testable Design》, M.Abramovici, M.A.Breuer, A.D.Friedman,Computer Science Press,1995 《Testing of Digital Systems》,Niraj,Sandeep Gupta, Cambridge University Press,2003 软件 VCS,DFT Compiler,TetraMax

司外大华花秀教材一黄 超大规模 数字系统测甘 集成电路测试 和可测性设 窗提克那忠标单峰。编酒 TE VLSI TES DESION FOR PRINCIPLES TESTABILITY ARCHITECTU AM LAUND-TERNO WANG CHENO-WEN WUX 鸟独酷 2020/9/4 集成电路可测性设计 3

2020/9/4 集成电路可测性设计 3

EDA/DFT技术相关网站 1C设计及制造(伴号体、微电子到 芯知乎微电子杂谈】 FPGA|ASIC|IC前端设计论坛 Analog/RFIC设计(44 后端设计(39) 主题:200,帖数:1496 FPGA 40 主题:6万,帖傲:147万 主题:2万,帖傲:29万 最后发表:昨天18:39 主题:5万,帖数:92万 最后发表:10分钟前 最后发表:1分钟前 最后发表:8分钟前 IC测试与可测性(3) 1C验证(12 MEMS(微机电系统)(1) S0C设计论坛(⑤) 主题:1310,帖数:2万 主题:7767,帖数:13万 主题:335,帖数:4769 主题:1842,帖擞:3万 最后发表:1小时前 最后发表:2小时前 最后发表:2小时前 最后发表:3小时崩 Analog Layout(版图)(⑦ 脚本语言(script)学习交流(6) 集成电路生产/封装/工艺3) ESD/EoS和atchup(花片级) 主题:6167,帖数:7万 主题:1512,帖傲:2万 主题:1766,数:2万 主题:484,帖傲:8888 最后发表:1小时前 最后发表:半小时前 最后发表:3小时前 最后发表:昨天07:02 开源CPU设计(Risc- 通信C设计及开源通信算法 封装设计(1) 半导体新材料 v,0 penMips等)(7) 主题:178,帖数:2689 主题:189,帖数:2044 主题:195,帖数:1670 主题:3612,帖数:8万 最后发表:4天前 最后发表:3小时前 最后发表:前天18:38 最后发表:半小时前 4

EDA/DFT技术相关网站 www.eetop.cn/bbs www.edaboard.com www.fpga.com.cn www.edaclub.com www.edachina.com 4

章节安排 1、概述(2学时) 2、电路测试基础(2学时) ÷3、验证、模拟和仿真(4学时) 4、自动测试生成(2学时) 5、专用可测性设计(2学时) ÷6、扫描设计(2-3学时) 。7、边界扫描法(2-3学时) 8、随机测试和伪随机测试(2学时) 主要以教科书为参考 名 9、内建自测试(2-3学时) 增加新的内容 10、电流测试(2学时) 强调实用性 11、存储器测试(2-3学时) 12、SoC测试(2学时) 13、处理器的测试(2) 2020/9/4 集成电路可测性设计 6

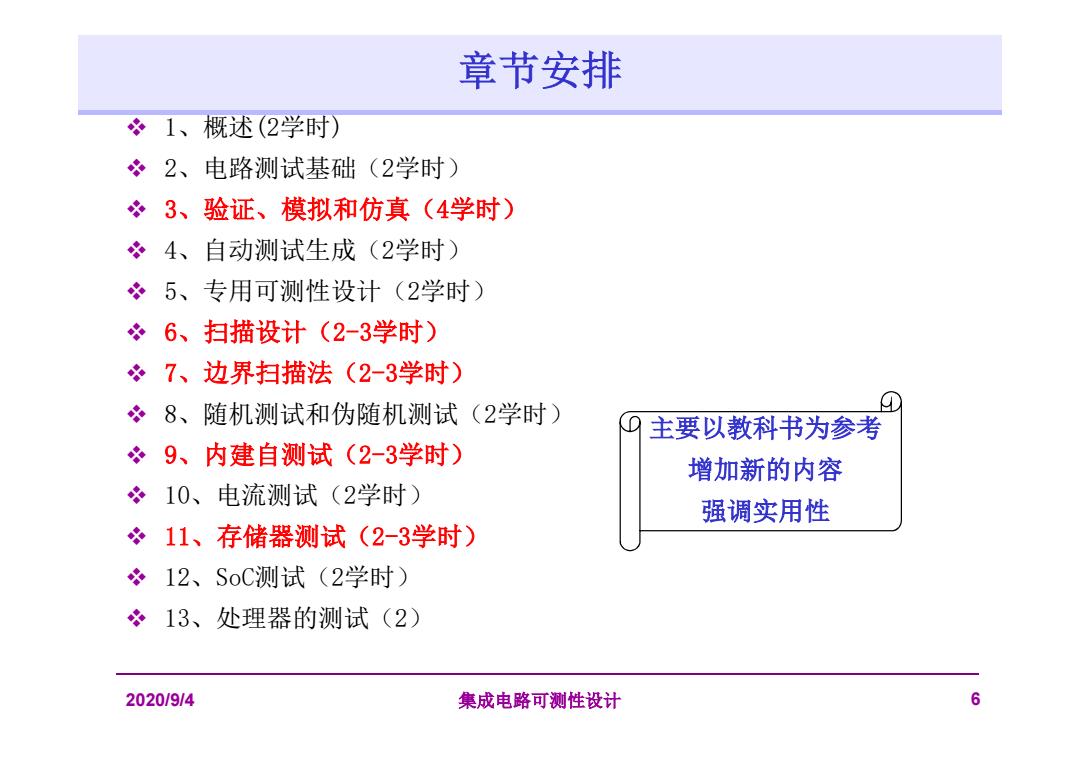

2020/9/4 集成电路可测性设计 6 章节安排 1、概述(2学时) 2、电路测试基础(2学时) 3、验证、模拟和仿真(4学时) 4、自动测试生成(2学时) 5、专用可测性设计(2学时) 6、扫描设计(2-3学时) 7、边界扫描法(2-3学时) 8、随机测试和伪随机测试(2学时) 9、内建自测试(2-3学时) 10、电流测试(2学时) 11、存储器测试(2-3学时) 12、SoC测试(2学时) 13、处理器的测试(2) 主要以教科书为参考 增加新的内容 强调实用性

第一章概述 包子件皮女学 1966 University of Electronic Science and Technology of China

第一章 概述

What 什么是DFT? Why 为什么DFT? How ① 怎么DFT? 2020/9/4 集成电路可测性设计 8

2020/9/4 集成电路可测性设计 8 什么是DFT? 为什么DFT? 怎么DFT? What Why How

基本目的 可能感兴趣的职位: Senior DFT Engineer 面议 逐点半导体(上海)有限公司 硕士及以上|5年工作经验 上海 电子技术半导体/集成电路 资深DFT工程师 面议 中晟宏芯 本科及以上|3年工作经验 上海-浦东新区 电子技术半导体/集成电路 DFT Engineer 30-42万 顺卓微电子 学历不限|1年工作经验 上海-浦东新区 电子技术/半导体/集成电路 Design for Test Engineer(... 面议 西安紫光国芯半导体有限公司 本科及以上|3年工作经验 上海 电子技术/半导体/集成电路 资深DFT工程师 面议 北京比特大陆科技有限公司 统招本科|经验不限 北凉 电子技术半导体/集成电路 9

2020/9/4 集成电路可测性设计 9 基本目的 使学生掌握VLSI系统测试和可测性设计的基本原理 和主要方法; 使学生把握VLSI系统测试和可测性设计的学科前沿 方向; 使学生对EDA系统中有关测试和可测性设计工具有 初步认识和实践体会; DFT是VLSI设计工程师的基本技能; 就职的需求:设计公司很多有DFT的试题和 要求。 百度一下“DFT 招聘”……

一、研究意义

一、研究意义

为什么需要DFT技术? 冬下面需要了解一些产业背景和拓展的知识 11

下面需要了解一些产业背景和拓展的知识 11 为什么需要DFT技术?

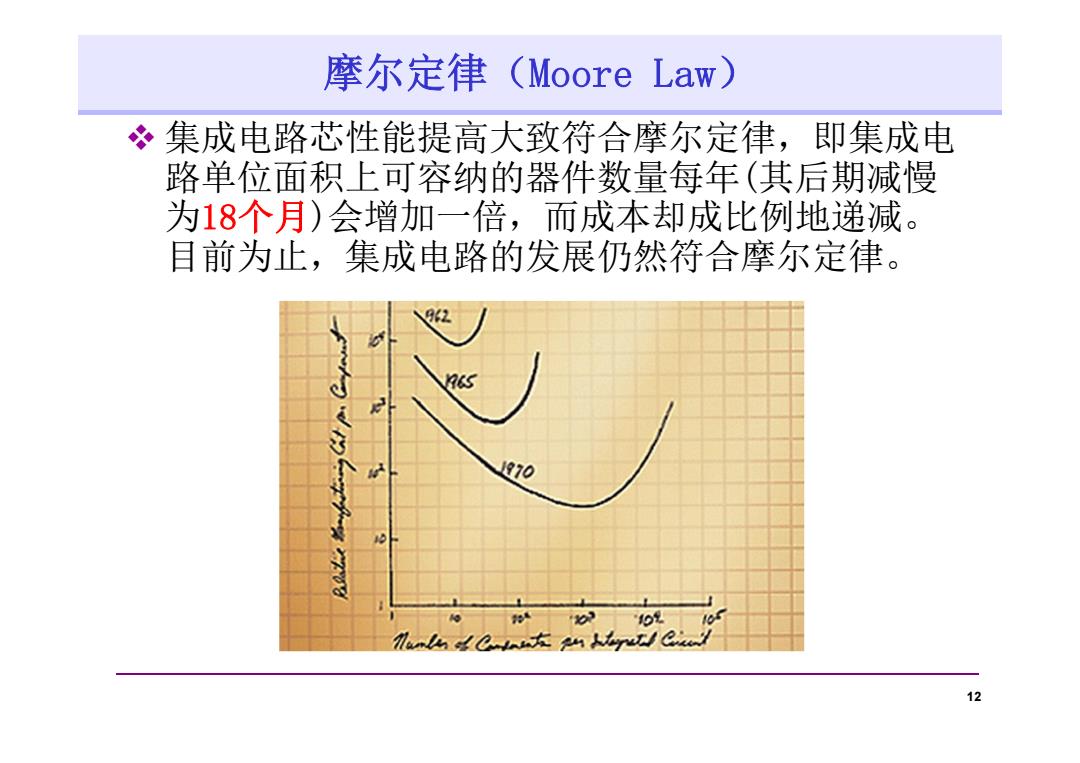

摩尔定律(Moore Law) 集成电路芯性能提高大致符合摩尔定律,即集成电 路单位面积上可容纳的器件数量每年(其后期减慢 为18个月)会增加一倍,而成本却成比例地递减。 目前为止,集成电路的发展仍然符合摩尔定律。 070 12

摩尔定律(Moore Law) 集成电路芯性能提高大致符合摩尔定律,即集成电 路单位面积上可容纳的器件数量每年(其后期减慢 为18个月)会增加一倍,而成本却成比例地递减。 目前为止,集成电路的发展仍然符合摩尔定律。 12