Topic4:VLSI for DSP Digital Signal Processing ·Signal&System ·DSP system ·Description for DSP FIR Filter Design Implement 。Digital Filter Specification Design Hardware Implementation Some Examples Digital Down Converter 。 Central Processing Unit h国 2021/1/13 ASIC Design,by Yan Bo 2

ASIC Design, by Yan Bo Topic4: VLSI for DSP Digital Signal Processing • Signal & System • DSP system • Description for DSP FIR Filter Design & Implement • Digital Filter • Specification Design • Hardware Implementation Some Examples • Digital Down Converter • Central Processing Unit • …… 2021/1/13 2

集成电路是信息行业的引擎(万物皆比特) 信良论之父 计算机之父 晶体管之父 克劳漉·香农 阿兰·图灵 威廉姆·背克利 C.Shannon A.Turing W.Shockley ASIC Design,by Yan Bo 3

ASIC Design, by Yan Bo 集成电路是信息行业的引擎(万物皆比特) 信息论之父 克劳德·香农 C.Shannon 3 晶体管之父 威廉姆·肖克利 W.Shockley 计算机之父 阿兰·图灵 A.Turing

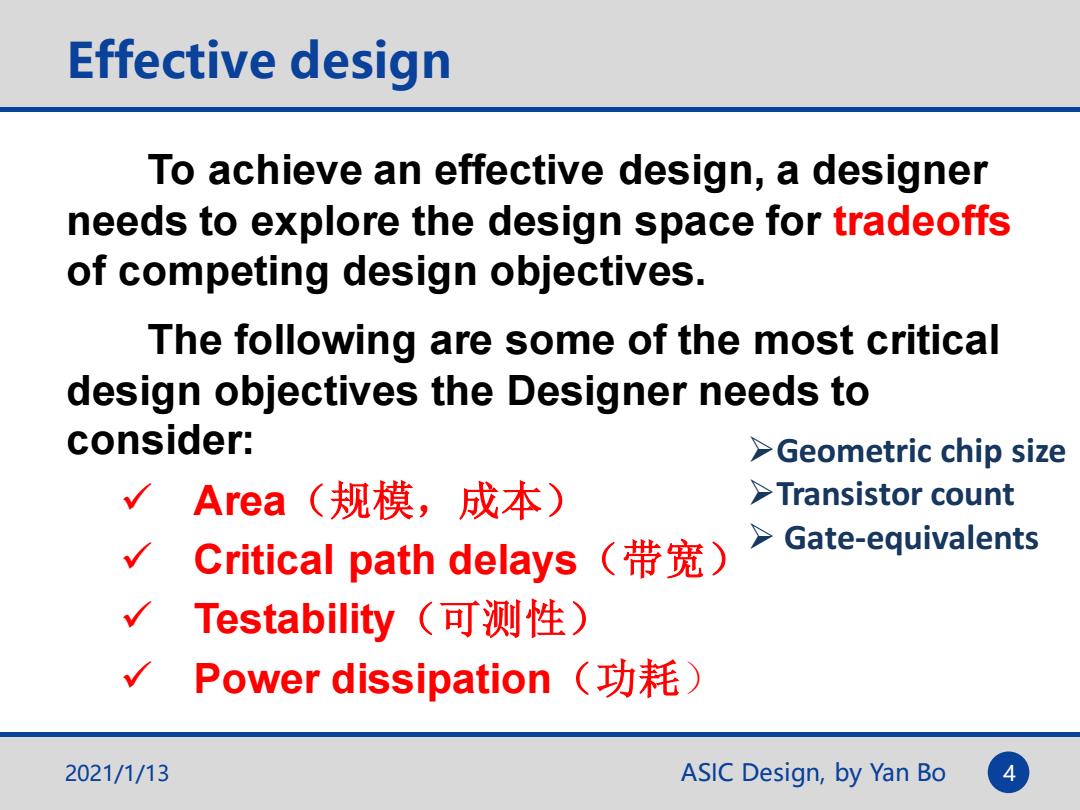

Effective design To achieve an effective design,a designer needs to explore the design space for tradeoffs of competing design objectives. The following are some of the most critical design objectives the Designer needs to consider: >Geometric chip size Area(规模,成本) >Transistor count Critical path delays(带宽) Gate-equivalents Testability(可测性) Power dissipation(功耗) 2021/1/13 ASIC Design,by Yan Bo

ASIC Design, by Yan Bo Effective design 2021/1/13 4 To achieve an effective design, a designer needs to explore the design space for tradeoffs of competing design objectives. The following are some of the most critical design objectives the Designer needs to consider: ✓ Area(规模,成本) ✓ Critical path delays(带宽) ✓ Testability(可测性) ✓ Power dissipation(功耗) ➢Geometric chip size ➢Transistor count ➢ Gate-equivalents

Topic4:VLSI for DSP Digital Signal Processing ·Signal&System 。DSP system ·Description for DSP FIR Filter Design Implement 。Digital Filter Specification Design Hardware Implementation Some Examples Digital Down Converter 。 Central Processing Unit 2021/1/13 ASIC Design,by Yan Bo 5

ASIC Design, by Yan Bo Topic4: VLSI for DSP Digital Signal Processing • Signal & System • DSP system • Description for DSP FIR Filter Design & Implement • Digital Filter • Specification Design • Hardware Implementation Some Examples • Digital Down Converter • Central Processing Unit • …… 2021/1/13 5

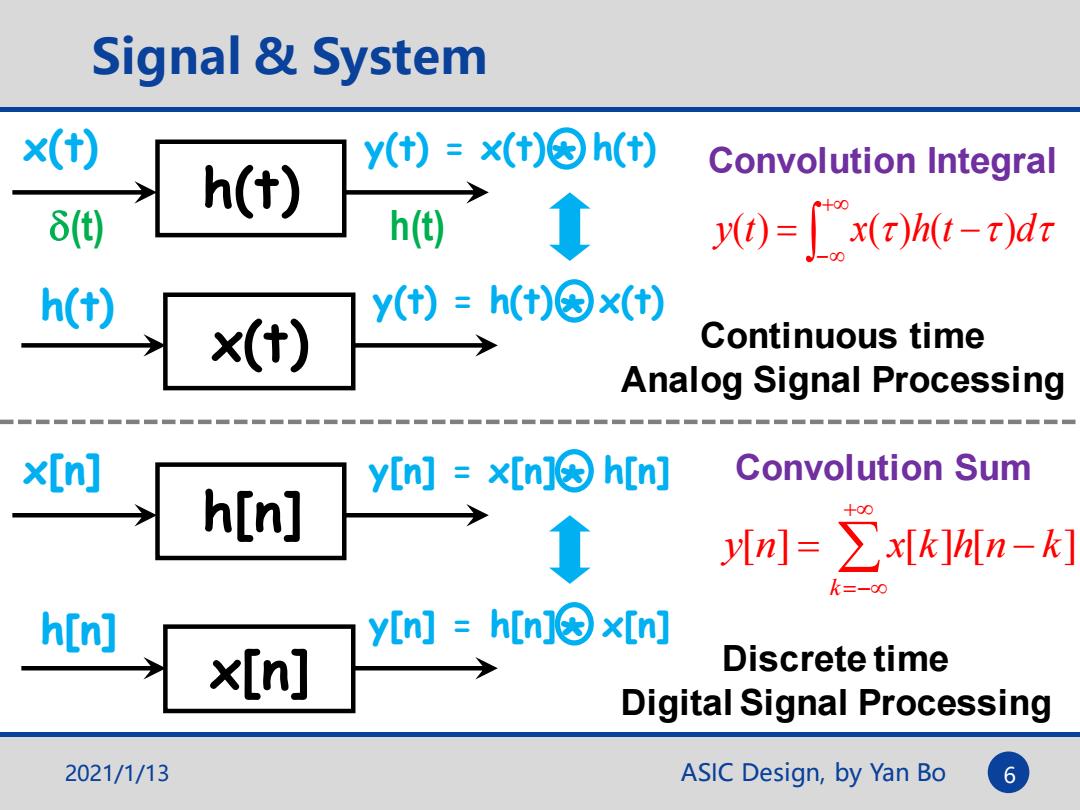

Signal System (t) y(t)=x(t)因h(t) 俐 h(t) Convolution Integral h() )=x(r)ht-t)d红 h(t) y(t)=h(t)©x(t) x(t) Continuous time Analog Signal Processing ×[n)] y[n]=x[n因h[n Convolution Sum h[n] 十00 yn]=∑x[k]hn-k1 k=-00 h[n] y[n=h[n]©x[n x[n] Discrete time Digital Signal Processing 2021/1/13 ASIC Design,by Yan Bo 6

ASIC Design, by Yan Bo Signal & System 2021/1/13 6 + =− = − k y[n] x[k]h[n k] x(t) y(t)=? System h(t) LTI (t) h(t) y(t) = x(t) h(t) Continuous time Analog Signal Processing * Convolution Integral x(t) h(t) y(t) = h(t) x(t) * x[n] Y[n]=? h[n] LTI y[n] = x[n] h[n] * x[n] h[n] y[n] = h[n] x[n] * Discrete time Digital Signal Processing Convolution Sum + − y(t) = x( )h(t − )d

Topic4:VLSI for DSP Digital Signal Processing ·Signal&System 。DSP system 。Description for DSP FIR Filter Design Implement 。Digital Filter Specification Design Hardware Implementation Some Examples Digital Down Converter 。 Central Processing Unit h 2021/1/13 ASIC Design,by Yan Bo 7

ASIC Design, by Yan Bo Topic4: VLSI for DSP Digital Signal Processing • Signal & System • DSP system • Description for DSP FIR Filter Design & Implement • Digital Filter • Specification Design • Hardware Implementation Some Examples • Digital Down Converter • Central Processing Unit • …… 2021/1/13 7

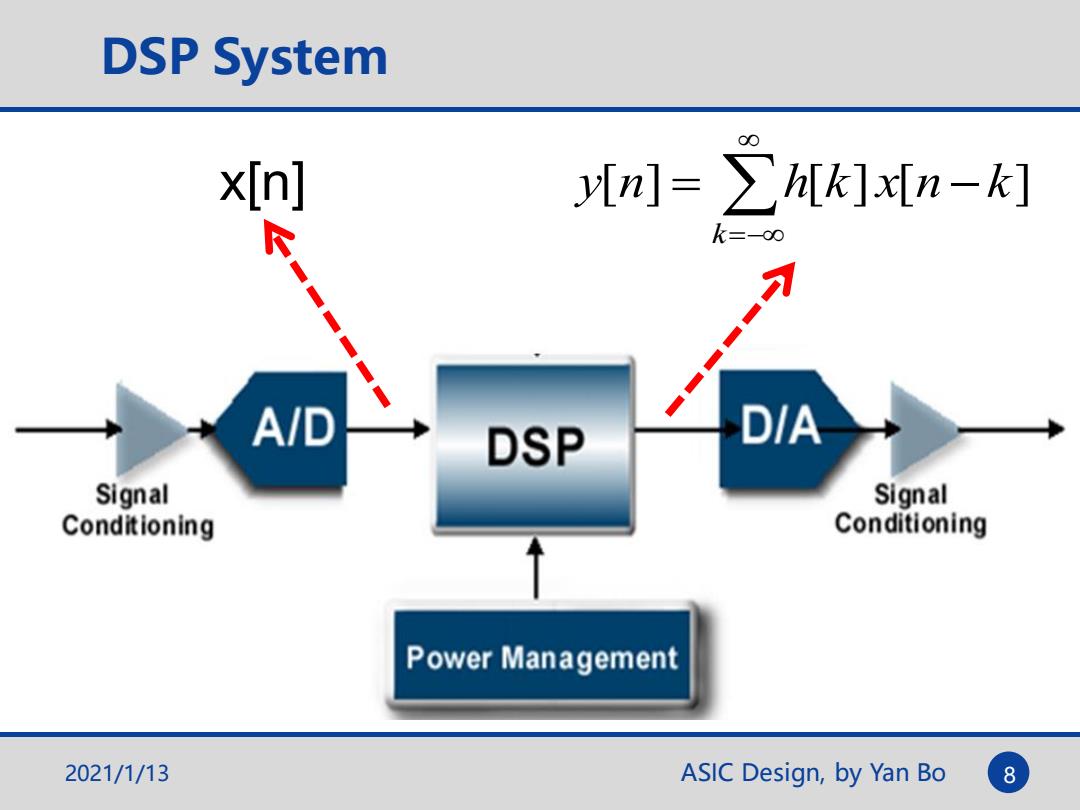

DSP System [ y[n]=∑hk]x[n-k] k=-o∞ ← A/D DSP D/A Signal Signal Conditioning Conditioning Power Management 2021/1/13 ASIC Design,by Yan Bo 8

ASIC Design, by Yan Bo DSP System =− = − k y[n] h[k] x[n k] 2021/1/13 8 x[n]

Wireless Communication System 增加冗余信道编码信息 用基带信宴调制款波信号参量 用于接受方检猎和纠错 用于适应发送信道特正 ■■■■■■ 基玷 : 16/64 Turbo eNodeB CRC 预编 射频 编码 编码 服 务 器 码 旺映射 发送 数字前端 单元 ◆ ■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■ ■■■■ ■■■■■■■■■ 行 CTE下行信道物理层①SP模快 接收 16/64 CRC Turbo 解交织 QAM 旺逆 OFDM UE 校验 ADC 译码 速率 /P 信号检 信道估 解调 变 匹配 解调 计 射 手机 2021/1/13 ASIC Design,by Yan Bo 9

ASIC Design, by Yan Bo Wireless Communication System 2021/1/13 9 基站 手机 下 行 增加冗余信道编码信息 用于接受方检错和纠错 用基带信息调制载波信号参量 用于适应发送信道特征 发送 接收 LTE下行信道物理层 射频 单元 数 字 前 端 服 务 器 DSP模块

Wireless Communication System 射频远端RRU宽带接口CPRI Radio Remote Unit Common Public PCIe Radio Interface CRA架构 数字 cloud radio access network. 弟瑞 Server 协作式 Cooperative 10GE 集中式 /IB Centralized 前端胶换 后端交换 载波 云计算 还移 Cloud RRU 无线接入网 FPGA+ARM 高性能计算机 RAN 射频前端 基带池 2021/1/13 ASIC Design,by Yan Bo 10

ASIC Design, by Yan Bo Wireless Communication System 2021/1/13 10 CRAN架构 cloud radio access network 宽带接口CPRI Common Public Radio Interface 射频远端RRU Radio Remote Unit 数字 前端 Server PCIe 10GE /IB 载波 迁移 FPGA+ARM 高性能计算机 射频前端 基带池 协作式 Cooperative 集中式 Centralized 云计算 Cloud 无线接入网 RAN

Topic4:VLSI for DSP Digital Signal Processing ·Signal&System 。DSP system ·Description for DSP FIR Filter Design Implement 。Digital Filter Specification Design Hardware Implementation Some Examples Digital Down Converter 。 Central Processing Unit h国 2021/1/13 ASIC Design,by Yan Bo 11

ASIC Design, by Yan Bo Topic4: VLSI for DSP Digital Signal Processing • Signal & System • DSP system • Description for DSP FIR Filter Design & Implement • Digital Filter • Specification Design • Hardware Implementation Some Examples • Digital Down Converter • Central Processing Unit • …… 2021/1/13 11