电子科越女学 niversity of Electreaie Sclence and Techaolepof Chiaa Preface Introduction to VLSI Dr.Ling National Key Lab of Science and Technology on Communication

Preface Introduction to VLSI Dr. Ling National Key Lab of Science and Technology on Communication

Background requirement o Digital signal process VHDL or Verilog Tools:Matlab/Simulink,Xilinx ISE,Modelsim 里子5电8书粉 1 出 VLSI数宇信号处理系统 VLS1数字信号处理系统 设计与实现 设计与实现 (英文版) VLSI DIGITAL SIGNAL VLSI DIGITAL PROCESSING SIGNAL PROCESSING SYSTEMS SYSTEMS DESIGN AND DINCA IMPLEMENTATION CHINA-PUB.COM CHINA-PUB.COM 2021年2月 2

2021年2月 2 Background requirement Digital signal process VHDL or Verilog Tools: Matlab/Simulink, Xilinx ISE, Modelsim

Course design 课堂问答40分。 课程设计60分:根据学号尾数做相应一题,提交设计报告(20分) Matlab/simulink代码结果(20分)和RTL代码仿真结果(20分)。 ■加分项:硬件下板测试(40分) O、运用pipeline技术进行Cordic算法电路设计 1、运用unfolding技术进行格型滤波器设计 2、运用folding技术进行匹配滤波器设计 3、运用systolic技术进行三角矩阵求逆电路(或4x4矩阵乘法器)设计 4、运用fast convolution技术进行4x3线性卷积(或60点FFT)设计 5、运用FFA结构进行成形滤波器设计 6、运用频率抽取的快速DCT设计 7、运用离散超前流水进行IIR滤波器设计 8、Baugh-Nooley乘法器设计 9、可配置的比特级乘法器设计 2021年2月 3

2021年2月 3 Course design 课堂问答40分。 课程设计60分:根据学号尾数做相应一题,提交设计报告(20分)、 Matlab/simulink代码结果(20分)和RTL代码仿真结果(20分) 。 加分项:硬件下板测试(40分) 0、运用pipeline技术进行Cordic算法电路设计 1、运用unfolding技术进行格型滤波器设计 2、运用folding技术进行匹配滤波器设计 3、运用systolic技术进行三角矩阵求逆电路(或4x4矩阵乘法器)设计 4、运用fast convolution技术进行4x3线性卷积(或60点FFT)设计 5、运用FFA结构进行成形滤波器设计 6、运用频率抽取的快速DCT设计 7、运用离散超前流水进行IIR滤波器设计 8、Baugh-Wooley乘法器设计 9、可配置的比特级乘法器设计

■Goal: Computation speed:faster Silicon area:smaller Power consumption:lower ■Methods: Optimize the algorithm Optimize the implementation infrastructure Improve the silicon technology 2021年2月 4

Goal: Computation speed: faster Silicon area: smaller Power consumption: lower Methods: Optimize the algorithm Optimize the implementation infrastructure Improve the silicon technology 2021年2月 4

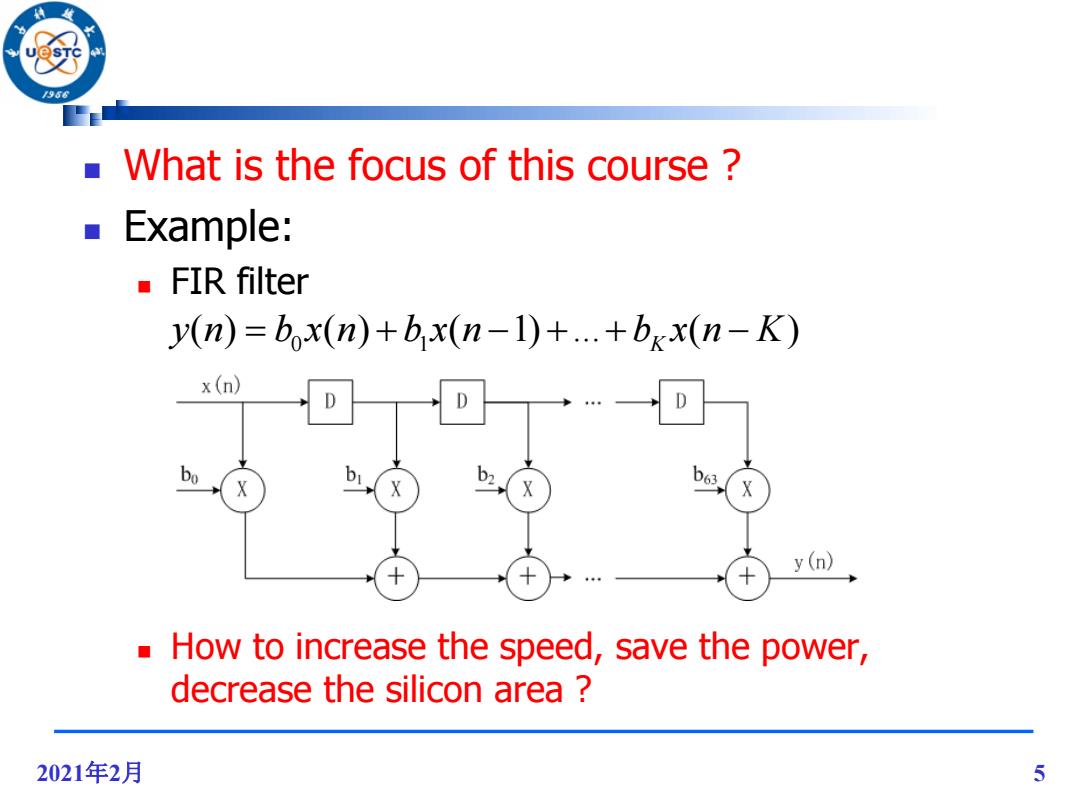

/956 What is the focus of this course Example: FIR filter y(n)=box(n)+bx(n-1)+...+bxx(n-K) x (n) D bo b63 y(n) How to increase the speed,save the power, decrease the silicon area 2021年2月 5

What is the focus of this course ? Example: FIR filter 2021年2月 5 0 1 ( ) ( ) ( 1) ... ( ) K y n b x n b x n b x n K How to increase the speed, save the power, decrease the silicon area ?

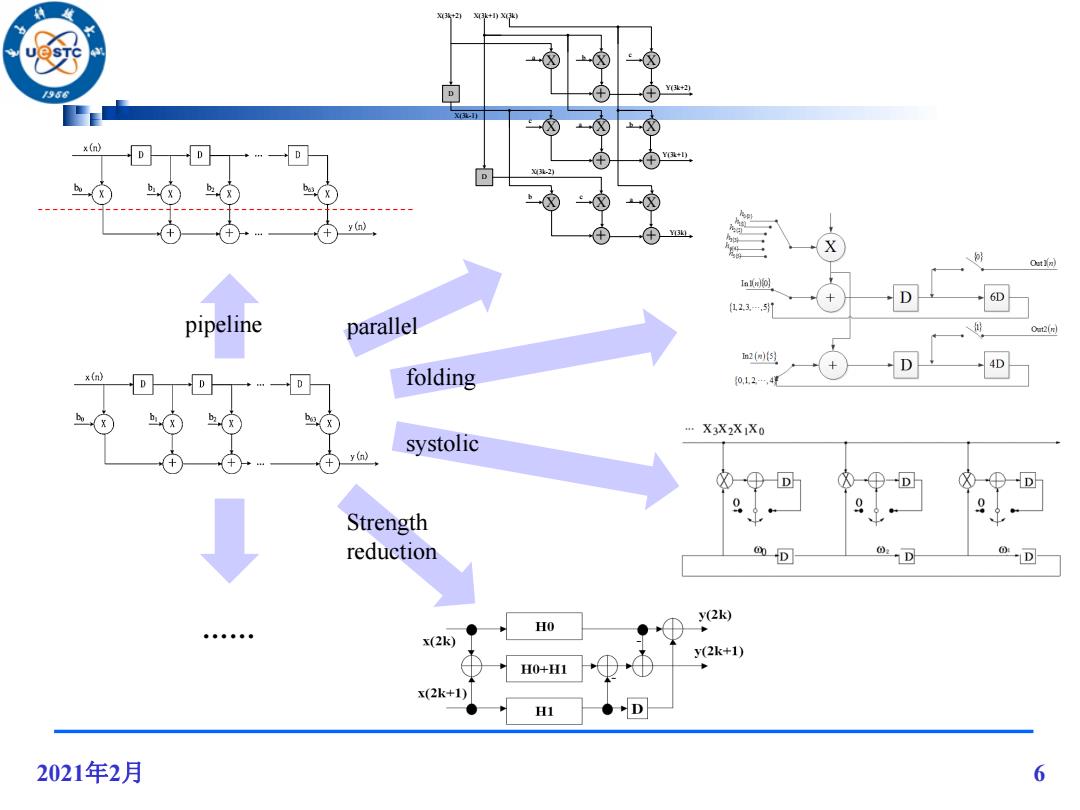

X x(n) 03L-2 y(n) Y3 Otln) Im或no D 6D 12.3… pipeline parallel Out2(n) m2包 D 4D x(n) folding 0,12…,4 …X3X2X1X0 systolic )y ②⊕D D Strength reduction D D y(2k) HO x(2k) y(2k+1) H0+H1 x(2k+1) H1 ●D 2021年2月 6

2021年2月 6 X X X X X X X X X + + + + + + D D X(3k+2) X(3k+1) X(3k) Y(3k+2) Y(3k+1) Y(3k) a a a b b b c c c X(3k-1) X(3k-2) pipeline parallel folding systolic Strength reduction ……

History of VLSI First integrated circuit (germanium),1958 Audion(Triode) First point contact transistor (germanium) Jack S.Kilby,Texas 1906,Lee De Forest 1947,John Bardeen,Walter Brattain Instruments And William Shockely Bell Laboratories Contained five components, three types: Transistors,resistors and capacitors 2021年2月 7

2021年2月 7 History of VLSI Audion (Triode) 1906, Lee De Forest First point contact transistor (germanium) 1947, John Bardeen, Walter Brattain And William Shockely Bell Laboratories First integrated circuit (germanium), 1958 Jack S. Kilby, Texas Instruments Contained five components, three types: Transistors, resistors and capacitors

/96d J.S.Kilby Robert Noyce Gordon Moore 2021年2月 8

2021年2月 8 J.S.Kilby Robert Noyce Gordon Moore

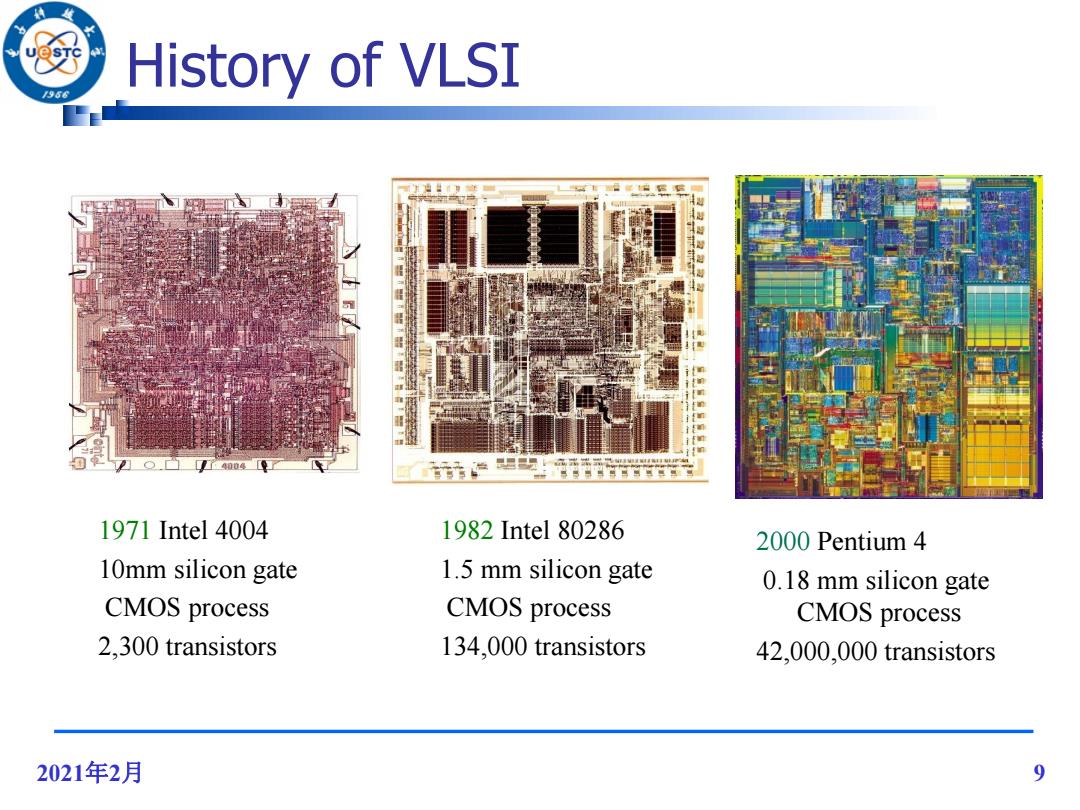

History of VLSI /96 1971 Intel4004 1982 Intel80286 2000 Pentium 4 10mm silicon gate 1.5 mm silicon gate 0.18 mm silicon gate CMOS process CMOS process CMOS process 2.300 transistors 134.000 transistors 42,000,000 transistors 2021年2月 9

2021年2月 9 History of VLSI 2000 Pentium 4 0.18 mm silicon gate CMOS process 42,000,000 transistors 1982 Intel 80286 1.5 mm silicon gate CMOS process 134,000 transistors 1971 Intel 4004 10mm silicon gate CMOS process 2,300 transistors

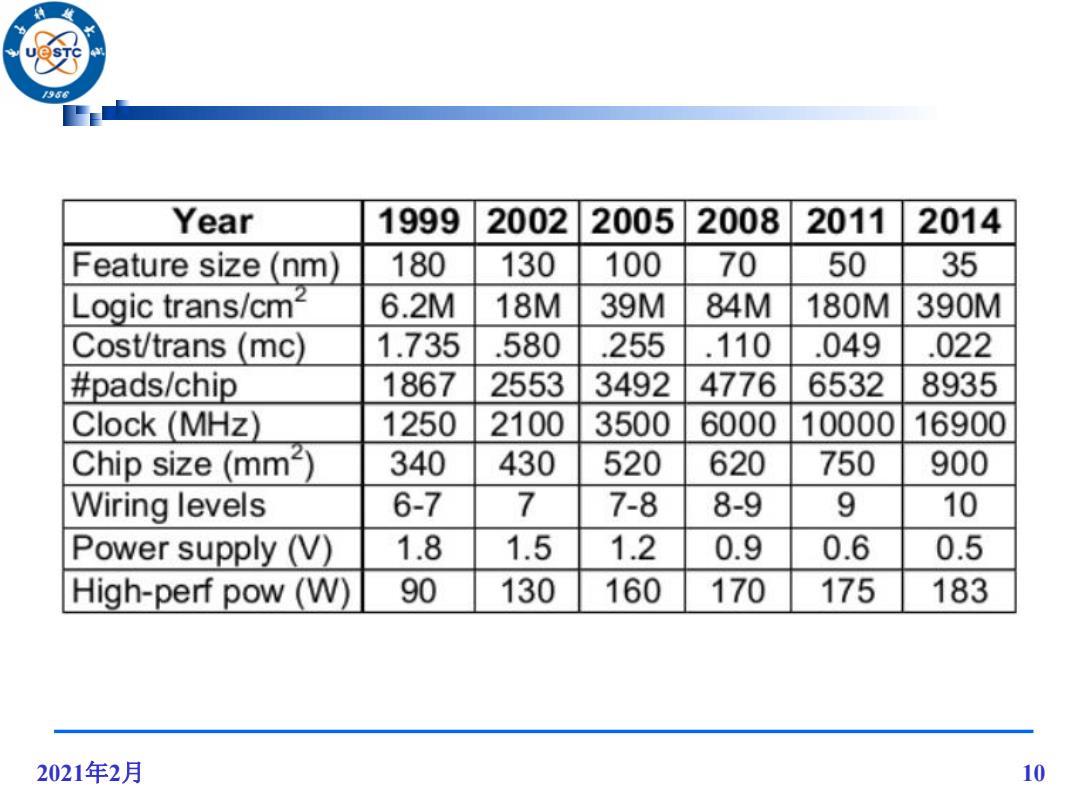

/966 Year 1999 2002 2005 2008 20112014 Feature size(nm 180 130 100 70 50 35 Logic trans/cm 6.2M 18M 39M 84M 180M 390M Cost/trans(mc) 1.735 .580 .255 .110 .049 .022 #pads/chip 1867 2553 3492 4776 6532 8935 Clock (MHz) 1250 2100 3500 6000 10000 16900 Chip size (mm2) 340 430 520 620 750 900 Wiring levels 6-7 7 7-8 8-9 9 10 Power supply (V) 1.8 1.5 1.2 0.9 0.6 0.5 High-perf pow(W) 90 130 160 170 175 183 2021年2月 10

2021年2月 10