二、测试的基本知识

二、测试的基本知识

讨论几个概念 IC验证(IC Verification) IC测试(IC Testing) 2020/9/4 集成电路可测性设计 3

2020/9/4 集成电路可测性设计 3 讨论几个概念 IC验证(IC Verification) IC测试(IC Testing)

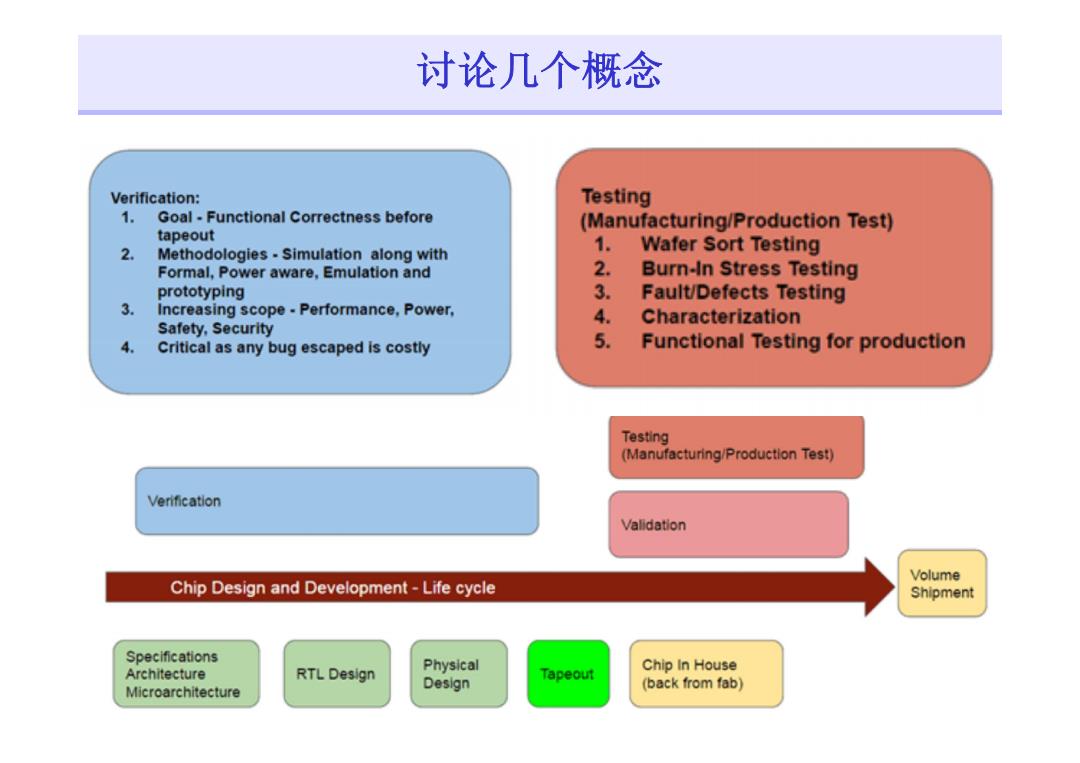

讨论几个概念 Verification: Testing 1. Goal-Functional Correctness before (Manufacturing/Production Test) tapeout 2. Methodologies-Simulation along with 1.Wafer Sort Testing Formal,Power aware,Emulation and 2. Burn-In Stress Testing prototyping 3. Fault/Defects Testing 3. Increasing scope -Performance,Power, 4. Characterization Safety.Security 4. Critical as any bug escaped is costly 5. Functional Testing for production Testing (Manufacturing/Production Test) Verification Validation Volume Chip Design and Development-Life cycle Shipment Specifications Architecture RTL Design Physical Chip In House Design Tapeout Microarchitecture back from fab】

2020/9/4 集成电路可测性设计 4 讨论几个概念

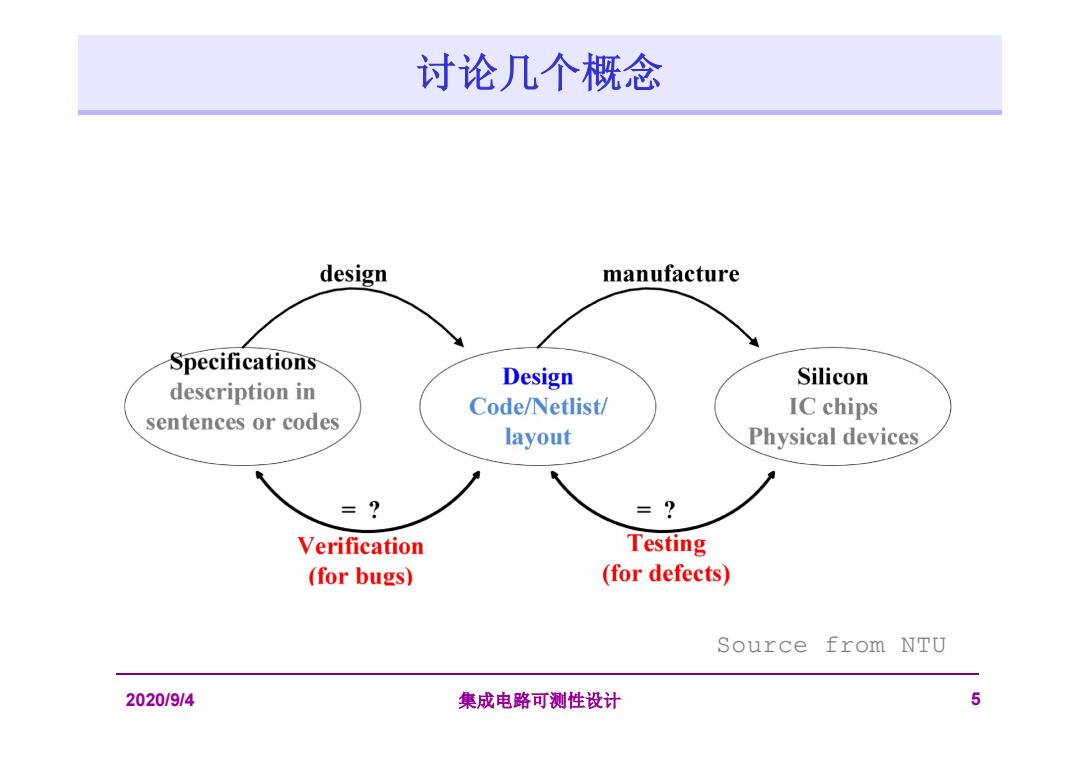

讨论几个概念 design manufacture Specifications Silicon description in Design Code/Netlist/ IC chips sentences or codes layout Physical devices =? Verification Testing (for bugs) (for defects) Source from i NTU 2020/9/4 集成电路可测性设计 5

讨论几个概念 2020/9/4 集成电路可测性设计 5 Source from NTU

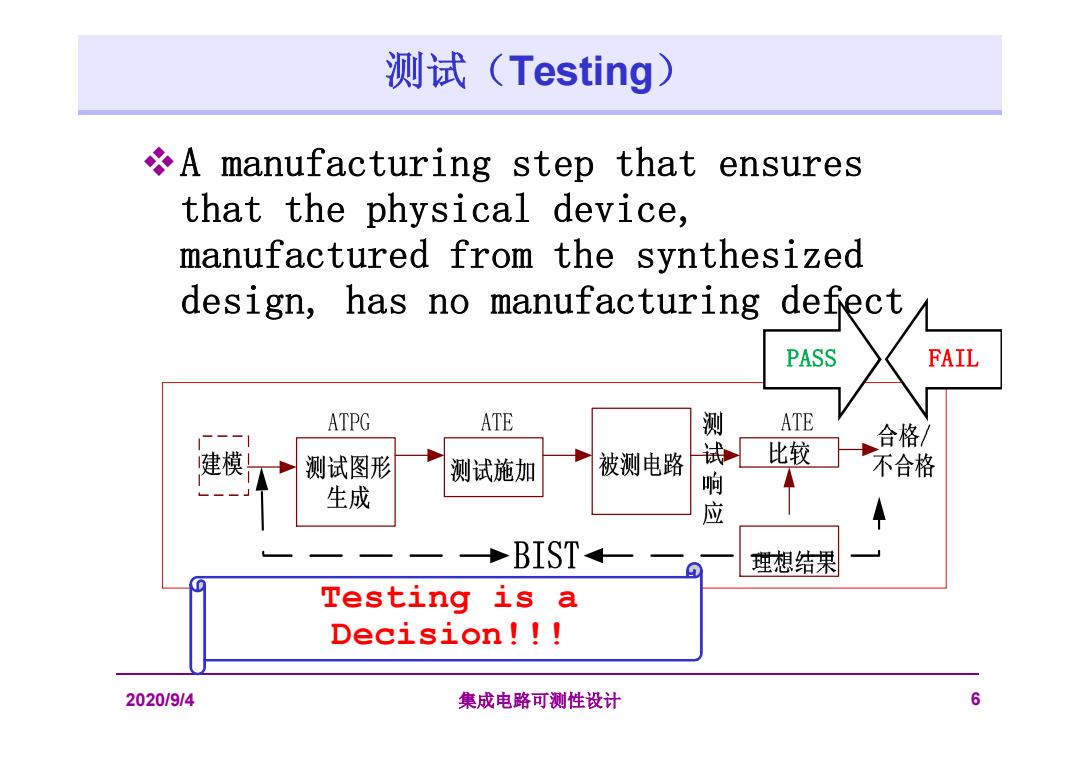

测试(Testing) A manufacturing step that e ensures that the physical device, manufactured from the synthesized design,has no manufacturing defect PASS FAIL ATPG ATE 测 ATE 合格/ 建模 测试图形 测试施加 被测电路 试 比较 不合格 生成 响 →BIST← 理想结果 Testing is a Decision!!! 2020/9/4 集成电路可测性设计 6

2020/9/4 集成电路可测性设计 6 测试(Testing) A manufacturing step that ensures that the physical device, manufactured from the synthesized design, has no manufacturing defect PASS FAIL Testing is a Decision!!!

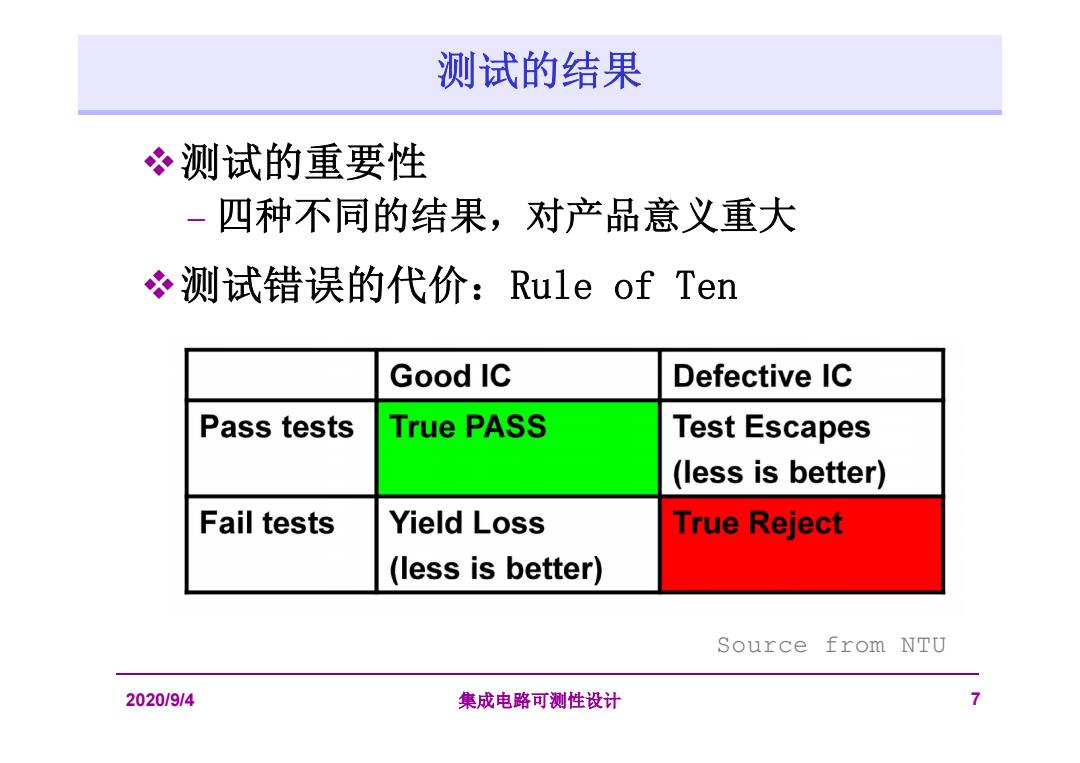

测试的结果 测试的重要性 -四种不同的结果,对产品意义重大 测试错误的代价:Rule of Ten Good IC Defective IC Pass tests True PASS Test Escapes (less is better) Fail tests Yield Loss True Reject (less is better) Source from NTU 2020/9/4 集成电路可测性设计 7

2020/9/4 集成电路可测性设计 7 测试的结果 测试的重要性 四种不同的结果,对产品意义重大 测试错误的代价:Rule of Ten Source from NTU

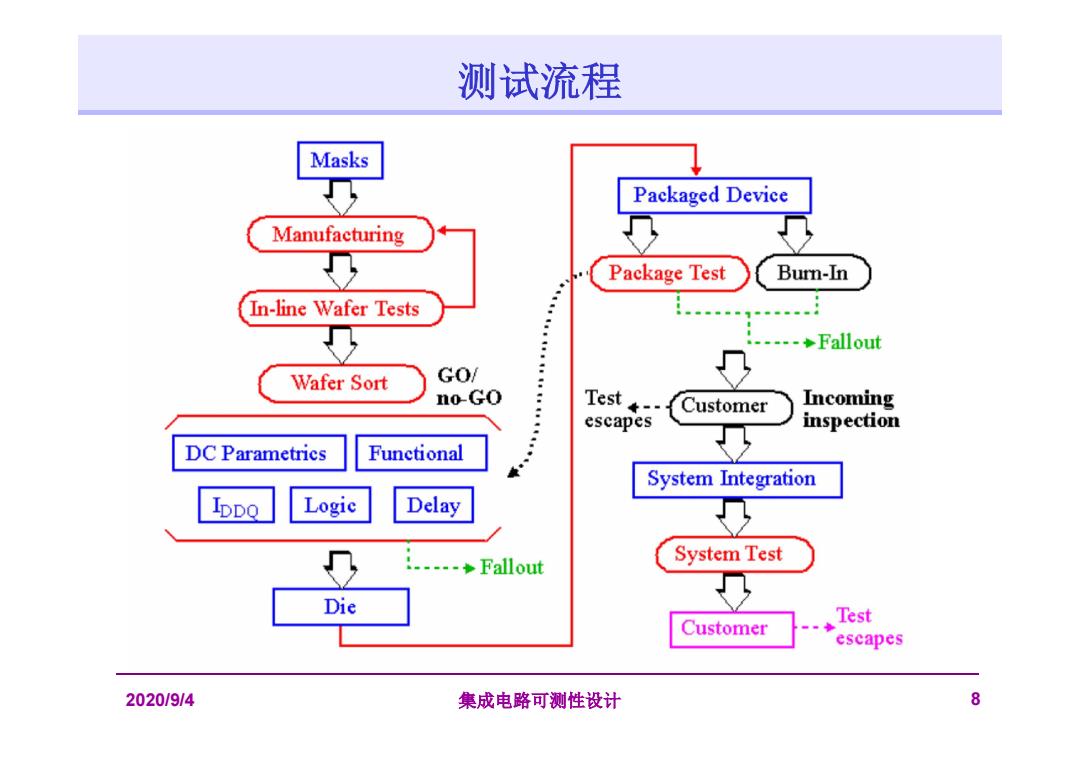

测试流程 Masks Packaged Device Manufacturing Package Test Burn-In In-line Wafer Tests ---◆Fallout Wafer Sort GO/ no-GO Test+-- Customer Incoming escapes inspection DC Parametrics Functional System Integration IDDQ Logic Delay ----Fallout System Test 2 Die Test Customer escapes 2020/9/4 集成电路可测性设计 8

2020/9/4 集成电路可测性设计 8 测试流程

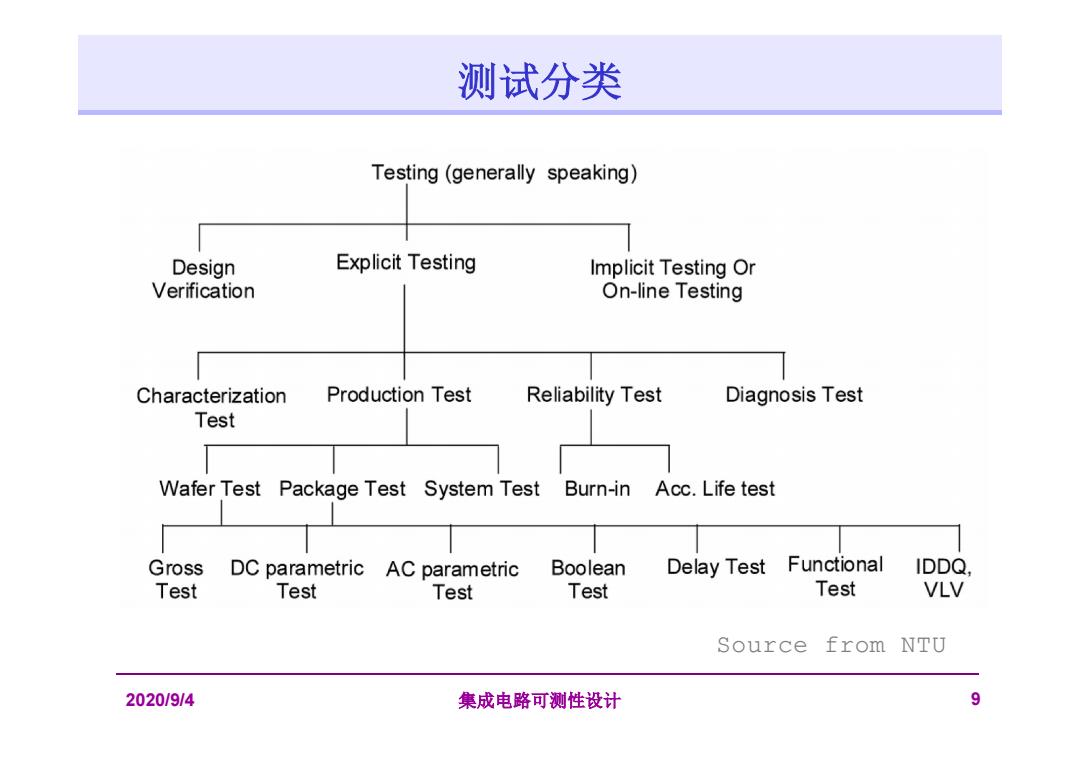

测试分类 Testing(generally speaking) Design Explicit Testing Implicit Testing Or Verification On-line Testing Characterization Production Test Reliability Test Diagnosis Test Test Wafer Test Package Test System Test Burn-in Acc.Life test Gross DC parametric AC parametric Boolean Delay Test Functional IDDQ. Test Test Test Test Test VLV Source from NTU 2020/9/4 集成电路可测性设计 9

2020/9/4 集成电路可测性设计 9 测试分类 Source from NTU

生产测试 目的:用以确定制造的产品是否达到设计参数要求, 也称为产品测试。 冬裸片测试(或探针测试)--中测 封装后测试。-一成测 2020/9/4 集成电路可测性设计 10

2020/9/4 集成电路可测性设计 10 生产测试 目的: 用以确定制造的产品是否达到设计参数要求, 也称为产品测试。 裸片测试(或探针测试)---中测 封装后测试。 ---成测

自动测试设备 ATE Advantest HP93000 Tester *Teradyne 750 Tester Mosaid Tester C200e ADVANT 2020/9/4 集成电路可测性设计 11

2020/9/4 集成电路可测性设计 11 自动测试设备(ATE) Advantest HP93000 Tester Teradyne 750 Tester Mosaid Tester