●● ●●●● ●● 第九章内建自测试(BST) 利用第八章“伪随机测试”的部分知识 2021/8/18 集成电路可测性设计 2

2021/8/18 集成电路可测性设计 2 第九章 内建自测试(BIST) 利用第八章“伪随机测试”的部分知识

●●● ●● ●●●● 本章要点 ●●●● ●●●● 。理解BIST的原理 。掌握LFSR的原理 ●掌握BIST的结构 2021/8/18 集成电路可测性设计 3

2021/8/18 集成电路可测性设计 3 本章要点 理解BIST的原理 掌握LFSR的原理 掌握BIST的结构

●●●● ●● ●●●● ●●●● ●●0● ●●o● ● 1、BST概述 2021/8/18 集成电路可测性设计 4

2021/8/18 集成电路可测性设计 4 1、BIST概述

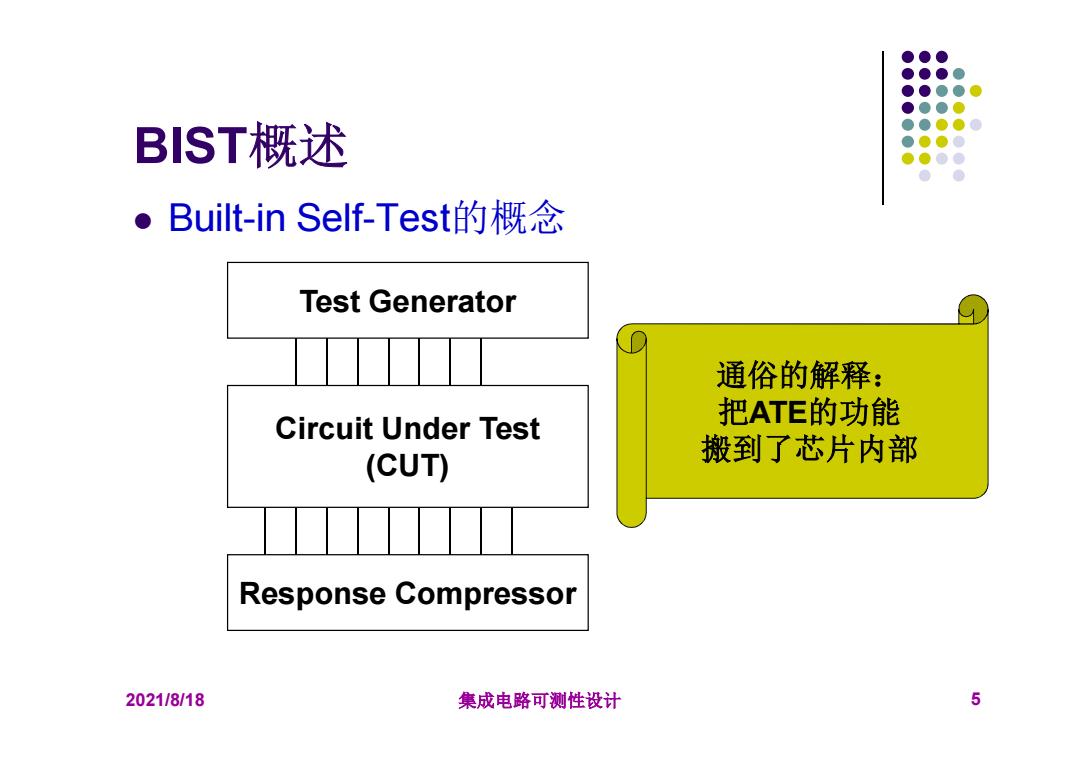

●●● ●● ● ●●0 BIST概述 ●●●● ●Built--in Self-.Test的概念 Test Generator 通俗的解释: Circuit Under Test 把ATE的功能 (CUT) 搬到了芯片内部 Response Compressor 2021/8/18 集成电路可测性设计 5

2021/8/18 集成电路可测性设计 5 BIST概述 Built-in Self-Test的概念 Test Generator Circuit Under Test (CUT) Response Compressor 通俗的解释: 把ATE的功能 搬到了芯片内部

●0 BIST的目标 ●● ●●@ Reduce input/output pin signal traffic. Permit easy circuit initialization and observation. Eliminate as much test pattern generation as possible. Achieve fair fault coverages on general class of failure mode. ●Reduce test time. Execute at-speed testing. Test circuit during burn-in. BIST Goal 2021/8/18 集成电路可测性设计 6

2021/8/18 集成电路可测性设计 6 BIST 的目标 Reduce input/output pin signal traffic. Permit easy circuit initialization and observation. Eliminate as much test pattern generation as possible. Achieve fair fault coverages on general class of failure mode. Reduce test time. Execute at-speed testing. Test circuit during burn-in. BIST Goal

●● ●0 ● ●● BIST的优点 ●●●● ● Can be used at all level of testing System level testing in field ●At speed testing ●No need for ATE Less 1/O pins needed for testing Burn-in Test made easy No need for test vector development 2021/8/18 集成电路可测性设计 7

2021/8/18 集成电路可测性设计 7 BIST的优点 Can be used at all level of testing System level testing in field At speed testing No need for ATE Less I/O pins needed for testing Burn-in Test made easy No need for test vector development

●● ● ●● BIST的缺点 ●●●● ●●●● .Area overhead -more susceptibility to manufacturing defects Performance penalties Designing and verifying proper operation of BIST at design level. Additional risk in project 2021/8/18 集成电路可测性设计 8

2021/8/18 集成电路可测性设计 8 BIST的缺点 Area overhead -more susceptibility to manufacturing defects Performance penalties Designing and verifying proper operation of BIST at design level. Additional risk in project

●● ●0 ● ●●0 BIST分类 ●●●● ●●●● 。通常分为 。LBIST ·Logic BIST-研究很深入,但是应用很少 ●MBIST 。Memory BIST--极大的应用 ·Syntest公司 本章重点 ·SRAM BIST ●Mentor公司 ·MBIST ● Synopsys公司 ▣?? 2021/8/18 集成电路可测性设计 9

2021/8/18 集成电路可测性设计 9 BIST分类 通常分为 LBIST Logic BIST---研究很深入,但是应用很少 MBIST Memory BIST---极大的应用 Syntest公司 SRAM BIST Mentor公司 MBIST Synopsys公司 ?? 本章重点

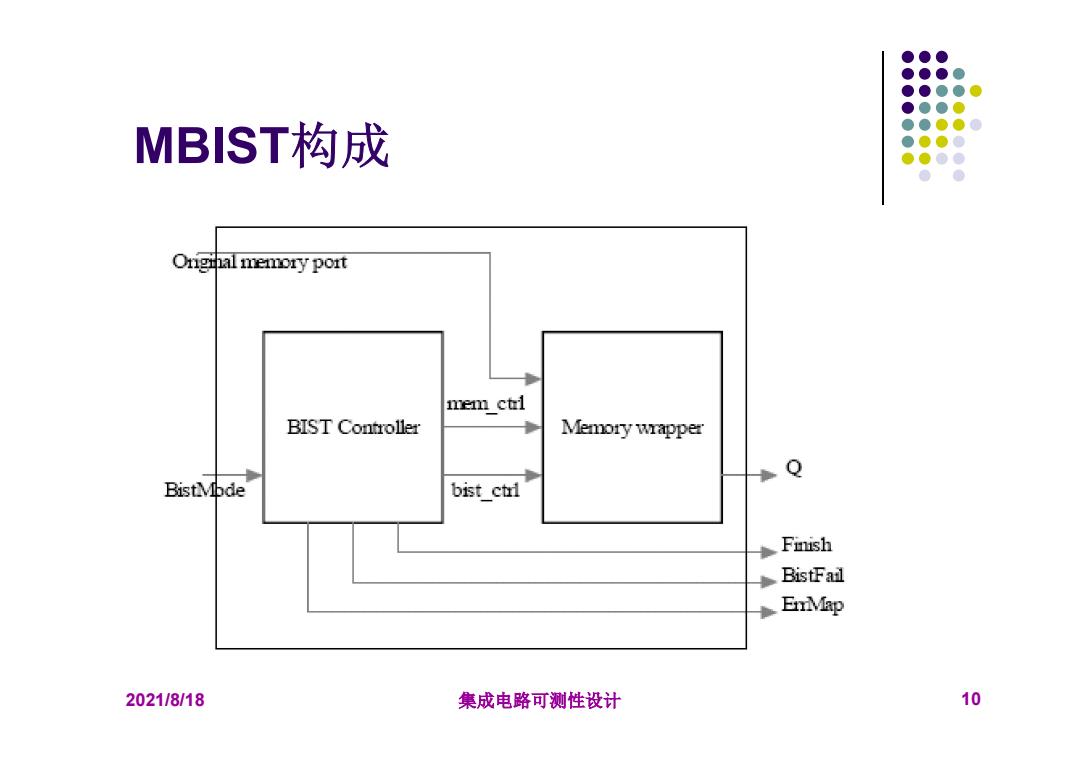

●● ●●● ●●●● ● ●●●●0 MBIST构成 ●●● ● ● Origihal memory port mem ctl BIST Controller Memory wrapper BistMbde bist ctrl Finish 渔 BistFail EnMap 2021/8/18 集成电路可测性设计 10

2021/8/18 集成电路可测性设计 10 MBIST构成

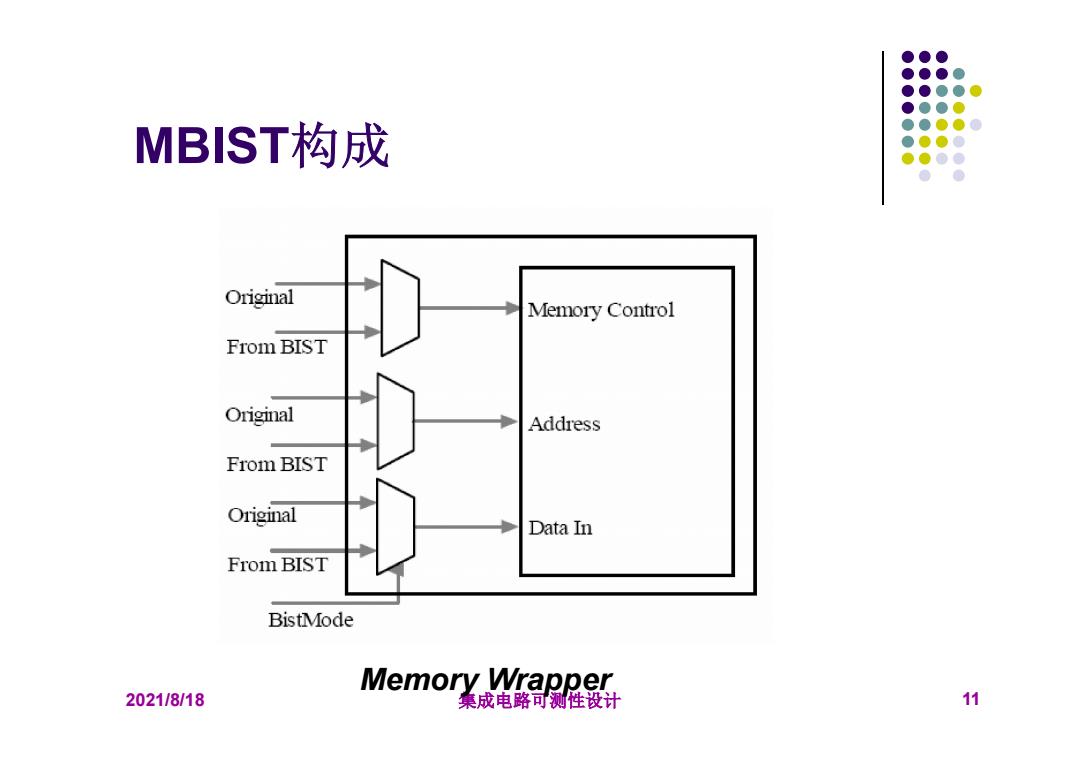

●● ●●● ●●●● ●● ●●●●0 MBIST构成 ●●●● ●●● ● Original Memory Control From BIST Original Address From BIST Original Data In From BIST BistMode Memory Wrapper 2021/8/18 集成电路可测性设计 11

2021/8/18 集成电路可测性设计 11 MBIST构成 Memory Wrapper