●●● 888 ●0 ● ● ●●d ●●●● 第十二章Soc测试 子件技女学 1966 University of Electronic Science and Technology of China

2021/8/18 2 第十二章 SoC测试

●●● ●●●0 ●● ●● ●●●● 本章重点 ●●●● ●●o● ·SoC设计的基本概念 。IEEE P1500协议 ·SoC的DFT策略的探讨 3

本章重点 SoC设计的基本概念 IEEE P1500协议 SoC的DFT策略的探讨 3

●●● 88880 ●●●● ●●0●0 ●●●● ●●0● ●● 12.1SoC的基本概念 2021/8/18 4

2021/8/18 4 12.1 SoC的基本概念

SoC设计的特点 ●● ●● ●设计方法从传统的电路设计转向系统设计。 ●● 。设计的重心从逻辑综合、布局布线转向系统的设计、软硬件协同 的设计以及仿真。 。大量使用了IP模块重用的方法。 SoC的设计多基于深亚微米(①SM)和超深亚微米级工艺(DSM),必 须将高层的设计和底层的版图设计紧密结合,作为整体来考虑。 SoC是非常复杂的系统,测试这样复杂的系统,需要使用结构化 和系统化的DFT(design-for-testa.bility)的方法。将测试方法 融入到设计的过程中,使设计和测试可以重复利用。 5

SoC设计的特点 设计方法从传统的电路设计转向系统设计。 设计的重心从逻辑综合、布局布线转向系统的设计、软硬件协同 的设计以及仿真。 大量使用了IP模块重用的方法。 SoC的设计多基于深亚微米(DSM)和超深亚微米级工艺(VDSM),必 须将高层的设计和底层的版图设计紧密结合,作为整体来考虑。 SoC是非常复杂的系统,测试这样复杂的系统,需要使用结构化 和系统化的DFT(design-for-testability)的方法。将测试方法 融入到设计的过程中,使设计和测试可以重复利用。 5

●● SOB→SOC→SIP ● ●● ●●●● ●●●● ● System on a Chip System on a board CPU ASIC SiP CPU memor CPU CPU ASIC ROM DSP SRAN 之 号 数开 无圾史清 图1不同功能器件集成到不同 图2.系统封装内不同功能 的封装内形威功能不同的模块 器件可以是20或0封装 6

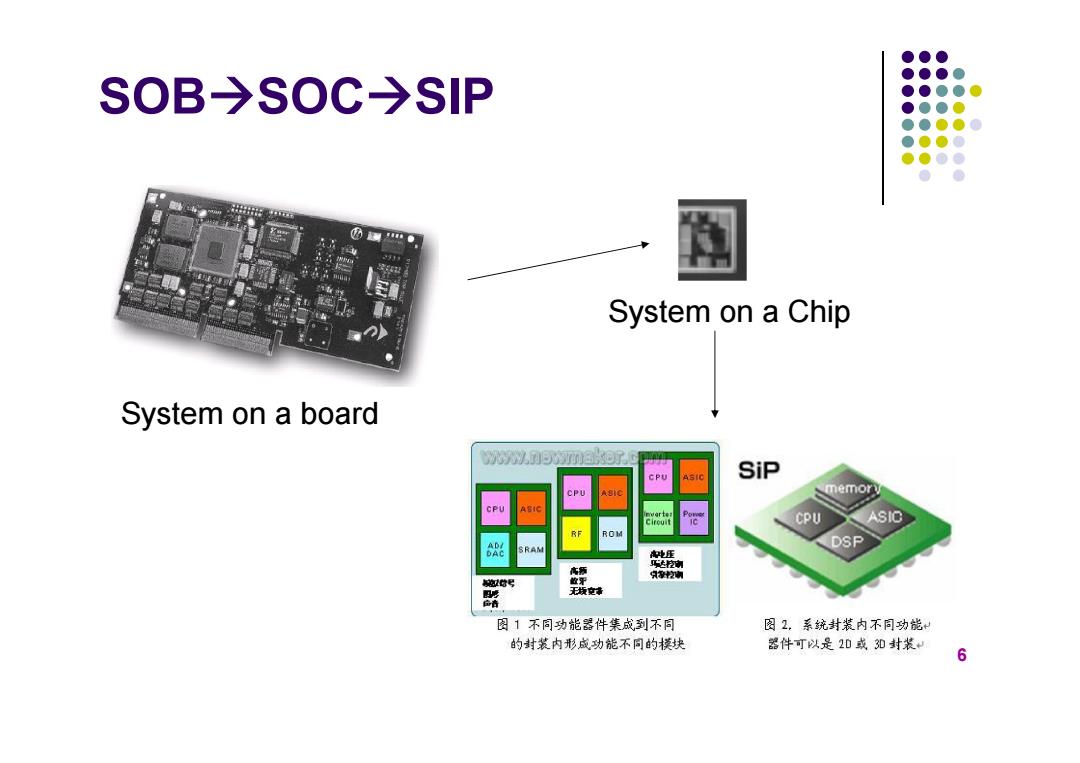

6 System on a board System on a Chip SOBSOCSIP

●● SOC软硬件协同设计流程 ●●●● ●●● ●0 ●●●●0 ●●●● ●●0● ● ● Design Architecture IP Library Specification Estimators Description Language L Hw/Sw Partitioning HW SW Verification VHDL,Verilog Synthesis Compiler Cosimulation Rapid design space exploration On-Chip Quality tool-kit generation Care Off-Chip Memory Design reuse nterface 7

7 SOC软硬件协同设计流程

●● ●●● 三种IP ● ●● ●●0 ●●0● ● Soft Resusability core portability flexibility Firm core Hard core Predictability,performance,time to market 8

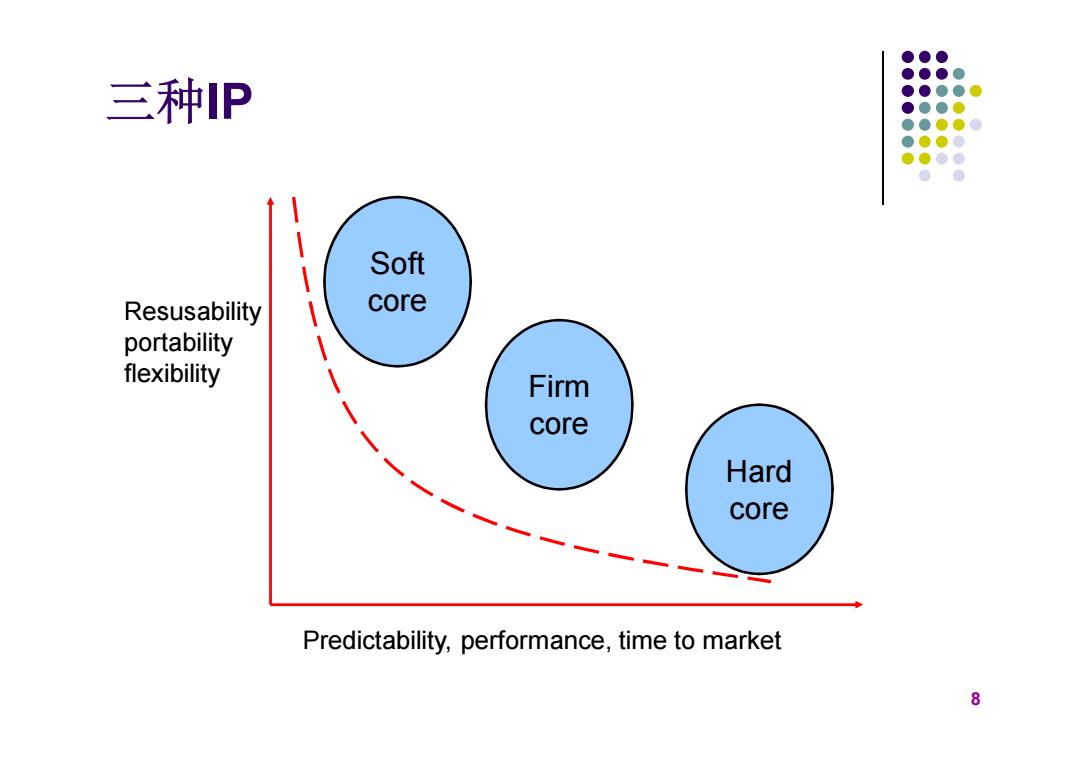

8 Resusability portability flexibility Predictability, performance, time to market Soft core Firm core Hard core 三种IP

●● ●●●● ●●●● 可复用核的分类 ●●● ●●●●0 ●●●● 类型 灵活性 设计流 表达 库 处理工 可携带性 程 艺 软核 非常灵 系统设 行为 无 无关 无限制 活 计 RTL 不可 RTL 测 固核 比较灵 版图 RTL, 参考 生成 库映射 活 布线 模块, 时间模 网表 型 硬核 不灵活 Routing Polygon 特定的 固定 过程映射 可预测 验证 数据 库和 设计 规律 9

9 可复用核的分类 类型 灵活性 设计流 程 表达 库 处理工 艺 可携带性 软核 非常灵 活 不可预 测 系统设 计 RTL 行为 RTL 无 无关 无限制 固核 比较灵 活 版图 布线 RTL, 模块, 网表 参考 时间模 型 生成 库映射 硬核 不灵活 可预测 Routing 验证 Polygon 数据 特定的 库和 设计 规律 固定 过程映射

SoC测试与板级系统测试的比较 ●0 ●● ●●● IC设计 IP设计 ●SoB(System on Board)的元件是制造好、经过测试的IC元件; S0C的元件是未经制造和测试的核,是虚拟元件; 森 IC验证 IP验证 ●SoB上的IC由生产厂生产、测试并提供测试方法; SoC上的核由集成商制造和测试: IC制造 ●SoB系统集成者认为IC是无故障的,其核心工作是用IC来 IC测试 设计和制造系统,只负责测试IC之间连接的缺陷: SoC系统集成者不但负责核之间互连逻辑和互连线的测试, 还特别要负责核的测试: ●IC之间的连接具有较好的可控性和可观性; SoB设计 SoC设计 P的内部及其连接间缺少直接的可控性和可观性。 SoB验证 SoC验证 SoC是基于核的设计,对其测试除了涉及到对每一 黍 SoB制造 SoC制造 个核的测试、UDL测试、核之间互连测试和SoC整体 测试外,还有测试策略的开发问题。因此,SoC的测 SoB测试 SoC测试 试比较独特,远比传统的ASIC测试复杂得多。 10

SoC测试与板级系统测试的比较 SoC设计 SoC验证 SoC制造 SoC测试 IP设计 IP验证 IC设计 IC验证 IC制造 IC测试 SoB设计 SoB验证 SoB制造 SoB测试 元件系统 SoB(System on Board)的元件是制造好、经过测试的IC元件; SoC的元件是未经制造和测试的核,是虚拟元件; SoB上的IC由生产厂生产、测试并提供测试方法; SoC上的核由集成商制造和测试; SoB系统集成者认为IC是无故障的,其核心工作是用IC来 设计和制造系统,只负责测试IC之间连接的缺陷; SoC系统集成者不但负责核之间互连逻辑和互连线的测试, 还特别要负责核的测试; IC之间的连接具有较好的可控性和可观性; IP的内部及其连接间缺少直接的可控性和可观性。 SoC是基于核的设计,对其测试除了涉及到对每一 个核的测试、UDL测试、核之间互连测试和SoC整体 测试外,还有测试策略的开发问题。因此,SoC的测 试比较独特,远比传统的ASIC测试复杂得多。 10

●●● ●●●● ●●●●0 ●●●● 一般SOC的结构 ●●●●0 ●●●● ●●0● ● PLL Memory Memory Specific Core UDL Block Inter face Micropro. A/D, DSP D/A 2021/8/18 11

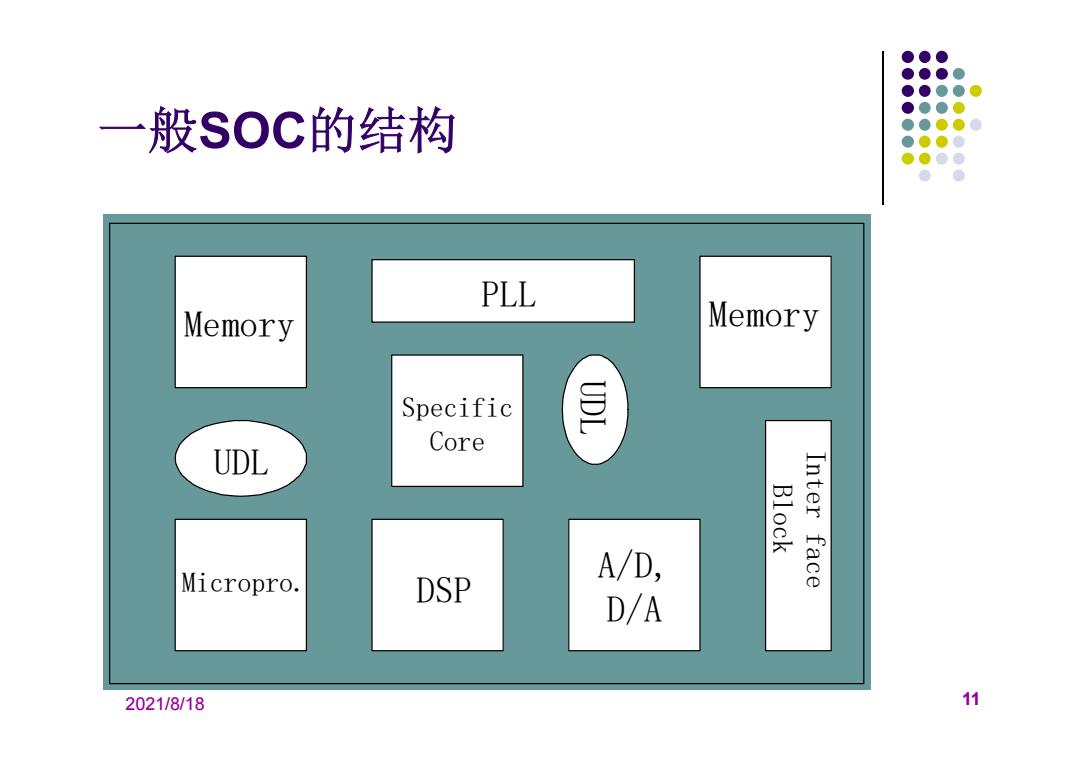

2021/8/18 11 一般SOC的结构 Memory Memory PLL UDL UDL Micropro. DSP A/D, D/A Inter face Block Specific Core