第三章验证、模拟和仿真 包子件皮女学 966 University of Electronic Science and Technology of China

第三章 验证、模拟和仿真

本章要点 。了解验证、模拟和仿真的含义 必理解验证、模拟和仿真的异同 冬学会建立test bench 冬掌握功能模拟的常用方法 。掌握故障模拟的常用方法 2020/9/4 集成电路可测性设计 3

2020/9/4 集成电路可测性设计 3 本章要点 了解验证、 模拟和仿真的含义 理解验证、 模拟和仿真的异同 学会建立test bench 掌握功能模拟的常用方法 掌握故障模拟的常用方法

3.1验证与模拟 包子种皮女学 1/966 University of Electronic Science and Technology of China

3.1 验证与模拟

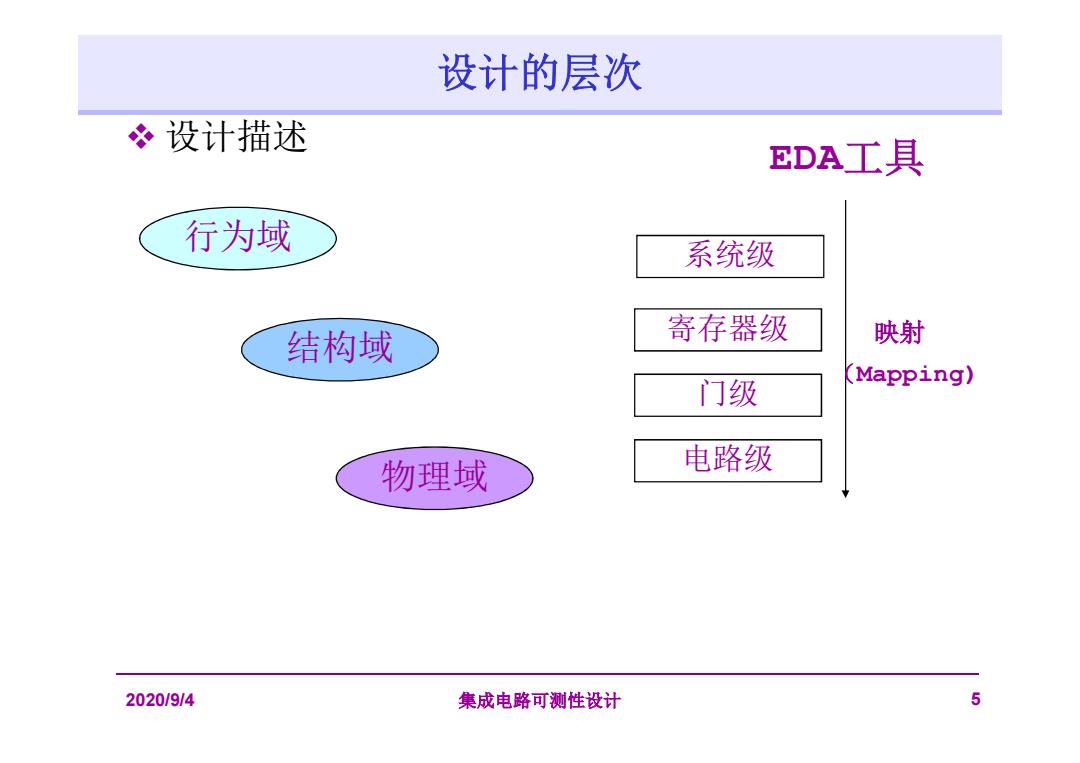

设计的层次 设计描述 EDA工具 行为域 系统级 结构域 寄存器级 映射 (Mapping) 门级 物理域 电路级 2020/9/4 集成电路可测性设计 5

2020/9/4 集成电路可测性设计 5 设计的层次 设计描述 系统级 寄存器级 门级 电路级 行为域 物理域 结构域 映射 (Mapping) EDA工具

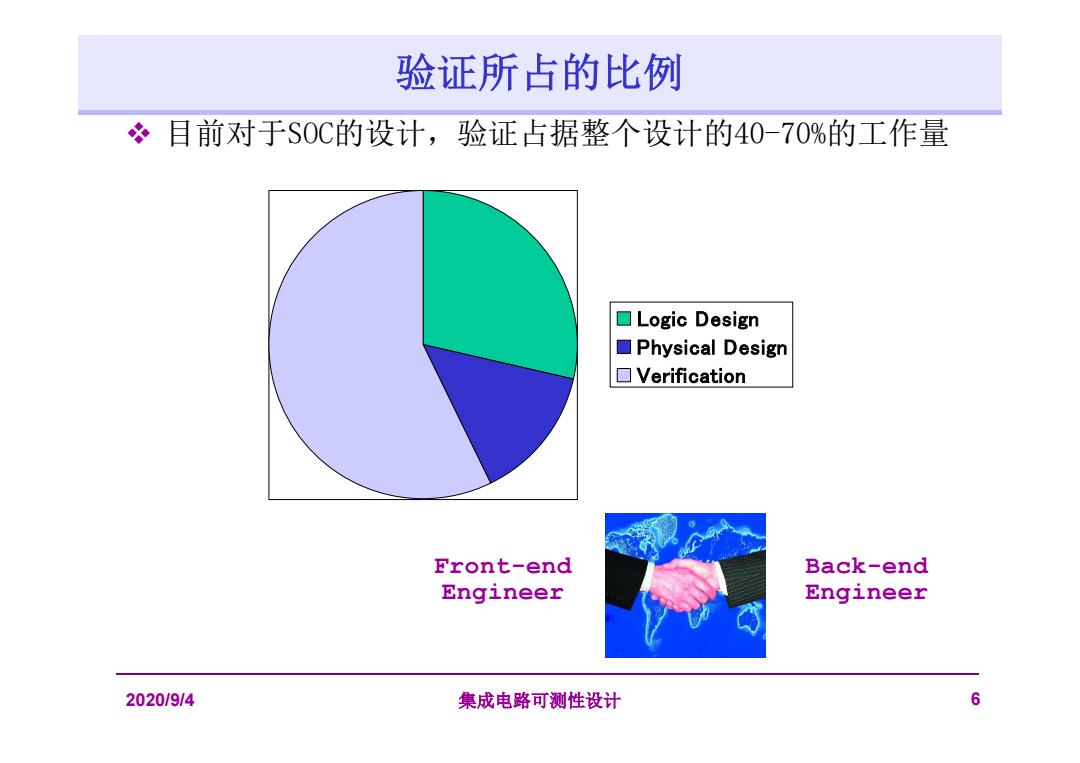

验证所占的比例 冬目前对于S0C的设计,验证占据整个设计的40-70%的工作量 ☐Logic Design ■Physical Design ☐Verification Front-end Back-end Engineer Engineer 2020/9/4 集成电路可测性设计 6

2020/9/4 集成电路可测性设计 6 验证所占的比例 目前对于SOC的设计,验证占据整个设计的40-70%的工作量 Logic Design Physical Design Verification Front-end Engineer Back-end Engineer

IC验证技术分类 Simulation lechnologies Logic simulation Event-based simulation Cycle-based simulation Transaction-based simulation -Code coverage Fault simulation HW/SW co-verification Technologies Emulation Rapid prototyping Hardware accelerator Static Verification Technologies -Lint checking (code inspection) Static Timing Analyze (STA) Formal Verification Technologies Physical Verification Technologies 2020/9/4 集成电路可测性设计 7

2020/9/4 集成电路可测性设计 7 IC验证技术分类 Simulation Technologies Logic simulation Event-based simulation Cycle-based simulation Transaction-based simulation Code coverage Fault simulation HW/SW co-verification Technologies Emulation Rapid prototyping Hardware accelerator Static Verification Technologies Lint checking (code inspection) Static Timing Analyze (STA) Formal Verification Technologies Physical Verification Technologies

两个概念的区分 Simulation vs Emulation Mentor PRODUCTS SOLUTIONS TRAINING SERVICES COMPANY BLOGS SUPPORT ⊙gCea Functional Verification Search Mentor.com Q Products Functional Venfication Customer stories STMicroelectronis:Simulation Emulation-Verification Success Veloce Emulation Platform STMicroelectronics:Simulation Emulation Verification X-STEP Success Questa Verification Solution In2012 STMicroelectronics Northwest Logic Analog/Mixed- began a pilot Signal Verification project to build lite.augmented Microsemi Corporation Clock-Domain what it called the Crossina Eagle Reference Cypress 2020/9/4 集成电路可测性设计 8

两个概念的区分 Simulation vs Emulation 2020/9/4 集成电路可测性设计 8

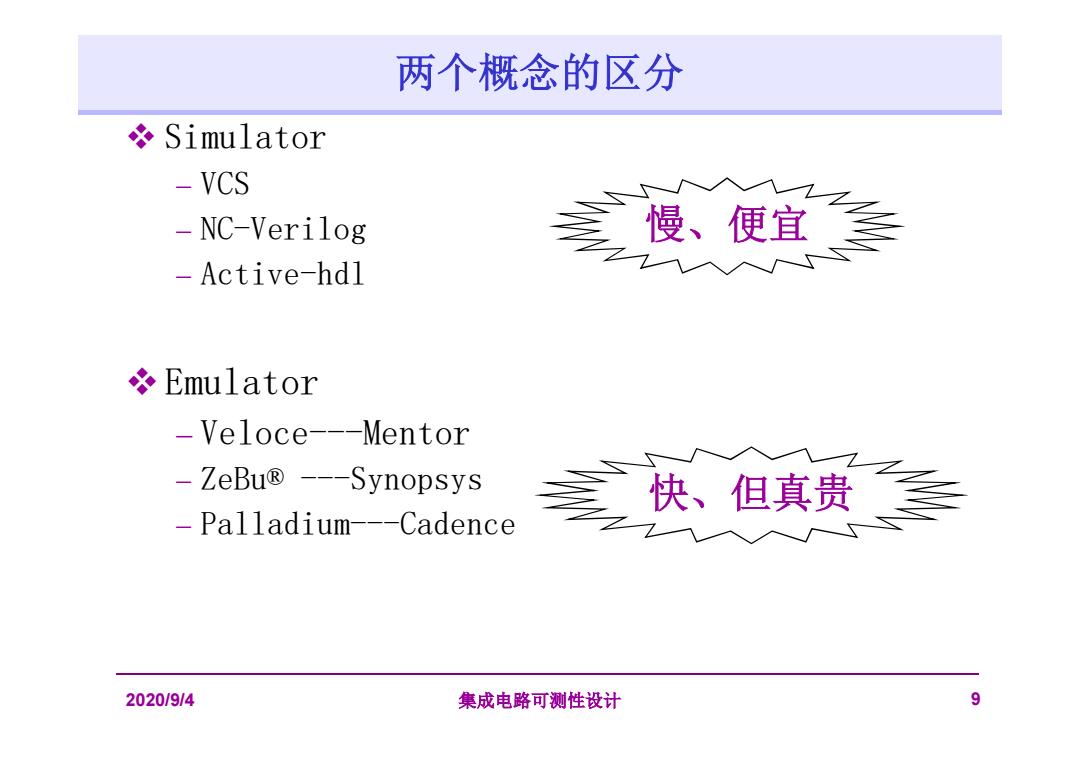

两个概念的区分 Simulator -VCS NC-Verilog 慢、便宜套 -Active-hdl Emulator -Veloce---Mentor -ZeBu®---Synopsys 快、但真贵 套 -Palladium---Cadence 2020/9/4 集成电路可测性设计 9

两个概念的区分 Simulator VCS NC-Verilog Active-hdl Emulator Veloce---Mentor ZeBu® ---Synopsys Palladium---Cadence 2020/9/4 集成电路可测性设计 9 慢、便宜 快、但真贵

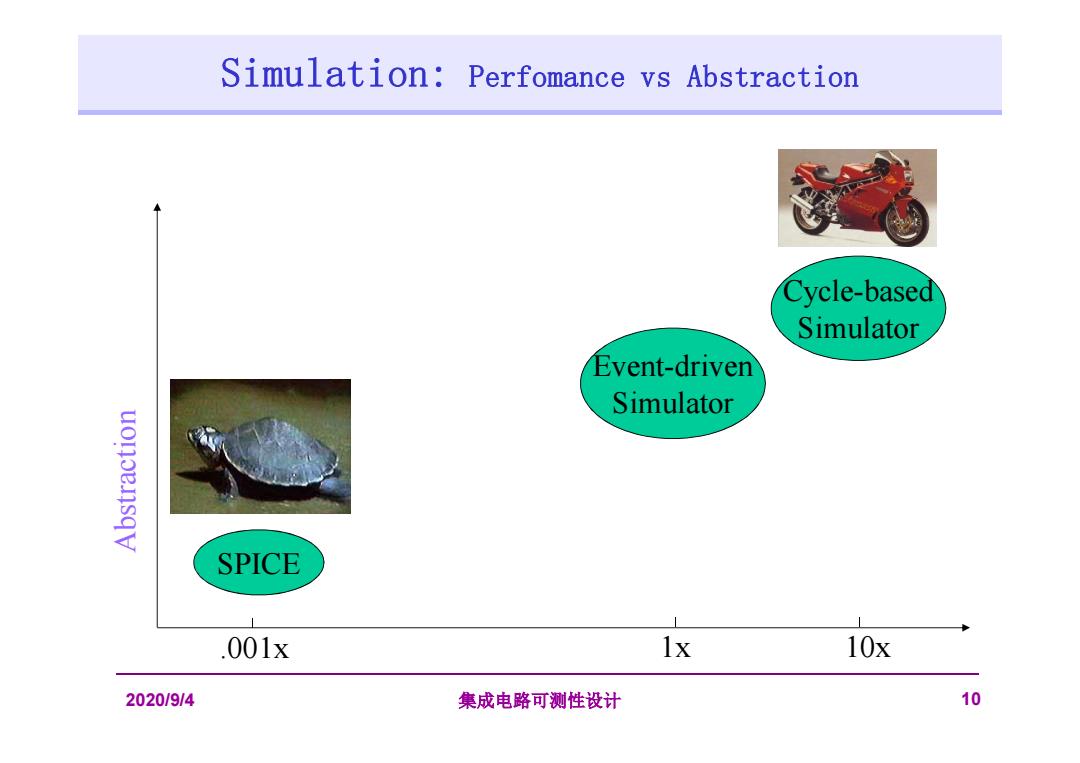

Simulation:Perfomance vs Abstraction Cycle-based Simulator Event-driven Simulator SPICE 001x 1x 10x 2020/9/4 集成电路可测性设计 10

2020/9/4 集成电路可测性设计 10 Simulation: Perfomance vs Abstraction .001x SPICE Event-driven Simulator Cycle-based Simulator 1x 10x Abstractio n

各种验证测试方法的比较 基于事件 基于时钟 硬件加 仿真 形式验 静态时 速器 证 间 功能 是 是 是 是 是 是 抽象级 行为、门、 门、RTL 门、 门、 门、 RTL RTL RTL RTL 门 功能等效 是 是 是 是 是 是 时间 是 否 是/否 否 否 是 容量 低 中 高 很高 高 中 运行时间 (10时钟 1K时钟 1K时钟 1M时钟 中 高 成本 低 中 中 高 中 低 2020/914 集成电路可测性设计 11

2020/9/4 集成电路可测性设计 11 各种验证测试方法的比较 基于事件 基于时钟 硬件加 速器 仿真 形式验 证 静态时 间 功能 是 是 是 是 是 是 抽象级 行为、门、 RTL 门、RTL 门、 RTL 门、 RTL 门、 RTL 门 功能等效 是 是 是 是 是 是 时间 是 否 是/否 否 否 是 容量 低 中 高 很高 高 中 运行时间 〈10时钟 1K时钟 1K时钟 1M时钟 中 高 成本 低 中 中 高 中 低