IEEE P1500 嵌入式核可测性标准

IEEE P1500 嵌入式核可测性标准

主要内容 一、EEEP1500嵌入式核可测性标准 二、SoC测试生成

主要内容 一、IEEE P1500嵌入式核可测性标准 二、SoC测试生成

第一部分 IEEE P1500 嵌入式核可测性标准

第一部分 IEEE P1500 嵌入式核可测性标准

SoC测试标准的核心问题 IEEP1500测弑标准核心问题是: 建立标准测试模型接口,使得嵌入式核和系统环境之间能进行 测试信息(包括嵌入式核本身的测试矢量)传递; ·制定测试界面的存取(access)與隔断(isolation)機制,使得测 試向量與程序可重用,並提供系統晶片間連線及DL的测試; 。设计一種可用來描述P1500的测試架搆與核心電路的测試描述語 言(Core Testlanguage-一CTL),期望能將符合IEEE P1500標 準的核以即插即用(plug-and-play)方式整合於SoC中。 满足这些要求就使得嵌入式核设计商和系统集成商之间能通过嵌 入式核测试语言描述的标准接口模型进行信息传递,使得测试可以 重用,既提高了测试的效率,也保护了嵌入式核提供商的知识产权 不受侵犯

SoC测试标准的核心问题 IEEE P1500 測試标准核心问题是: 建立标准测试模型接口,使得嵌入式核和系统环境之间能进行 测试信息(包括嵌入式核本身的测试矢量)传递; 制定测试界面的存取(access)與隔斷(isolation)機制,使得測 試向量與程序可重用,並提供系統晶片間連線及UDL的測試; 设计一種可用來描述P1500的測試架構與核心電路的測試描述語 言 (Core TestLanguage——CTL ),期望能將符合IEEE P1500標 準的核以即插即用(plug-and-play)方式整合於SoC中。 满足这些要求就使得嵌入式核设计商和系统集成商之间能通过嵌 入式核测试语言描述的标准接口模型进行信息传递,使得测试可以 重用,既提高了测试的效率,也保护了嵌入式核提供商的知识产权 不受侵犯

IEEE P1500测试标准的解决办法 IEEE P1500工作组提出的结构化的测试标准解决了: 如何通过SoC上的边界扫描机制访问嵌入式核上的边界扫描单 元 如何对每个单独的核进行测试; ● 如何进行核间连接的测试; ● 如何测试S0C上的其他模块,如存储器、用户定义逻辑模块 (UDL一user defined logic),以及模拟模块等; ● 如何在核的不同的模式(正常、核测试,其他模块测试、连接 测试和隔离等)之间进行切换。 主要内容包括:1)可变规模的可测性标准硬件结构: 2)测试描述语言CTL(Core Test Language)

IEEE P1500 测试标准的解决办法 IEEE P1500工作组提出的结构化的测试标准解决了: 如何通过SoC上的边界扫描机制访问嵌入式核上的边界扫描单 元; 如何对每个单独的核进行测试; 如何进行核间连接的测试; 如何测试SoC上的其他模块,如存储器、用户定义逻辑模块 (UDL——user defined logic ),以及模拟模块等; 如何在核的不同的模式(正常、核测试,其他模块测试、连接 测试和隔离等)之间进行切换。 主要内容包括:1)可变规模的可测性标准硬件结构; 2)测试描述语言CTL(Core Test Language)

参加制定P1500标准的公司 Advantest Nortel ASC Palmchip G2Startup.Com Philips HP Sisco Systems IBM ● Sonic Intellitech Synopsys LogicVision ti Mentor Graphics Veritable Motorola

参加制定P1500标准的公司 Nortel Palmchip Philips Sisco Systems Sonic Synopsys TI Veritable Advantest ASC G2Startup.Com HP IBM Intellitech LogicVision Mentor Graphics Motorola

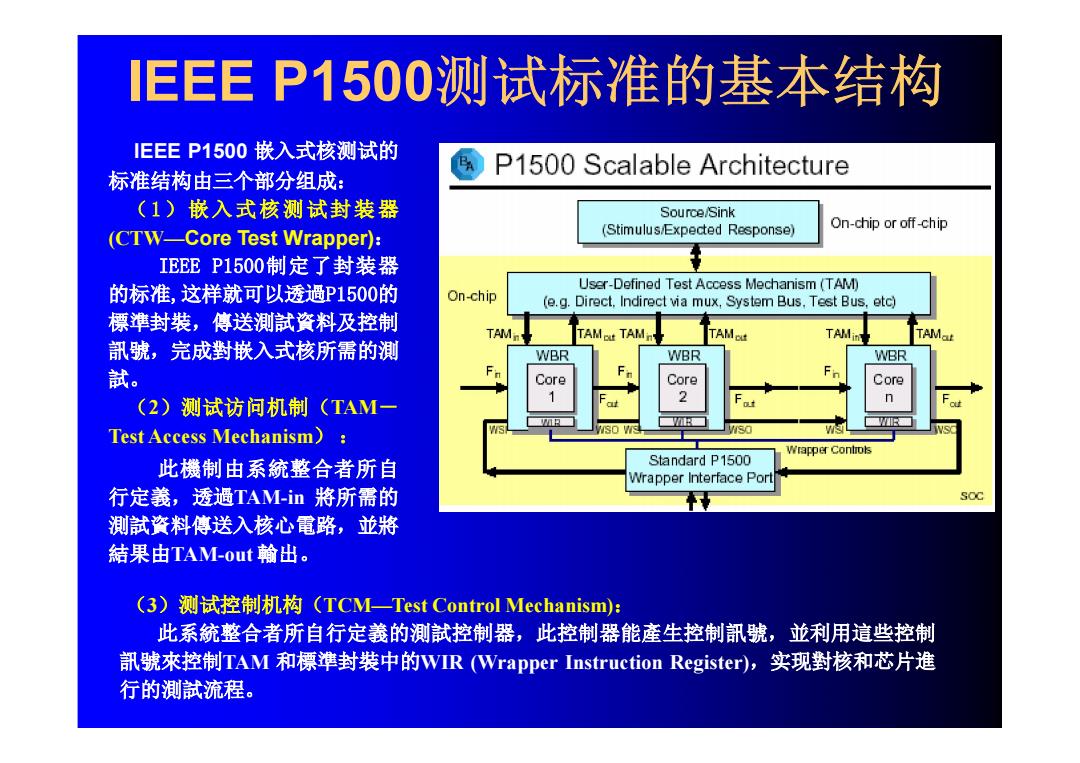

IEEE P1500测试标准的基本结构 IEEE P1500嵌入式核测试的 P1500 Scalable Architecture 标准结构由三个部分组成: (1)嵌入式核测试封装器 Source/Sink (Stimulus/Expected Response) On-chip or off-chip (CTW-Core Test Wrapper): IEEE P1500制定了封装器 的标准,这样就可以透過P1500的 User-Defined Test Access Mechanism (TAM) On-chip (e.g.Direct.Indirect via mux,System Bus.Test Bus,etc) 標準封装,停送测試资料及控制 TAM TAMTAM TAM 訊號,完成對嵌入式核所需的测 WBR WBR WBR 試。 Core Core Core 2 (2)测试访问机制(TAM一 n Test Access Mechanism): 301 此機制由系統整合者所自 Standard P1500 wrapper Interface Port 行定義,透過TAM-im将所需的 SOC 测試资料停送入核心電路,並將 結果由TAM-out輸出。 (3)测试控制机构(TCM一Test Control Mechanism): 此系統整合者所自行定義的测試控制器,此控制器能產生控制訊號,並利用這些控制 訊號來控制TAM和標準封装中的WIR(Wrapper Instruction Register),实现對核和芯片進 行的测試流程

IEEE P1500测试标准的基本结构 IEEE P1500 嵌入式核测试的 标准结构由三个部分组成: ( 1)嵌入式核测试封装器 (CTW—Core Test Wrapper): IEEE P1500制定了封装器 的标准,这样就可以透過P1500的 標準封裝,傳送測試資料及控制 訊號,完成對嵌入式核所需的測 試。 (2)测试访问机制(TAM- Test Access Mechanism) : 此機制由系統整合者所自 行定義,透過TAM-in 將所需的 測試資料傳送入核心電路,並將 結果由TAM-out 輸出。 (3)测试控制机构(TCM—Test Control Mechanism): 此系統整合者所自行定義的測試控制器,此控制器能產生控制訊號,並利用這些控制 訊號來控制TAM 和標準封裝中的WIR (Wrapper Instruction Register),实现對核和芯片進 行的測試流程

嵌入式核测试封装器结构 lesl sfm百 伊列 WPOX test resporses Core tuncticnal funcionel ore data data functional functional WBY Input data Output data 2c过C0iel test control ,8对5mh WS WIR WSO +8s1re9p0m683 Wrapper WIP 未封装的核 具有封装结构的封装核 封装器将整个核完全封闭起来,使之与外界隔离.通过封装器,嵌入式核可以同TAM连接 起来,并可将核设置为正常模式、测试模式或其他模式: WBR(Wrapper Boundary Register):边界寄存器; WIR(Wrapper Instruction Register):指令寄存器: BY(Wrapper Bypass Register):旁路寄存器; WSI/SO(Wrapper Serial Input/,0 utput):串行输入/输出接口; PI/PO(rapper Parallel Input/,Output):并行输入/并出接口(可选); WIP(Wrapper Interface Port):封装器接口

嵌入式核测试封装器结构 封装器将整个核完全封闭起来,使之与外界隔离.通过封装器,嵌入式核可以同TAM连接 起来,并可将核设置为正常模式、测试模式或其他模式; WBR(Wrapper Boundary Register):边界寄存器; WIR(Wrapper Instruction Register):指令寄存器; WBY(Wrapper Bypass Register):旁路寄存器; WSI/WSO(Wrapper Serial Input/Output):串行输入/输出接口; WPI/WPO(Wrapper Parallel Input/Output):并行输入/并出接口(可选); WIP(Wrapper Interface Port):封装器接口。 未封装的核 具有封装结构的封装核 functional Input data functional Output data

嵌入式核测试封装器的接口端 User Defined Port Optional Wrapper for Test Flexibility Parallel Control Parallel Port (WPP) WPC Wrapper Wrapper Parallel Inpunt Parallel Outputi WPI WPO Core WSI Wrapper WSO Wrapper Wrapper Serial Input Serial Output i WSC Required Wrapper/ Wrapper Standardized Port Serial Port (WSP) Serial Control for Plug Play

嵌入式核测试封装器的接口端

WBR边界扫描寄存器 Col TastOutput TAM. CTO □w作apper Cells CORE CORE CFI goundary Scan Cell ·CFO Cell Functional Output Control CTI Cell Tos rput 边界扫描寄存器WBR 边界扫描单元BSC示意图 BSC的连接方式 WBR由串行连接的边界扫描单元BSCs)组成; 核的每一个输入/输出端口都有一个BSC,但TAM端口和模拟端口可以不设置BSC; 只定义了两种类型的BSC:输入BSC和输出BSC,BSC可置为高阻状态; IEEE P1500不支持双向端口,因此没有定义双向BSC

WBR边界扫描寄存器 核的每一个输入/输出端口都有一个BSC,但TAM端口和模拟端口可以不设置BSC ; 只定义了两种类型的BSC:输入BSC和输出BSC,BSC可置为高阻状态; IEEE P1500不支持双向端口,因此没有定义双向BSC. 边界扫描寄存器WBR 边界扫描单元BSC示意图 BSC的连接方式 WBR由串行连接的边界扫描单元(BSCs)组成;