正在加载图片...

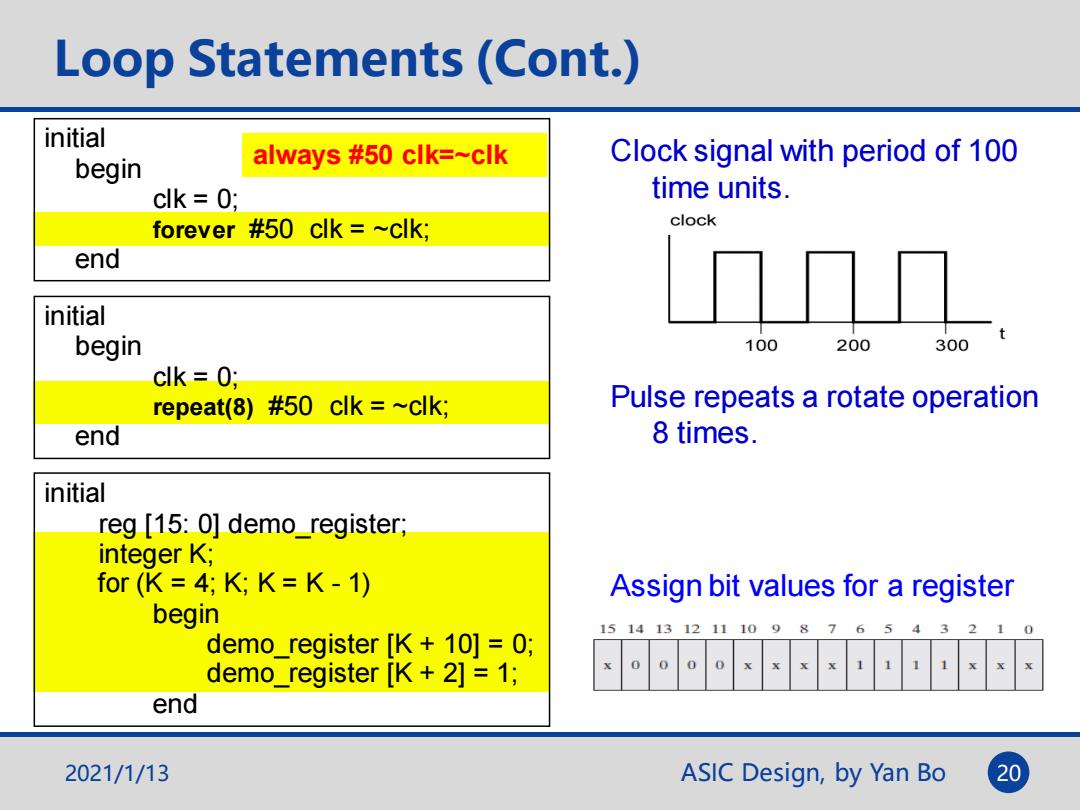

Loop Statements(Cont.) initial begin always #50 clk=~clk Clock signal with period of 100 clk 0; time units. forever #50 clk=~clk; clock end initial begin 100 200 300 clk 0; repeat(8)#50 clk =~clk; Pulse repeats a rotate operation end 8 times. initial reg [15:0]demo_register; integer K; for (K=4;K;K=K-1) Assign bit values for a register begin 1514131211109 8 demo_register [K+10]0; demo_register [K+2]=1; 0 end 2021/1/13 ASIC Design,by Yan Bo 20ASIC Design, by Yan Bo initial reg [15: 0] demo_register; integer K; for (K = 4; K; K = K - 1) begin demo_register [K + 10] = 0; demo_register [K + 2] = 1; end Loop Statements (Cont.) Clock signal with period of 100 time units. Pulse repeats a rotate operation 8 times. initial begin clk = 0; forever #50 clk = ~clk; end initial begin clk = 0; repeat(8) #50 clk = ~clk; end Assign bit values for a register 2021/1/13 20 always #50 clk=~clk