正在加载图片...

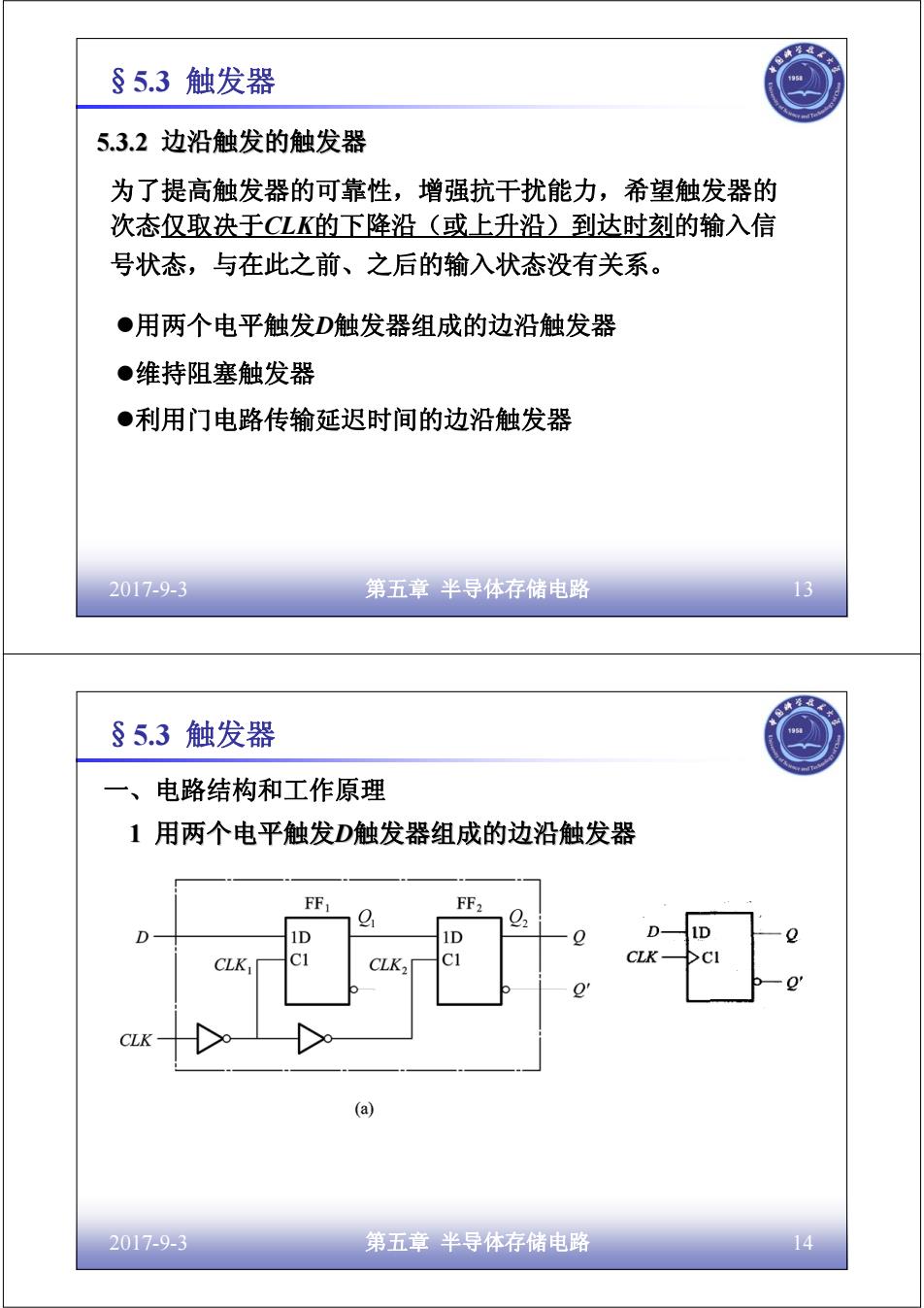

§5.3 触发器 5.3.2边沿触发的触发器 为了提高触发器的可靠性,增强抗干扰能力,希望触发器的 次态仅取决于CLK的下隆沿(或上升沿)到达时刻的输入信 号状态,与在此之前、之后的输入状态没有关系。 ●用两个电平触发D触发器组成的边沿触发器 ●维持阻塞触发器 ●利用门电路传输延迟时间的边沿触发器 2017-9-3 第五章半导体存储电路 §5.3 触发器 一、电路结构和工作原理 1用两个电平触发D触发器组成的边沿触发器 FF, FF2 0 1D 1D ID CLK. CLK2 CLK- >C1 CLK (a) 2017-9-3 第五章半导体存储电路 142017-9-3 第五章 半导体存储电路 13 为了提高触发器的可靠性,增强抗干扰能力,希望触发器的 次态仅取决于CLK的下降沿(或上升沿)到达时刻的输入信 号状态,与在此之前、之后的输入状态没有关系。 z用两个电平触发D触发器组成的边沿触发器 z维持阻塞触发器 z利用门电路传输延迟时间的边沿触发器 §5.3 触发器 5.3.2 边沿触发的触发器 2017-9-3 第五章 半导体存储电路 14 1 用两个电平触发D触发器组成的边沿触发器 一、电路结构和工作原理 Q1 1 Q1 2 §5.3 触发器