正在加载图片...

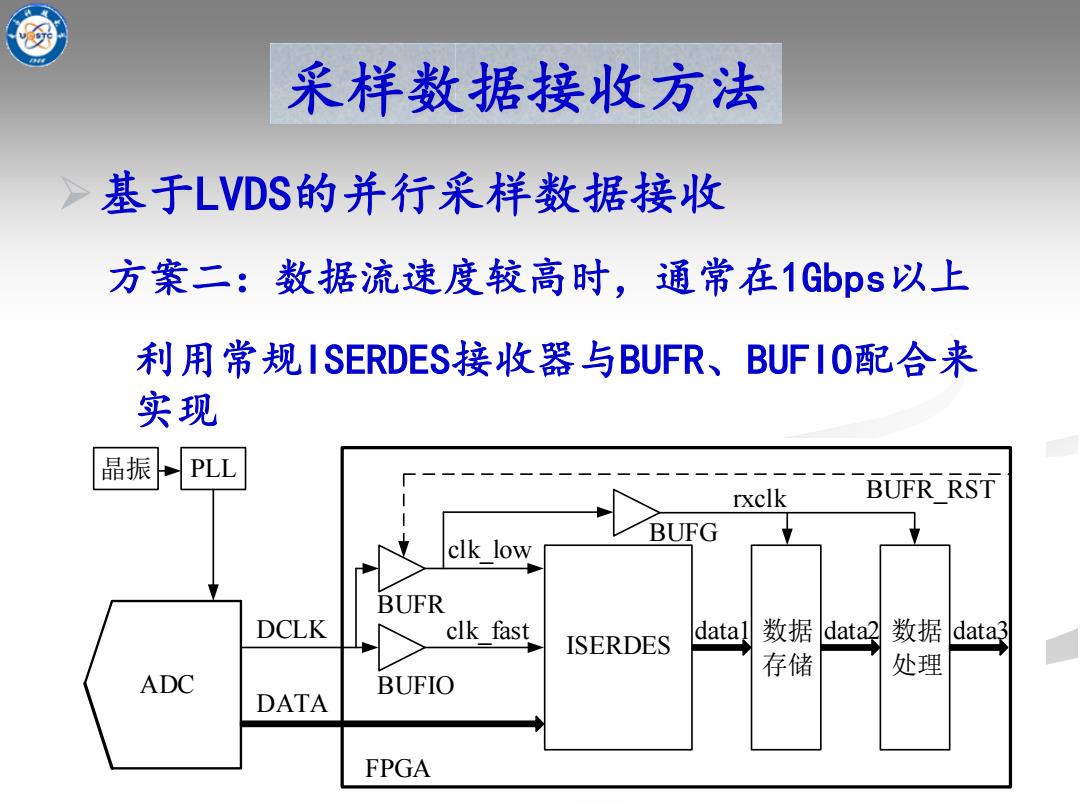

采样数据接收方法 >基于LVDS的并行采样数据接收 方案二:数据流速度较高时,通常在1Gbps以上 利用常规I SERDES接收器与BUFR、BUFI0配合来 实现 晶振 PLL rxclk BUFR RST BUFG clk low BUFR DCLK clk fast ISERDES datal 数据data2 数据data3 存储 处理 ADC BUFIO DATA FPGA第8页 基于LVDS的并行采样数据接收 采样数据接收方法 方案二:数据流速度较高时,通常在1Gbps以上 利用常规ISERDES接收器与BUFR、BUFIO配合来 实现 ADC DCLK DATA BUFR FPGA BUFIO clk_fast clk_low ISERDES BUFR_RST data1 数据 存储 data2 数据 处理 BUFG rxclk 晶振 PLL data3