正在加载图片...

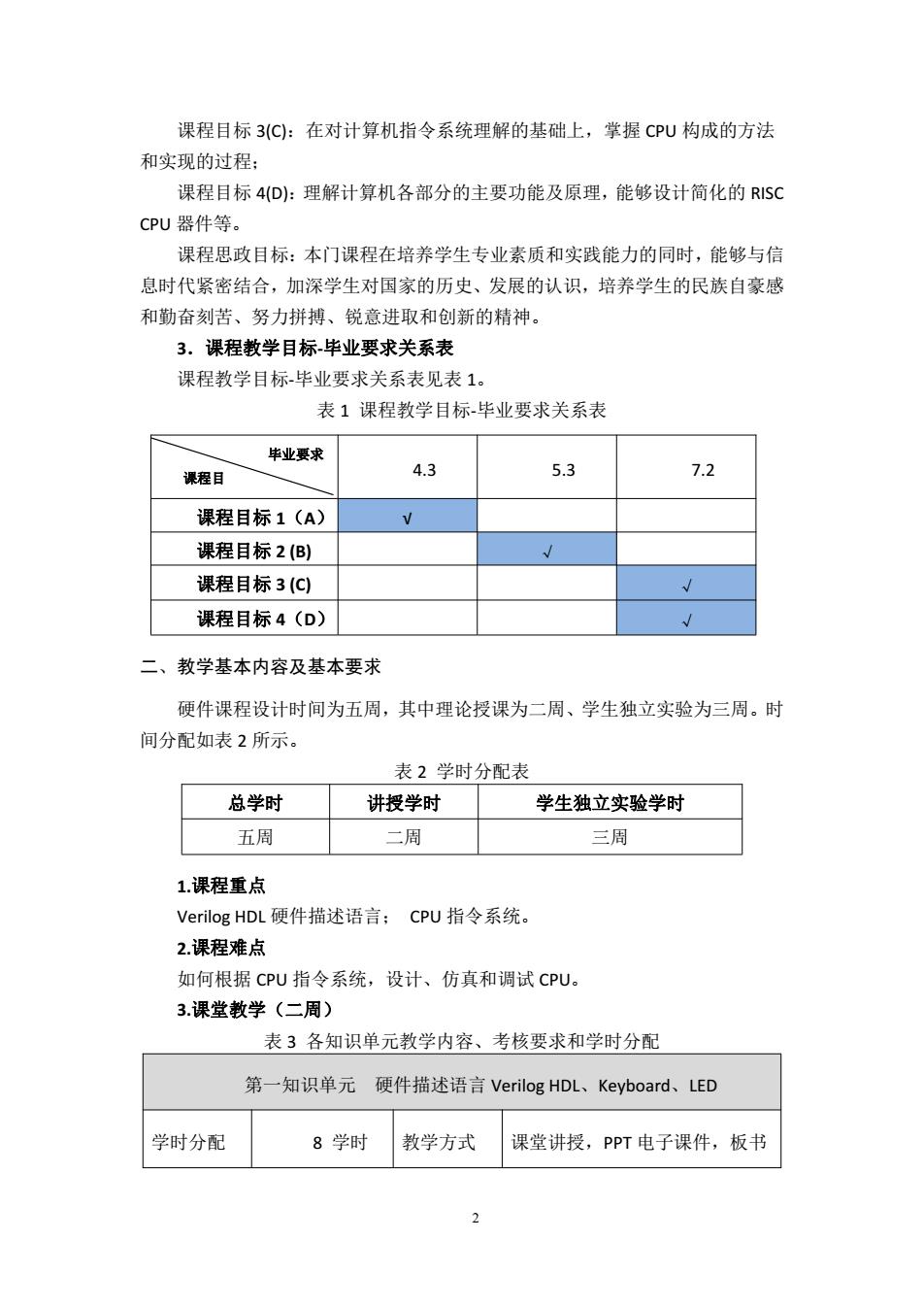

课程目标3(C:在对计算机指令系统理解的基础上,掌握CU构成的方法 和实现的过程: 课程目标4(D):理解计算机各部分的主要功能及原理,能够设计简化的RSC CPU器件等。 课程思政目标:本门课程在培养学生专业素质和实践能力的同时,能够与信 息时代紧密结合,加深学生对国家的历史、发展的认识,培养学生的民族自豪感 和勤奋刻苦、努力拼搏、锐意进取和创新的精神。 3.课程教学目标毕业要求关系表 课程教学目标毕业要求关系表见表1。 表1课程教学目标毕业要求关系表 毕业要求 课程目 4.3 5.3 7.2 课程目标1(A) 课程目标2(B) 课程目标3(C) 课程目标4(D) 二、教学基本内容及基本要求 硬件课程设计时间为五周,其中理论授课为二周、学生独立实验为三周。时 间分配如表2所示。 表2学时分配表 总学时 讲授学时 学生独立实验学时 五周 二周 三周 1.课程重点 Verilog HDL硬件描述语言:CPU指令系统 2.课程难点 如何根据CPU指令系统,设计、仿真和调试CPU。 3课堂教学(二周) 表3各知识单元教学内容、考核要求和学时分配 第一知识单元硬件描述语言Verilog HDL、Keyboard、LED 学时分配 8学时 教学方式 课堂讲授,PPT电子课件,板书2 课程目标 3(C):在对计算机指令系统理解的基础上,掌握 CPU 构成的方法 和实现的过程; 课程目标 4(D):理解计算机各部分的主要功能及原理,能够设计简化的 RISC CPU 器件等。 课程思政目标:本门课程在培养学生专业素质和实践能力的同时,能够与信 息时代紧密结合,加深学生对国家的历史、发展的认识,培养学生的民族自豪感 和勤奋刻苦、努力拼搏、锐意进取和创新的精神。 3.课程教学目标-毕业要求关系表 课程教学目标-毕业要求关系表见表 1。 表 1 课程教学目标-毕业要求关系表 4.3 5.3 7.2 课程目标 1(A) √ 课程目标 2 (B) √ 课程目标 3 (C) √ 课程目标 4(D) √ 二、教学基本内容及基本要求 硬件课程设计时间为五周,其中理论授课为二周、学生独立实验为三周。时 间分配如表 2 所示。 表 2 学时分配表 总学时 讲授学时 学生独立实验学时 五周 二周 三周 1.课程重点 Verilog HDL 硬件描述语言; CPU 指令系统。 2.课程难点 如何根据 CPU 指令系统,设计、仿真和调试 CPU。 3.课堂教学(二周) 表 3 各知识单元教学内容、考核要求和学时分配 第一知识单元 硬件描述语言 Verilog HDL、Keyboard、LED 学时分配 8 学时 教学方式 课堂讲授,PPT 电子课件,板书 毕业要求 课程目 标