课程名称:硬件课程设计 课程编码:7263511 课程学分:5学分 课程学时:5周 适用专业:计算机科学与技术 先修课程:数字逻辑,计算机组成原理 课程类别:专业必修课 《硬件课程设计》 教学大纲 一、课程简介与目标 本课程为计算机专业必修课程,授课对象为计算机科学与技术专业本科生, 硬件课程设计是计算机科学与技术专业重要的实践环节。该课程讲授硬件描述语 言的综合知识和如何用硬件描述语言开发专用集成电路两大部分。同时为34年 级“接口与通信技术”和“计算机体系结构”的学习打下基础。通过学习和实 践,深刻领会硬件描述语言,掌握硬件描述语言的模块设计方法,能够运用硬件 描述语言的3种描述方式,熟练进行数字系统设计和仿真及实现,熟练设计简化 的RISC CPU器件等。 1课程支撑的毕业要求 4.3能够对计算机专业复杂工程问题进行研究实践,并能够针对实施的研究 过程或实验结果进行定性或定量分析,综合各种信息数据得到有效结论,并能对 结论进行合理解释。 5.3能够在计算机复杂工程问题中,开发、选择与使用恰当的技术、资源与 工具,对系统进行预测、模拟、开发和实现,并能够理解其局限性。 7.2能够分析与评价计算机系统开发、应用以及更新对环境和可持续发展影 响。并能够在计算系统开发、运行、更新换代中考虑利用技术手段降低对环境及 社会持续发展的负面作用。 2课程拟达到的敦学目标 本课程主要围绕用硬件描述语言设计硬件模块而展开,课程目标为: 课程目标1(A:掌握硬件描述语言: 课程目标2(B):掌握硬件描述语言的模块设计方法,能够运用硬件描述语言 的3种描述方式熟练进行数字系统设计和仿真及实现:

1 课程名称:硬件课程设计 课程编码:7263511 课程学分:5 学分 课程学时:5 周 适用专业:计算机科学与技术 先修课程:数字逻辑, 计算机组成原理 课程类别:专业必修课 《硬件课程设计》 教学大纲 一、课程简介与目标 本课程为计算机专业必修课程,授课对象为计算机科学与技术专业本科生, 硬件课程设计是计算机科学与技术专业重要的实践环节。该课程讲授硬件描述语 言的综合知识和如何用硬件描述语言开发专用集成电路两大部分。同时为 3-4 年 级“接口与通信技术” 和“计算机体系结构”的学习打下基础。通过学习和实 践,深刻领会硬件描述语言,掌握硬件描述语言的模块设计方法,能够运用硬件 描述语言的 3 种描述方式,熟练进行数字系统设计和仿真及实现,熟练设计简化 的 RISC CPU 器件等。 1 课程支撑的毕业要求 4.3 能够对计算机专业复杂工程问题进行研究实践,并能够针对实施的研究 过程或实验结果进行定性或定量分析,综合各种信息数据得到有效结论,并能对 结论进行合理解释。 5.3 能够在计算机复杂工程问题中,开发、选择与使用恰当的技术、资源与 工具,对系统进行预测、模拟、开发和实现,并能够理解其局限性。 7.2 能够分析与评价计算机系统开发、应用以及更新对环境和可持续发展影 响。并能够在计算系统开发、运行、更新换代中考虑利用技术手段降低对环境及 社会持续发展的负面作用。 2.课程拟达到的教学目标 本课程主要围绕用硬件描述语言设计硬件模块而展开,课程目标为: 课程目标 1(A):掌握硬件描述语言; 课程目标 2(B):掌握硬件描述语言的模块设计方法,能够运用硬件描述语言 的 3 种描述方式熟练进行数字系统设计和仿真及实现;

课程目标3(C:在对计算机指令系统理解的基础上,掌握CU构成的方法 和实现的过程: 课程目标4(D):理解计算机各部分的主要功能及原理,能够设计简化的RSC CPU器件等。 课程思政目标:本门课程在培养学生专业素质和实践能力的同时,能够与信 息时代紧密结合,加深学生对国家的历史、发展的认识,培养学生的民族自豪感 和勤奋刻苦、努力拼搏、锐意进取和创新的精神。 3.课程教学目标毕业要求关系表 课程教学目标毕业要求关系表见表1。 表1课程教学目标毕业要求关系表 毕业要求 课程目 4.3 5.3 7.2 课程目标1(A) 课程目标2(B) 课程目标3(C) 课程目标4(D) 二、教学基本内容及基本要求 硬件课程设计时间为五周,其中理论授课为二周、学生独立实验为三周。时 间分配如表2所示。 表2学时分配表 总学时 讲授学时 学生独立实验学时 五周 二周 三周 1.课程重点 Verilog HDL硬件描述语言:CPU指令系统 2.课程难点 如何根据CPU指令系统,设计、仿真和调试CPU。 3课堂教学(二周) 表3各知识单元教学内容、考核要求和学时分配 第一知识单元硬件描述语言Verilog HDL、Keyboard、LED 学时分配 8学时 教学方式 课堂讲授,PPT电子课件,板书

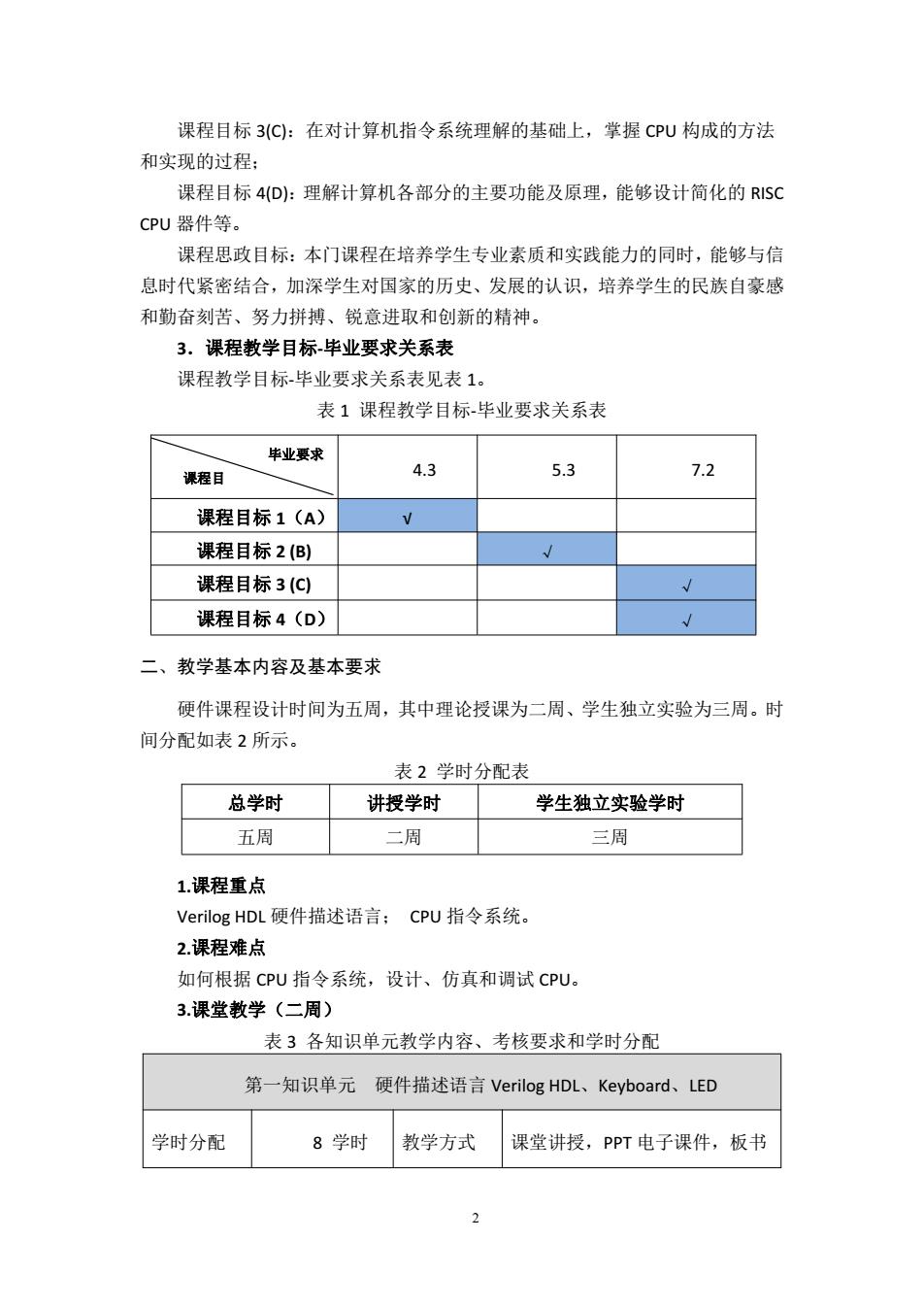

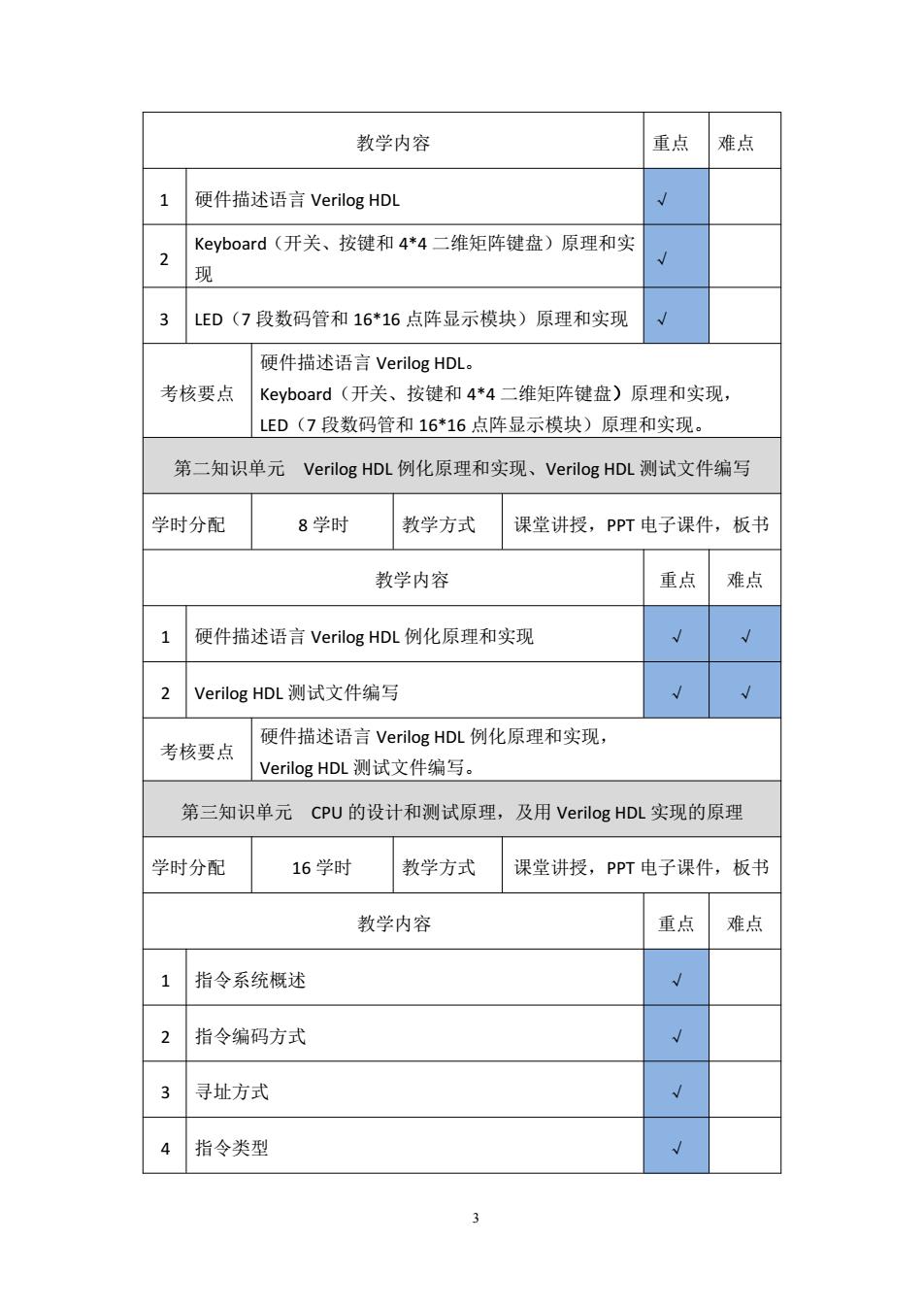

2 课程目标 3(C):在对计算机指令系统理解的基础上,掌握 CPU 构成的方法 和实现的过程; 课程目标 4(D):理解计算机各部分的主要功能及原理,能够设计简化的 RISC CPU 器件等。 课程思政目标:本门课程在培养学生专业素质和实践能力的同时,能够与信 息时代紧密结合,加深学生对国家的历史、发展的认识,培养学生的民族自豪感 和勤奋刻苦、努力拼搏、锐意进取和创新的精神。 3.课程教学目标-毕业要求关系表 课程教学目标-毕业要求关系表见表 1。 表 1 课程教学目标-毕业要求关系表 4.3 5.3 7.2 课程目标 1(A) √ 课程目标 2 (B) √ 课程目标 3 (C) √ 课程目标 4(D) √ 二、教学基本内容及基本要求 硬件课程设计时间为五周,其中理论授课为二周、学生独立实验为三周。时 间分配如表 2 所示。 表 2 学时分配表 总学时 讲授学时 学生独立实验学时 五周 二周 三周 1.课程重点 Verilog HDL 硬件描述语言; CPU 指令系统。 2.课程难点 如何根据 CPU 指令系统,设计、仿真和调试 CPU。 3.课堂教学(二周) 表 3 各知识单元教学内容、考核要求和学时分配 第一知识单元 硬件描述语言 Verilog HDL、Keyboard、LED 学时分配 8 学时 教学方式 课堂讲授,PPT 电子课件,板书 毕业要求 课程目 标

教学内容 重点难点 1 硬件描述语言Verilog HDL Keyboard(开关、按键和4*4二维矩阵键盘)原理和实 2 现 3 ED(7段数码管和16*16点阵显示模块)原理和实现 硬件描述语言Verilog HDL。. 考核要点 Keyboard(开关、按键和4*4二维矩阵键盘)原理和实现, LED(7段数码管和16*16点阵显示模块)原理和实现。 第二知识单元Verilog HDL例化原理和实现、Verilog HDL测试文件编写 学时分配 8学时 教学方式 课堂讲授,PPT电子课件,板书 教学内容 重点难点 1硬件描述语言Verilog HDL例化原理和实现 2 Verilog HDL测试文件编写 √ 硬件描述语言Verilog HDL例化原理和实现, 考核要点 Verilog HDL测试文件编写。 第三知识单元CpU的设计和测试原理,及用Verilog HDL实现的原理 学时分配 16学时 教学方式 课堂讲授,PPT电子课件,板书 教学内容 重点难点 1指令系统概述 2指令编码方式 寻址方式 4指令类型

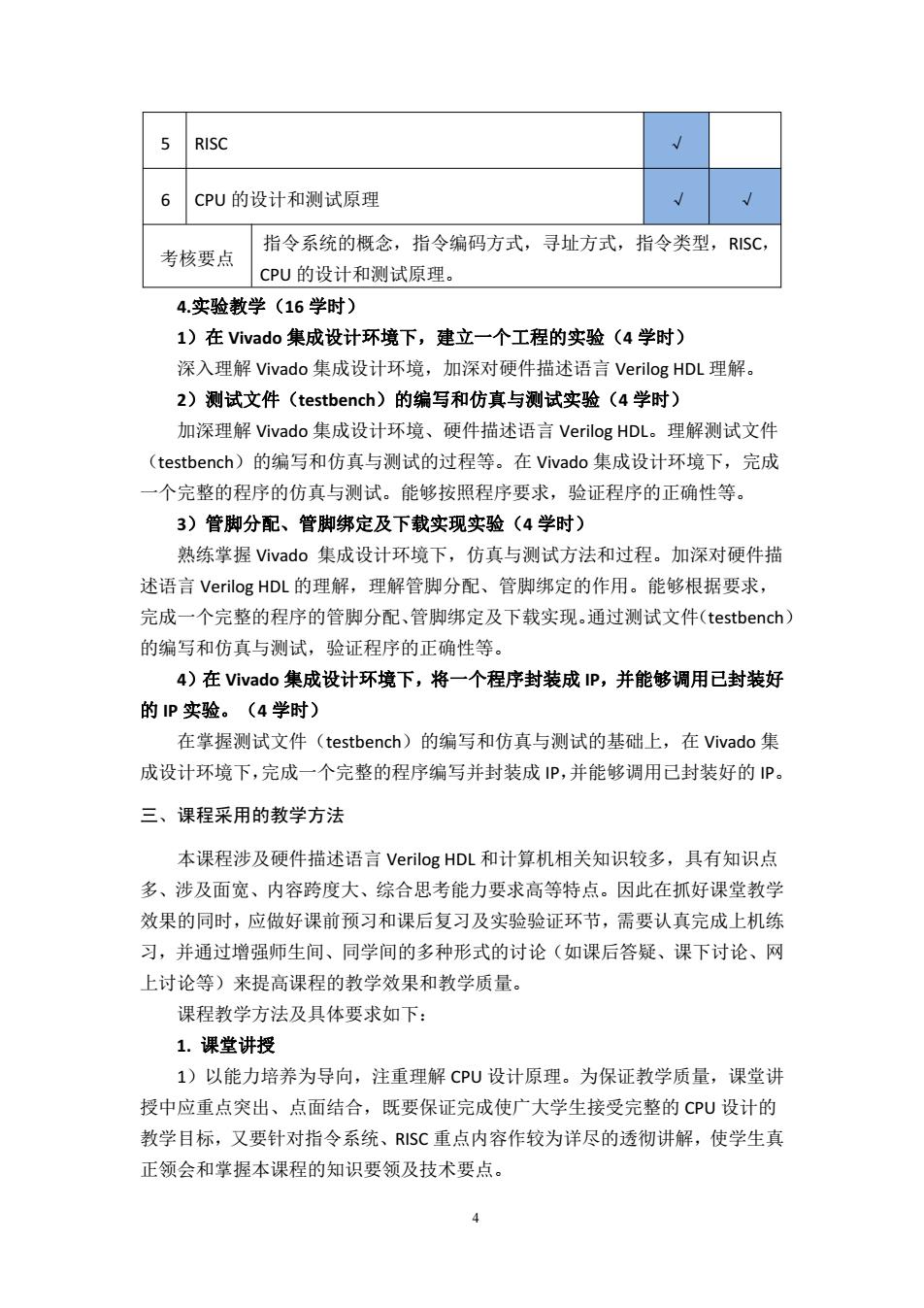

3 教学内容 重点 难点 1 硬件描述语言 Verilog HDL √ 2 Keyboard(开关、按键和 4*4 二维矩阵键盘)原理和实 现 √ 3 LED(7 段数码管和 16*16 点阵显示模块)原理和实现 √ 考核要点 硬件描述语言 Verilog HDL。 Keyboard(开关、按键和 4*4 二维矩阵键盘)原理和实现, LED(7 段数码管和 16*16 点阵显示模块)原理和实现。 第二知识单元 Verilog HDL 例化原理和实现、Verilog HDL 测试文件编写 学时分配 8 学时 教学方式 课堂讲授,PPT 电子课件,板书 教学内容 重点 难点 1 硬件描述语言 Verilog HDL 例化原理和实现 √ √ 2 Verilog HDL 测试文件编写 √ √ 考核要点 硬件描述语言 Verilog HDL 例化原理和实现, Verilog HDL 测试文件编写。 第三知识单元 CPU 的设计和测试原理,及用 Verilog HDL 实现的原理 学时分配 16 学时 教学方式 课堂讲授,PPT 电子课件,板书 教学内容 重点 难点 1 指令系统概述 √ 2 指令编码方式 √ 3 寻址方式 √ 4 指令类型 √

5RISC 6cPU的设计和测试原理 考核要点 指令系统的概念,指令编码方式,寻址方式,指令类型,ISC, cPU的设计和测试原理。 4.实验教学(16学时) 1)在Vivado集成设计环境下,建立一个工程的实验(4学时) 深入理解Vivado集成设计环境,加深对硬件描述语言Verilog HDL理解。 2)测试文件(testbench)的编写和仿真与测试实验(4学时) 加深理解Vivado集成设计环境、硬件描述语言Verilog HDL。理解测试文件 (testbench)的编写和仿真与测试的过程等。在Vivado集成设计环境下,完成 一个完整的程序的仿真与测试。能够按照程序要求,验证程序的正确性等。 3)管脚分配、管脚绑定及下载实现实验(4学时) 熟练掌握Vivado集成设计环境下,仿真与测试方法和过程。加深对硬件描 述语言Verilog HDL的理解,理解管脚分配、管脚绑定的作用。能够根据要求, 完成一个完整的程序的管脚分配、管脚绑定及下载实现。通过测试文件(testbench) 的编写和仿真与测试,验证程序的正确性等。 4)在Vivado集成设计环境下,将一个程序封装成P,并能够调用已封装好 的IP实验。(4学时) 在掌握测试文件(testbench)的编写和仿真与测试的基础上,在Vivado集 成设计环境下,完成一个完整的程序编写并封装成P,并能够调用已封装好的P 三、课程采用的教学方法 本课程涉及硬件描述语言Verilog HDL和计算机相关知识较多,具有知识点 多、涉及面宽、内容跨度大、综合思考能力要求高等特点。因此在抓好课堂教学 效果的同时,应做好课前预习和课后复习及实验验证环节,需要认真完成上机练 习,并通过增强师生间、同学间的多种形式的讨论(如课后答疑、课下讨论、网 上讨论等)来提高课程的教学效果和教学质量。 课程教学方法及具体要求如下: 1.课章讲授 1)以能力培养为导向,注重理解CU设计原理。为保证教学质量,课堂讲 授中应重点突出、点面结合,既要保证完成使广大学生接受完整的CPU设计的 教学目标,又要针对指令系统、RSC重点内容作较为详尽的透彻讲解,使学生真 正领会和学握本课程的知识要领及技术要点。 4

4 5 RISC √ 6 CPU 的设计和测试原理 √ √ 考核要点 指令系统的概念,指令编码方式,寻址方式,指令类型,RISC, CPU 的设计和测试原理。 4.实验教学(16 学时) 1)在 Vivado 集成设计环境下,建立一个工程的实验(4 学时) 深入理解 Vivado 集成设计环境,加深对硬件描述语言 Verilog HDL 理解。 2)测试文件(testbench)的编写和仿真与测试实验(4 学时) 加深理解 Vivado 集成设计环境、硬件描述语言 Verilog HDL。理解测试文件 (testbench)的编写和仿真与测试的过程等。在 Vivado 集成设计环境下,完成 一个完整的程序的仿真与测试。能够按照程序要求,验证程序的正确性等。 3)管脚分配、管脚绑定及下载实现实验(4 学时) 熟练掌握 Vivado 集成设计环境下,仿真与测试方法和过程。加深对硬件描 述语言 Verilog HDL 的理解,理解管脚分配、管脚绑定的作用。能够根据要求, 完成一个完整的程序的管脚分配、管脚绑定及下载实现。通过测试文件(testbench) 的编写和仿真与测试,验证程序的正确性等。 4)在 Vivado 集成设计环境下,将一个程序封装成 IP,并能够调用已封装好 的 IP 实验。(4 学时) 在掌握测试文件(testbench)的编写和仿真与测试的基础上,在 Vivado 集 成设计环境下,完成一个完整的程序编写并封装成 IP,并能够调用已封装好的 IP。 三、课程采用的教学方法 本课程涉及硬件描述语言 Verilog HDL 和计算机相关知识较多,具有知识点 多、涉及面宽、内容跨度大、综合思考能力要求高等特点。因此在抓好课堂教学 效果的同时,应做好课前预习和课后复习及实验验证环节,需要认真完成上机练 习,并通过增强师生间、同学间的多种形式的讨论(如课后答疑、课下讨论、网 上讨论等)来提高课程的教学效果和教学质量。 课程教学方法及具体要求如下: 1. 课堂讲授 1)以能力培养为导向,注重理解 CPU 设计原理。为保证教学质量,课堂讲 授中应重点突出、点面结合,既要保证完成使广大学生接受完整的 CPU 设计的 教学目标,又要针对指令系统、RISC 重点内容作较为详尽的透彻讲解,使学生真 正领会和掌握本课程的知识要领及技术要点

2)注重实践环节。为使同学们能够深入理解ISC原理,特别是CPU内部主 要构成部分、指令在机器内部的执行等重点环节,在教学过程中注重将抽象难懂 的内容,通过硬件描述语言Verilog HDL为学生展示实现方法。 3)多媒体课件与板书结合的教学手段与多种教学方法兼施并用。教学方法 则采取在教师讲授基本教学内容的过程中适当穿插引入个体针对性提问、集体提 问、答疑、讨论等教学形式。 2.讨论与自学 鼓励同学之间或同学与教师之间针对CU设计的重点和难点内容展开讨论, 以澄清知识要点、扩大知识面和培养独立思考能力及创新能力。自学内容应以学 生掌握相关知识结构基础上能比较方便的看懂和理解为原则,教师要布置自学提 纲和思考题。 3课前预习和课后复习 每次课前预习时间应不少于相应教学内容的课堂讲授计划时间,课后复习以 课堂讲授内容为主线、完成相应作业为突破口。 四、建议教材及教学参考书 1.敦学参考书 [1]雷思磊,自己动手写CPU。电子工业出版社。2014年9月 [2)高小鹏,计算机组成与实现。高等教育出版社。2018年12月 「3引张冬冬等,数字罗辑与组成原理实我教程。洁华大学出版社。2018年 8月 「4]吴继华、王成,Verilog设计与验证。人民邮电出版社。2006年8月 [51王金明.数字系统设计与Verilog HDL(第三版).电子工业出版社.2009年 1月 [6]何宾编著.EDA原理及Verilog实现(第1版),清华大学出版社,2010年7 夕 [7]David Patterson John Hennessy.Computer Organization and Design-The Hardware/Software Interface,5th Edition.September 2013 五、知识单元对课程目标的达成度设计 1.知识单元支撑课程目标情况表 围绕每一个具体的课程目标,从相关支撑知识单元的角度设计不同的考核方 式,如下表:

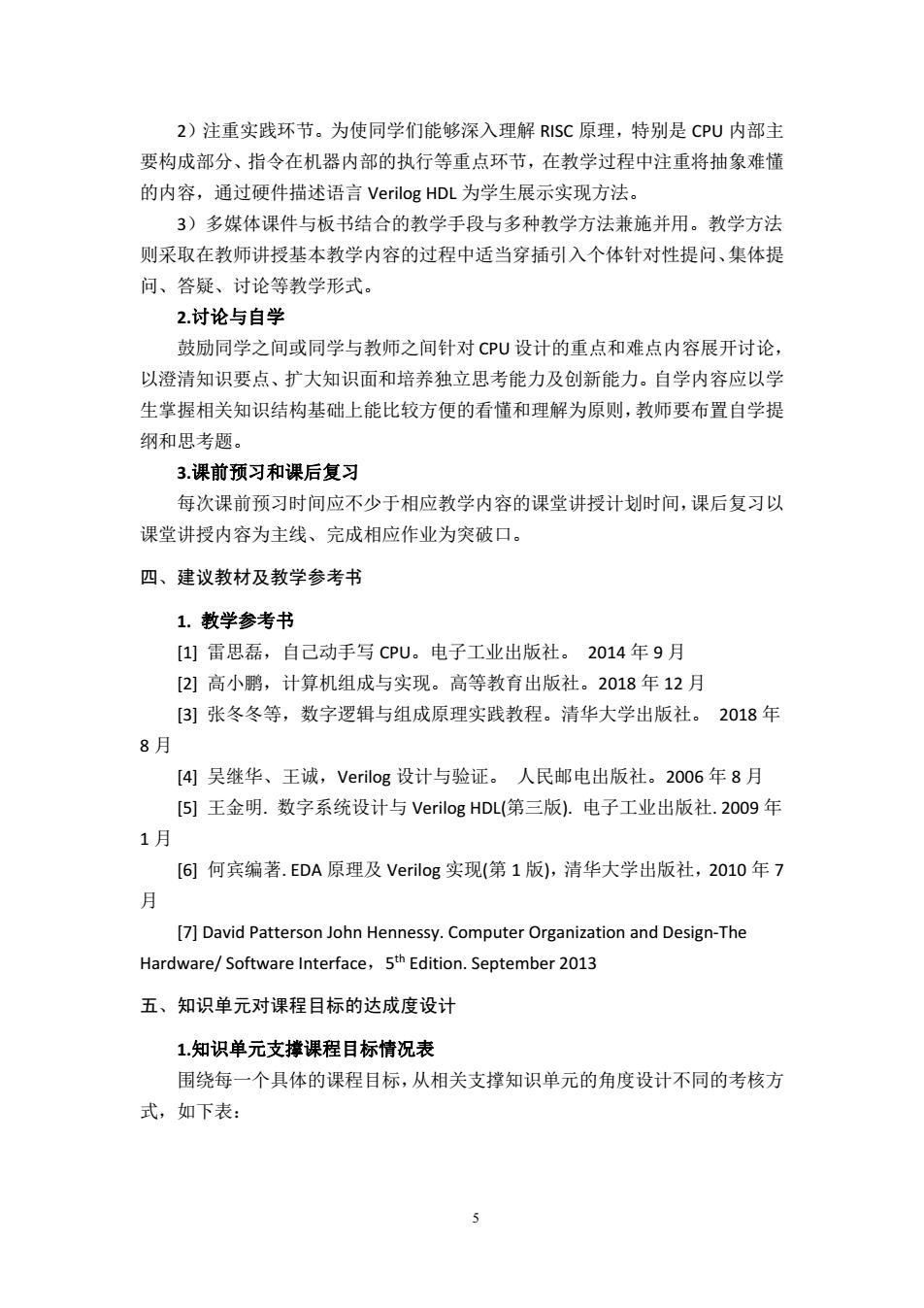

5 2)注重实践环节。为使同学们能够深入理解 RISC 原理,特别是 CPU 内部主 要构成部分、指令在机器内部的执行等重点环节,在教学过程中注重将抽象难懂 的内容,通过硬件描述语言 Verilog HDL 为学生展示实现方法。 3)多媒体课件与板书结合的教学手段与多种教学方法兼施并用。教学方法 则采取在教师讲授基本教学内容的过程中适当穿插引入个体针对性提问、集体提 问、答疑、讨论等教学形式。 2.讨论与自学 鼓励同学之间或同学与教师之间针对 CPU 设计的重点和难点内容展开讨论, 以澄清知识要点、扩大知识面和培养独立思考能力及创新能力。自学内容应以学 生掌握相关知识结构基础上能比较方便的看懂和理解为原则,教师要布置自学提 纲和思考题。 3.课前预习和课后复习 每次课前预习时间应不少于相应教学内容的课堂讲授计划时间,课后复习以 课堂讲授内容为主线、完成相应作业为突破口。 四、建议教材及教学参考书 1. 教学参考书 [1] 雷思磊,自己动手写 CPU。电子工业出版社。 2014 年 9 月 [2] 高小鹏,计算机组成与实现。高等教育出版社。2018 年 12 月 [3] 张冬冬等,数字逻辑与组成原理实践教程。清华大学出版社。 2018 年 8 月 [4] 吴继华、王诚,Verilog 设计与验证。 人民邮电出版社。2006 年 8 月 [5] 王金明. 数字系统设计与 Verilog HDL(第三版). 电子工业出版社. 2009 年 1 月 [6] 何宾编著. EDA 原理及 Verilog 实现(第 1 版),清华大学出版社,2010 年 7 月 [7] David Patterson John Hennessy. Computer Organization and Design-The Hardware/ Software Interface,5 th Edition. September 2013 五、知识单元对课程目标的达成度设计 1.知识单元支撑课程目标情况表 围绕每一个具体的课程目标,从相关支撑知识单元的角度设计不同的考核方 式,如下表:

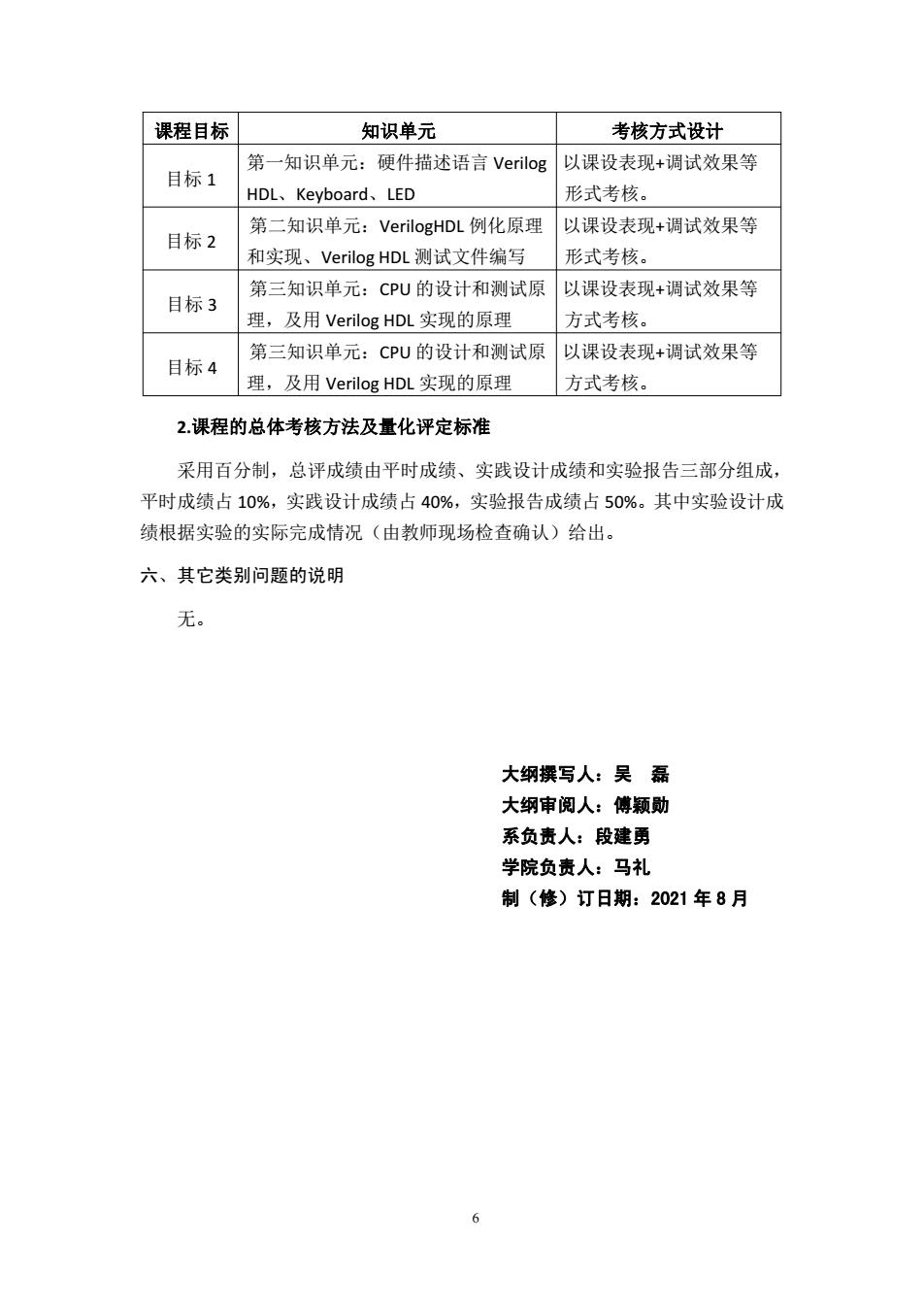

课程目标 知识单元 考核方式设计 第一知识单元:硬件描述语言Verilog以课设表现+调试效果等 目标1 HDL、Keyboard、LED 形式考核。 第二知识单元:VerilogHDL例化原理以课设表现+调试效果等 目标2 和实现、Verilog HDL测试文件编写形式考核。 目标3 第三知识单元:CPU的设计和测试原以课设表现+调试效果等 理,及用Verilog HDL实现的原理 方式考核。 第三知识单元:CPU的设计和测试原以课设表现+调试效果等 目标4 理,及用Verilog HDL实现的原理 方式考核。 2.课程的总体考核方法及量化评定标准 采用百分制,总评成绩由平时成绩、实践设计成绩和实验报告三部分组成 平时成绩占10%,实践设计成绩占40%,实验报告成绩占50%。其中实验设计成 绩根据实验的实际完成情况(由教师现场检查确认)给出。 六、其它类别问题的说明 无 大纲撰写人:吴磊 大纲审阅人:傅颖勋 系负责人:段建勇 学院负责人:马礼 制(修)订日期:2021年8月 6

6 课程目标 知识单元 考核方式设计 目标 1 第一知识单元:硬件描述语言 Verilog HDL、Keyboard、LED 以课设表现+调试效果等 形式考核。 目标 2 第二知识单元:VerilogHDL 例化原理 和实现、Verilog HDL 测试文件编写 以课设表现+调试效果等 形式考核。 目标 3 第三知识单元:CPU 的设计和测试原 理,及用 Verilog HDL 实现的原理 以课设表现+调试效果等 方式考核。 目标 4 第三知识单元:CPU 的设计和测试原 理,及用 Verilog HDL 实现的原理 以课设表现+调试效果等 方式考核。 2.课程的总体考核方法及量化评定标准 采用百分制,总评成绩由平时成绩、实践设计成绩和实验报告三部分组成, 平时成绩占 10%,实践设计成绩占 40%,实验报告成绩占 50%。其中实验设计成 绩根据实验的实际完成情况(由教师现场检查确认)给出。 六、其它类别问题的说明 无。 大纲撰写人:吴 磊 大纲审阅人:傅颖勋 系负责人:段建勇 学院负责人:马礼 制(修)订日期:2021 年 8 月