正在加载图片...

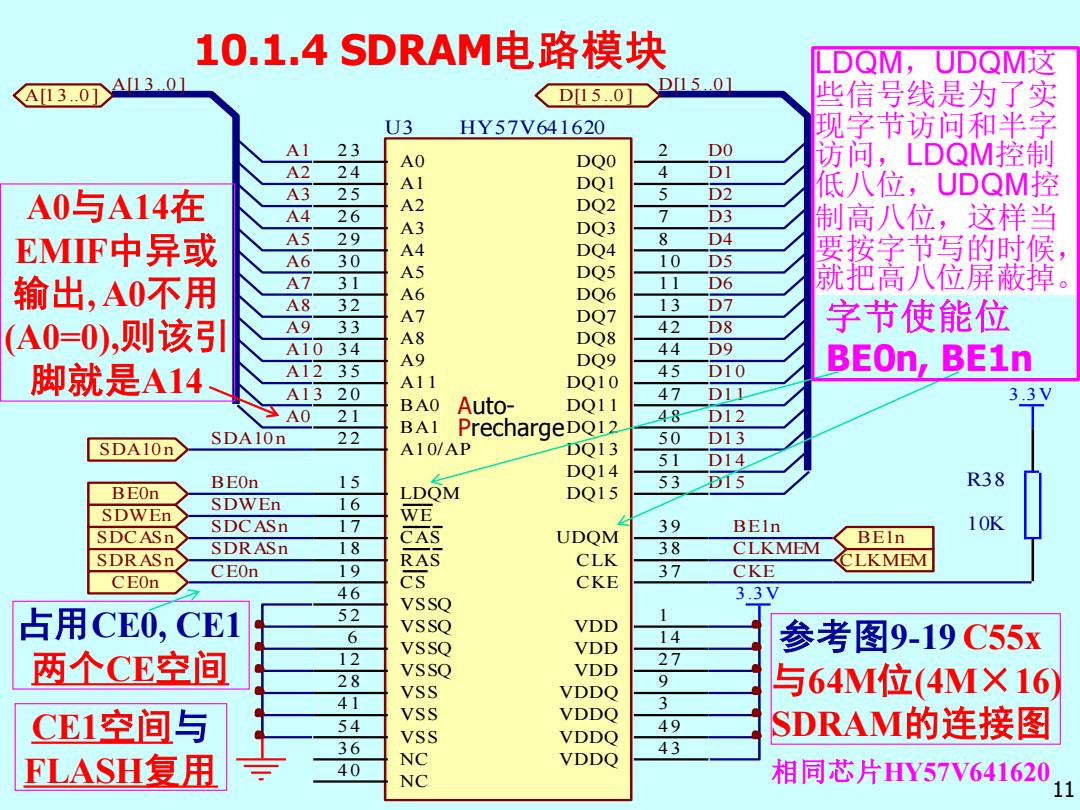

10.1.4 SDRAM电路模块 LDQM,UDQM☒ A[13.0 A1301 D15.01 D15.0] 些信号线是为了实 U3 HY57V641620 现字节访问和半字 23 2 A0 DO DQO 访问,LDQM控制 A2 24 4 A3 Al DQI DI A0与A14在 25 5 D2 低八位,UDQM控 A2 A4 26 DQ2 7 D3 A5 A3 DQ3 制高八位,这样当 EMIF中异或 29 8 D4 A4 DQ4 A6 30 10 D5 要按字节写的时候, A5 DQ5 输出,A0不用 A7 31 11 D6 就把高八位屏蔽掉。 A6 DQ6 A8 32 A7 13 D7 DQ7 (A0=0),则该引 A9 33 42 D8 字节使能位 A1034 A8 DQ8 44 A1235 A9 D9 DQ9 脚就是A14 A11 45 D10 BEOn,BE1n DQ10 A1320 Auto- 47 DIL 3.3V BAO DQ11 A0 21 48 D12 BAI SDA10n 22 PrechargeDQ12 50 D13 SDA10n A10/AP DQ13 51 D14 BEOn 15 DQ14 53D15 R38 BEOn LDQM DQ15 SDWEn 16 SDWEn SDCASn WE 17 CAS 39 BEln 10K SDCASn UDQM SDRASn 18 38 CLKMEM BEIn SDRASn CEOn CLK LKMEM 19 RAS 37 CEOn Cs CKE CKE 46 VSSQ 33V 占用CE0,CE1 52 VSSQ VDD 6 14 VSSQ VDD 参考图9-19C55x 两个CE空间 12 27 VSSQ VDD 28 9 VSS VDDQ 与64M位(4M×16 41 3 CE1空间与 VSS VDDQ 54 49 VSS VDDQ SDRAMI的连接图 36 43 FLASH复用 NC 40 VDDQ NC 相同芯片Y57V64162010.1.4 SDRAM电路模块 VDD 1 DQ0 2 DQ1 4 DQ2 5 VDDQ 3 VSSQ 6 DQ3 7 DQ4 8 VDDQ 9 DQ5 1 0 DQ6 1 1 VSSQ 1 2 DQ7 1 3 VDD 1 4 LDQM 1 5 W E 1 6 CAS 1 7 RAS 1 8 C S 1 9 BA0 2 0 BA1 2 1 A1 0/AP 2 2 A 0 2 3 A 1 2 4 A 2 2 5 A 3 2 6 VDD 2 7 VSS 2 8 A 4 2 9 A 5 3 0 A 6 3 1 A 7 3 2 A 8 3 3 A 9 3 4 A1 1 3 5 N C 3 6 CKE 3 7 CLK 3 8 UDQM 3 9 N C 4 0 VSS 4 1 DQ8 4 2 VDDQ 4 3 DQ9 4 4 DQ1 0 4 5 VSSQ 4 6 DQ1 1 4 7 DQ1 2 4 8 VDDQ 4 9 DQ1 3 5 0 DQ1 4 5 1 VSSQ 5 2 DQ1 5 5 3 VSS 5 4 U 3 HY57V641620 A[1 3 ..0 ] A 1 A 2 A 3 A 4 A 5 A 6 A 7 A 8 A 9 A1 0 SDA10 n A1 2 A1 3 A 0 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 D 8 D 9 D1 0 D1 1 D1 2 D1 3 D1 4 D1 5 D[1 5 ..0 ] 3 .3 V BE0n SDWEn SDCASn SDRASn CE0n BE1n CLKMEM CKE R38 10K 3 .3 V A[1 3 ..0 ] D[1 5 ..0 ] SDA10 n BE0n SDWEn SDCASn SDRASn CE0n BE1n CLKMEM 11 参考图9-19 C55x 与64M位(4M×16) SDRAM的连接图 A0与A14在 EMIF中异或 输出, A0不用 (A0=0),则该引 脚就是A14 LDQM,UDQM这 些信号线是为了实 现字节访问和半字 访问,LDQM控制 低八位,UDQM控 制高八位,这样当 要按字节写的时候, 就把高八位屏蔽掉。 字节使能位 BE0n, BE1n AutoPrecharge 占用CE0, CE1 两个CE空间 CE1空间与 FLASH复用 相同芯片HY57V641620 占用两个空间 和