正在加载图片...

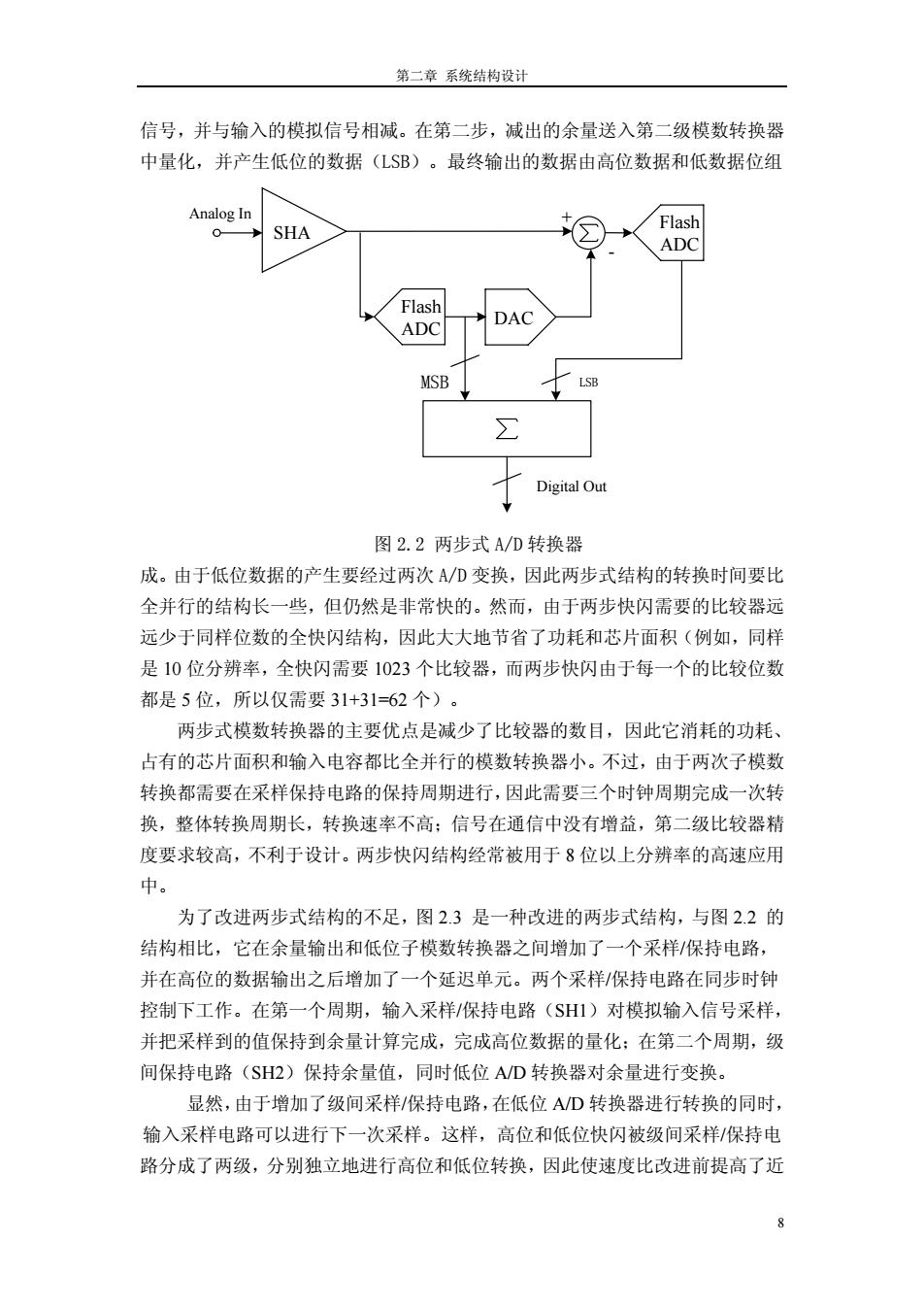

第二章系统结构设计 信号,并与输入的模拟信号相减。在第二步,减出的余量送入第二级模数转换器 中量化,并产生低位的数据(LSB)。最终输出的数据由高位数据和低数据位组 Analog In 0 Flash SHA ADC Flash DAC ADC MSB LSB 工 Digital Out 图2.2两步式A/D转换器 成。由于低位数据的产生要经过两次A/D变换,因此两步式结构的转换时间要比 全并行的结构长一些,但仍然是非常快的。然而,由于两步快闪需要的比较器远 远少于同样位数的全快闪结构,因此大大地节省了功耗和芯片面积(例如,同样 是10位分辨率,全快闪需要1023个比较器,而两步快闪由于每一个的比较位数 都是5位,所以仅需要31+31=62个)。 两步式模数转换器的主要优点是减少了比较器的数目,因此它消耗的功耗、 占有的芯片面积和输入电容都比全并行的模数转换器小。不过,由于两次子模数 转换都需要在采样保持电路的保持周期进行,因此需要三个时钟周期完成一次转 换,整体转换周期长,转换速率不高:信号在通信中没有增益,第二级比较器精 度要求较高,不利于设计。两步快闪结构经常被用于8位以上分辨率的高速应用 中。 为了改进两步式结构的不足,图2.3是一种改进的两步式结构,与图2.2的 结构相比,它在余量输出和低位子模数转换器之间增加了一个采样/保持电路, 并在高位的数据输出之后增加了一个延迟单元。两个采样/保持电路在同步时钟 控制下工作。在第一个周期,输入采样/保持电路(SH1)对模拟输入信号采样, 并把采样到的值保持到余量计算完成,完成高位数据的量化:在第二个周期,级 间保持电路(SH2)保持余量值,同时低位AD转换器对余量进行变换。 显然,由于增加了级间采样/保持电路,在低位AD转换器进行转换的同时, 输入采样电路可以进行下一次采样。这样,高位和低位快闪被级间采样/保持电 路分成了两级,分别独立地进行高位和低位转换,因此使速度比改进前提高了近 8第二章 系统结构设计 信号,并与输入的模拟信号相减。在第二步,减出的余量送入第二级模数转换器 图 2.2 两步式 A/D 转换器 中量化,并产生低位的数据(LSB)。最终输出的数据由高位数据和低数据位组 成。由于低位数据的产生要经 式结构的转换时间要比 占有 了改进两步式结构的不足,图 2.3 是一种改进的两步式结构,与图 2.2 的 结构 时, 输入 Flash ADC Analog In + - MSB LSB Digital Out SHA DAC Flash ADC 过两次 A/D 变换,因此两步 全并行的结构长一些,但仍然是非常快的。然而,由于两步快闪需要的比较器远 远少于同样位数的全快闪结构,因此大大地节省了功耗和芯片面积(例如,同样 是 10 位分辨率,全快闪需要 1023 个比较器,而两步快闪由于每一个的比较位数 都是 5 位,所以仅需要 31+31=62 个)。 两步式模数转换器的主要优点是减少了比较器的数目,因此它消耗的功耗、 的芯片面积和输入电容都比全并行的模数转换器小。不过,由于两次子模数 转换都需要在采样保持电路的保持周期进行,因此需要三个时钟周期完成一次转 换,整体转换周期长,转换速率不高;信号在通信中没有增益,第二级比较器精 度要求较高,不利于设计。两步快闪结构经常被用于 8 位以上分辨率的高速应用 中。 为 相比,它在余量输出和低位子模数转换器之间增加了一个采样/保持电路, 并在高位的数据输出之后增加了一个延迟单元。两个采样/保持电路在同步时钟 控制下工作。在第一个周期,输入采样/保持电路(SH1)对模拟输入信号采样, 并把采样到的值保持到余量计算完成,完成高位数据的量化;在第二个周期,级 间保持电路(SH2)保持余量值,同时低位 A/D 转换器对余量进行变换。 显然,由于增加了级间采样/保持电路,在低位 A/D 转换器进行转换的同 采样电路可以进行下一次采样。这样,高位和低位快闪被级间采样/保持电 路分成了两级,分别独立地进行高位和低位转换,因此使速度比改进前提高了近 8