正在加载图片...

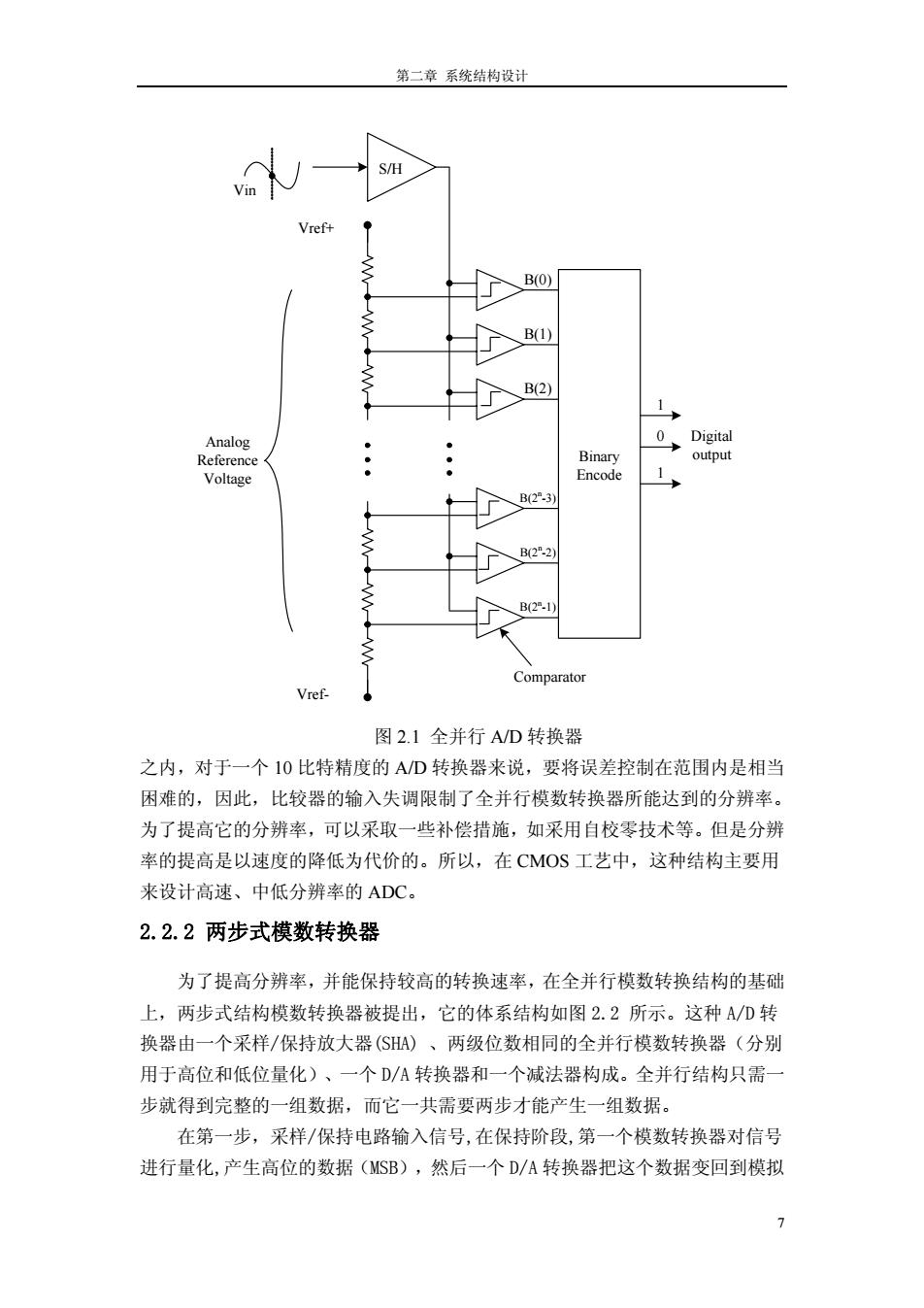

第二章系统结构设计 S/H Vref+ B(0) B(1) B(2) 1 Analog 0、Digital Reference Binary output Voltage Encode 1 B(23) B(2-2) B(2-1) Comparator Vref- 图2.1全并行AD转换器 之内,对于一个10比特精度的AD转换器来说,要将误差控制在范围内是相当 困难的,因此,比较器的输入失调限制了全并行模数转换器所能达到的分辨率。 为了提高它的分辨率,可以采取一些补偿措施,如采用自校零技术等。但是分辨 率的提高是以速度的降低为代价的。所以,在CMOS工艺中,这种结构主要用 来设计高速、中低分辨率的ADC。 2.2.2两步式模数转换器 为了提高分辨率,并能保持较高的转换速率,在全并行模数转换结构的基础 上,两步式结构模数转换器被提出,它的体系结构如图2.2所示。这种A/D转 换器由一个采样/保持放大器(SHA)、两级位数相同的全并行模数转换器(分别 用于高位和低位量化)、一个D/A转换器和一个减法器构成。全并行结构只需一 步就得到完整的一组数据,而它一共需要两步才能产生一组数据。 在第一步,采样/保持电路输入信号,在保持阶段,第一个模数转换器对信号 进行量化,产生高位的数据(MSB),然后一个D/A转换器把这个数据变回到模拟 1第二章 系统结构设计 Binary Encode Comparator S/H B(0) B(2) B(2n -3) B(2n -2) B(2n -1) B(1) 1 Digital output Vin Vref+ VrefAnalog Reference Voltage 0 1 图 2.1 全并行 A/D 转换器 之内,对于一个 10 比特精度的 A/D 转换器来说,要将误差控制在范围内是相当 困难的,因此,比较器的输入失调限制了全并行模数转换器所能达到的分辨率。 为了提高它的分辨率,可以采取一些补偿措施,如采用自校零技术等。但是分辨 率的提高是以速度的降低为代价的。所以,在 CMOS 工艺中,这种结构主要用 来设计高速、中低分辨率的 ADC。 2.2.2 两步式模数转换器 为了提高分辨率,并能保持较高的转换速率,在全并行模数转换结构的基础 上,两步式结构模数转换器被提出,它的体系结构如图 2.2 所示。这种 A/D 转 换器由一个采样/保持放大器(SHA) 、两级位数相同的全并行模数转换器(分别 用于高位和低位量化)、一个 D/A 转换器和一个减法器构成。全并行结构只需一 步就得到完整的一组数据,而它一共需要两步才能产生一组数据。 在第一步,采样/保持电路输入信号,在保持阶段,第一个模数转换器对信号 进行量化,产生高位的数据(MSB),然后一个 D/A 转换器把这个数据变回到模拟 7