正在加载图片...

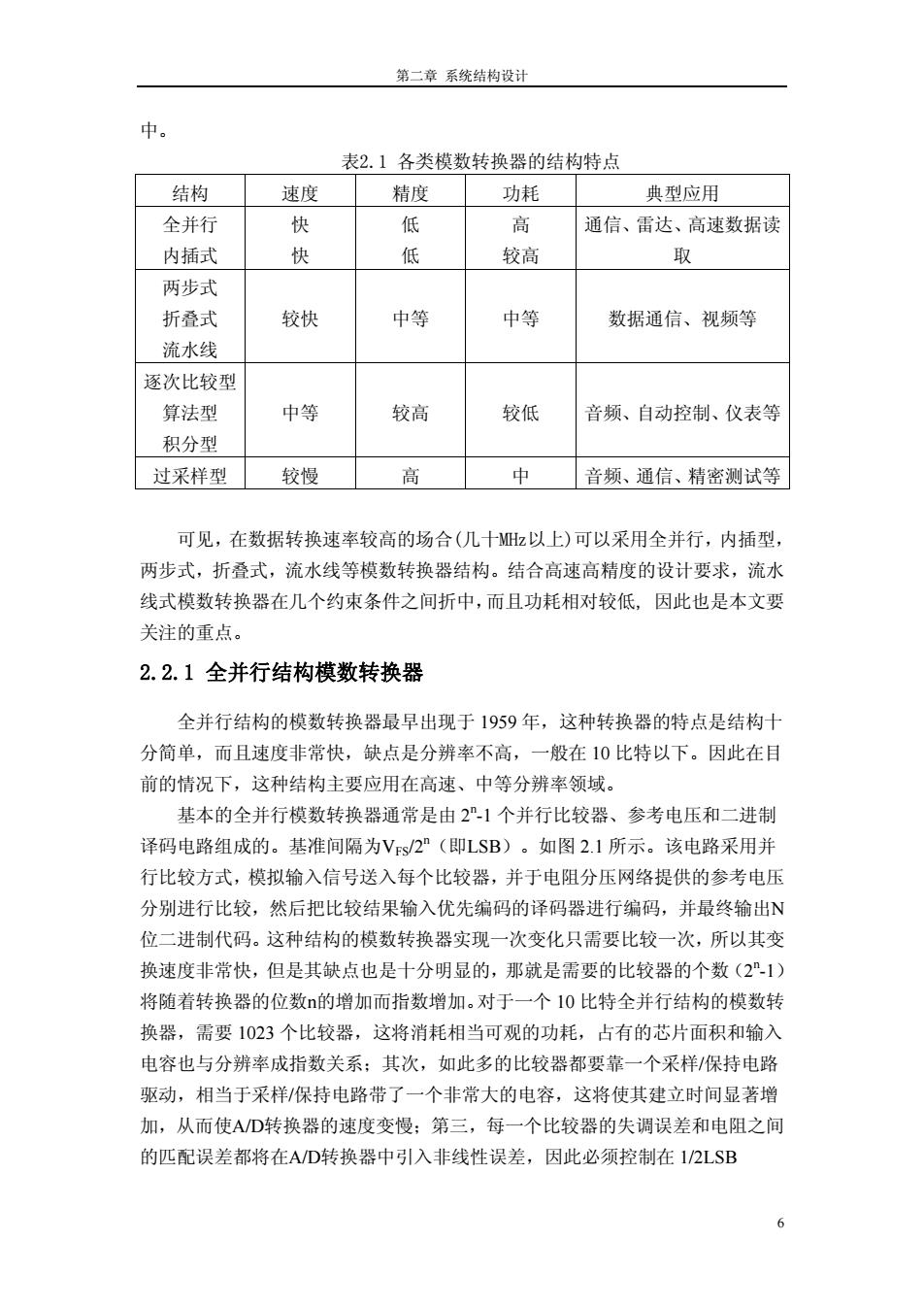

第二章系统结构设计 中。 表2.1各类模数转换器的结构特点 结构 速度 精度 功耗 典型应用 全并行 快 低 高 通信、雷达、高速数据读 内插式 快 低 较高 取 两步式 折叠式 较快 中等 中等 数据通信、视频等 流水线 逐次比较型 算法型 中等 较高 较低 音频、自动控制、仪表等 积分型 过采样型 较慢 高 中 音频、通信、精密测试等 可见,在数据转换速率较高的场合(几十MHz以上)可以采用全并行,内插型, 两步式,折叠式,流水线等模数转换器结构。结合高速高精度的设计要求,流水 线式模数转换器在几个约束条件之间折中,而且功耗相对较低,因此也是本文要 关注的重点。 2.2.1全并行结构模数转换器 全并行结构的模数转换器最早出现于1959年,这种转换器的特点是结构十 分简单,而且速度非常快,缺点是分辨率不高,一般在10比特以下。因此在目 前的情况下,这种结构主要应用在高速、中等分辨率领域。 基本的全并行模数转换器通常是由21个并行比较器、参考电压和二进制 译码电路组成的。基准间隔为Vs/2”(即LSB)。如图2.1所示。该电路采用并 行比较方式,模拟输入信号送入每个比较器,并于电阻分压网络提供的参考电压 分别进行比较,然后把比较结果输入优先编码的译码器进行编码,并最终输出N 位二进制代码。这种结构的模数转换器实现一次变化只需要比较一次,所以其变 换速度非常快,但是其缺点也是十分明显的,那就是需要的比较器的个数(2”1) 将随着转换器的位数n的增加而指数增加。对于一个10比特全并行结构的模数转 换器,需要1023个比较器,这将消耗相当可观的功耗,占有的芯片面积和输入 电容也与分辨率成指数关系;其次,如此多的比较器都要靠一个采样/保持电路 驱动,相当于采样/保持电路带了一个非常大的电容,这将使其建立时间显著增 加,从而使AD转换器的速度变慢;第三,每一个比较器的失调误差和电阻之间 的匹配误差都将在AD转换器中引入非线性误差,因此必须控制在1/2LSB 6第二章 系统结构设计 中。 表2.1 各类模数转换器的结构特点 结构 速度 精度 功耗 典型应用 全并行 内插式 快 快 低 低 高 较高 通信、雷达、高速数据读 取 两步式 折叠式 流水线 较快 中等 中等 数据通信、视频等 逐次比较型 算法型 积分型 中等 较高 较低 音频、自动控制、仪表等 过采样型 较慢 高 中 音频、通信、精密测试等 可见,在数据转换速率较高的场合(几十MHz以上)可以采用全并行,内插型, 两步式,折叠式,流水线等模数转换器结构。结合高速高精度的设计要求,流水 线式模数转换器在几个约束条件之间折中,而且功耗相对较低, 因此也是本文要 关注的重点。 2.2.1 全并行结构模数转换器 全并行结构的模数转换器最早出现于 1959 年,这种转换器的特点是结构十 分简单,而且速度非常快,缺点是分辨率不高,一般在 10 比特以下。因此在目 前的情况下,这种结构主要应用在高速、中等分辨率领域。 基本的全并行模数转换器通常是由 2n -1 个并行比较器、参考电压和二进制 译码电路组成的。基准间隔为VFS/2n (即LSB)。如图 2.1 所示。该电路采用并 行比较方式,模拟输入信号送入每个比较器,并于电阻分压网络提供的参考电压 分别进行比较,然后把比较结果输入优先编码的译码器进行编码,并最终输出N 位二进制代码。这种结构的模数转换器实现一次变化只需要比较一次,所以其变 换速度非常快,但是其缺点也是十分明显的,那就是需要的比较器的个数(2n -1) 将随着转换器的位数n的增加而指数增加。对于一个 10 比特全并行结构的模数转 换器,需要 1023 个比较器,这将消耗相当可观的功耗,占有的芯片面积和输入 电容也与分辨率成指数关系;其次,如此多的比较器都要靠一个采样/保持电路 驱动,相当于采样/保持电路带了一个非常大的电容,这将使其建立时间显著增 加,从而使A/D转换器的速度变慢;第三,每一个比较器的失调误差和电阻之间 的匹配误差都将在A/D转换器中引入非线性误差,因此必须控制在 1/2LSB 6