正在加载图片...

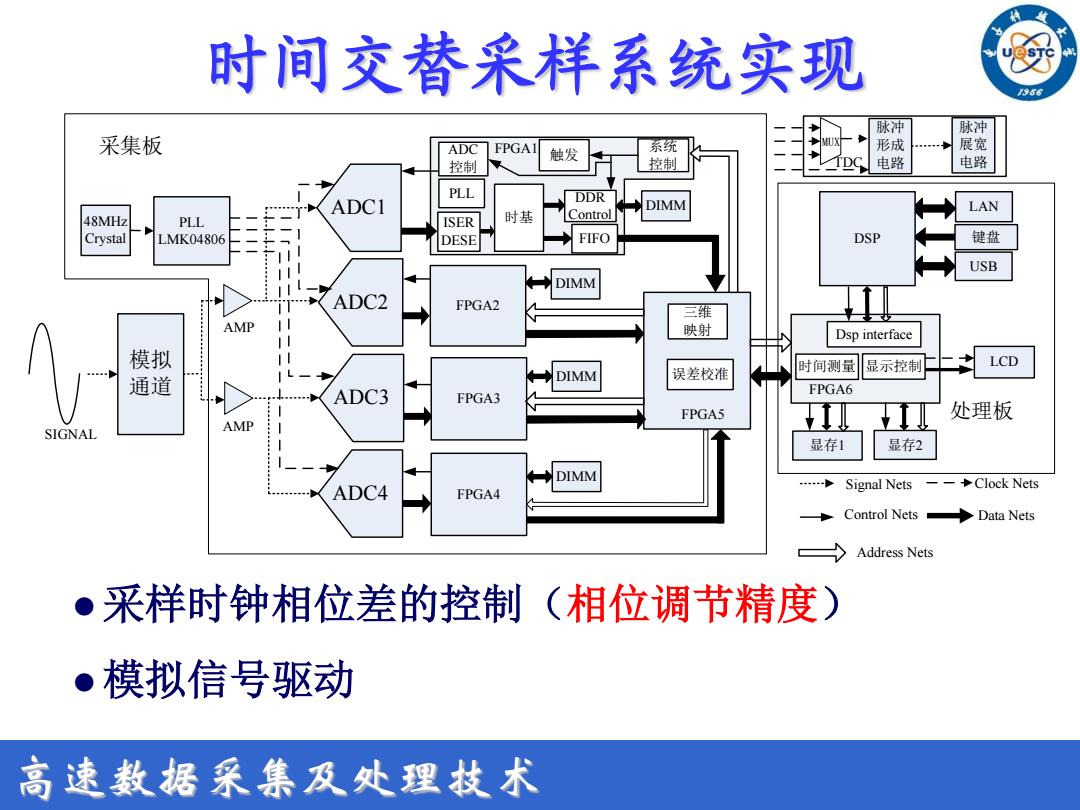

时间交替采样系统实现 脉冲 脉冲 采集板 ADC 触发 系统 形成 展宽 控制 控制 电路 电路 PLL ADCI DDR DIMM LAN 48MHz PLL ISER 时基 Control Crystal LMK04806 DESE FIFO DSP 键盘 USB DIMM T… ADC2 FPGA2 三维 AMP II 映射 11 Dsp interface 模拟 11 时间测量 显示控制 LCD 通道 DIMM 误差校准 …〈ADC3 FPGA6 FPGA3 FPGA5 处理板 SIGNAL AMP 显存1 显存2 DIMM Signal Nets 一一 ADC4 +Clock Nets FPGA4 Control Nets Data Nets Address Nets ·采样时钟相位差的控制(相位调节精度) ·模拟信号驱动 高速数据采集及处理技术高速数据采集及处理技术 时间交替采样系统实现 Control Nets Data Nets PLL LMK04806 LCD 键盘 USB Clock Nets Address Nets Signal Nets 48MHz Crystal ADC1 LAN 显存1 显存2 显示控制 ADC2 ADC3 ADC4 FPGA6 DSP Dsp interface ISER DESE FIFO DDR Control ADC 控制 系统 控制 FPGA1 时基 DIMM 触发 PLL DIMM DIMM DIMM FPGA5 三维 映射 误差校准 处理板 模拟 通道 SIGNAL AMP AMP 采集板 FPGA2 FPGA3 FPGA4 脉冲 形成 电路 脉冲 展宽 TDC 电路 MUX 时间测量 采样时钟相位差的控制(相位调节精度) 模拟信号驱动