956 高采样率技术 杨扩军副研究员 高速数据采集及处理技术

高速数据采集及处理技术 高采样率技术 杨扩军 副研究员

实现高采样率的技术瓶颈 。单片ADC的采样率和分辨率是一对矛盾。 ●器件制造工艺限制了单片ADC最高采样率 ·如何在现有器件条件下解决高采样率问题? ·并行采集 时间交替采样(Time-interleaving) 频率交替采样(Frequency-interleaving) 高速数据采集及处理技术

高速数据采集及处理技术 单片ADC的采样率和分辨率是一对矛盾。 器件制造工艺限制了单片ADC最高采样率 如何在现有器件条件下解决高采样率问题? 并行采集 时间交替采样(Time-interleaving) 频率交替采样(Frequency-interleaving) 实现高采样率的技术瓶颈

时间交替采样原理 /956 MT 女0 0M-1 x1[n] XM-[n] r(t) Time nMT+to (nM+1)T+t1 (nM+M-1)T+tm-1 高速数据采集及处理技术

高速数据采集及处理技术 时间交替采样原理

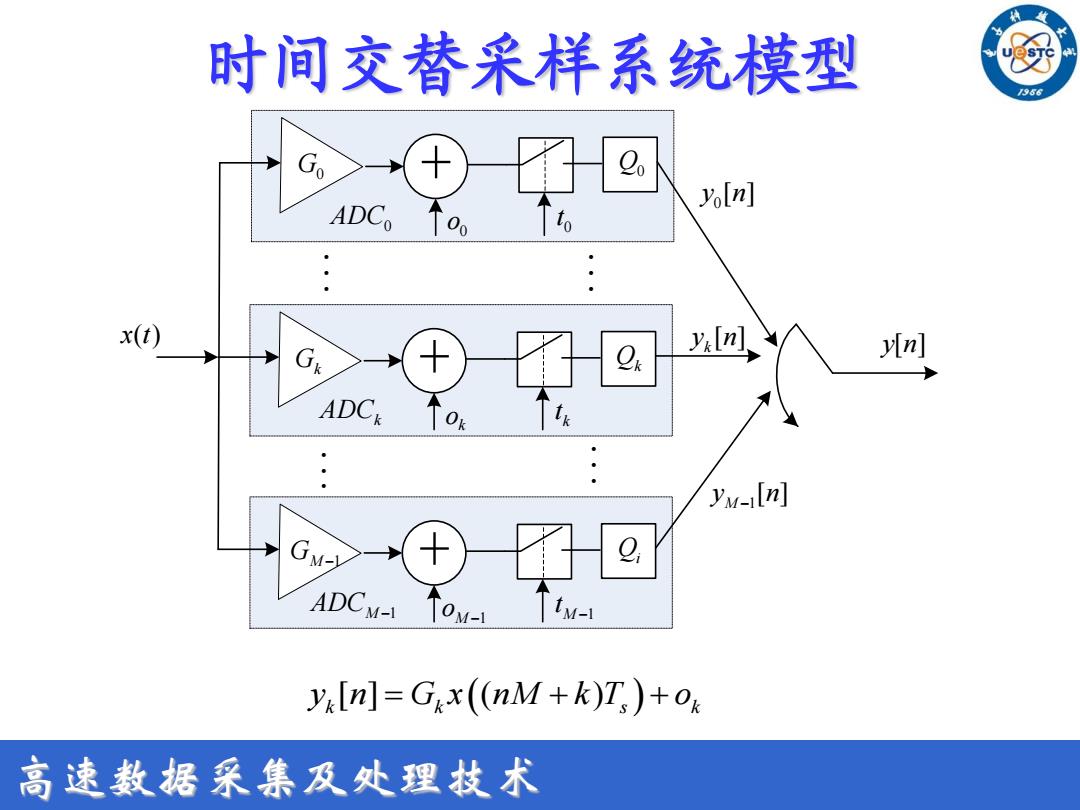

时间交替采样系统模型 /956 G ADCo Yo[n] 00 x(t) y n ADC yu-[n] ADCM- M-1 yx[n]=Gxx((nM+k)T)+o 高速数据采集及处理技术

高速数据采集及处理技术 时间交替采样系统模型 + ADC0 x t( ) G0 0 o 0 y n[ ] Q0 0 t + ADCk Gk k o [ ] k y n Qk kt + ADCM 1 GM 1 M 1 o 1[ ] M y n Qi M 1 t ... ... ... ... y n[ ] y n G x nM k T o k k s k [ ] ( )

时间交替采样系统模型 95 yx[n]=Gxx((nM+k)T)+ox m=号4网=2G,xoM+k)+o: k=0 k=0 8-a1M- M-】 yn]=>x((nM+k)T.)=x(nT,) k=0 由M个采样率为fM的子ADC构成的 TIADC与一个采样率为f的ADC的采样效 果是一样的 高速数据采集及处理技术

高速数据采集及处理技术 时间交替采样系统模型 y n G x nM k T o k k s k [ ] ( ) 1 1 0 0 [ ] [ ] ( ) M M k k s k k k y n y n G x nM k T o 0 0,1,..., 1 1 k k o k M G 1 0 [ ] ( ) = M s s k y n x nM k T x nT 由 M 个采样率为 fs /M 的 子 ADC 构成的 TIADC与一个采样率为fs的ADC的采样效 果是一样的

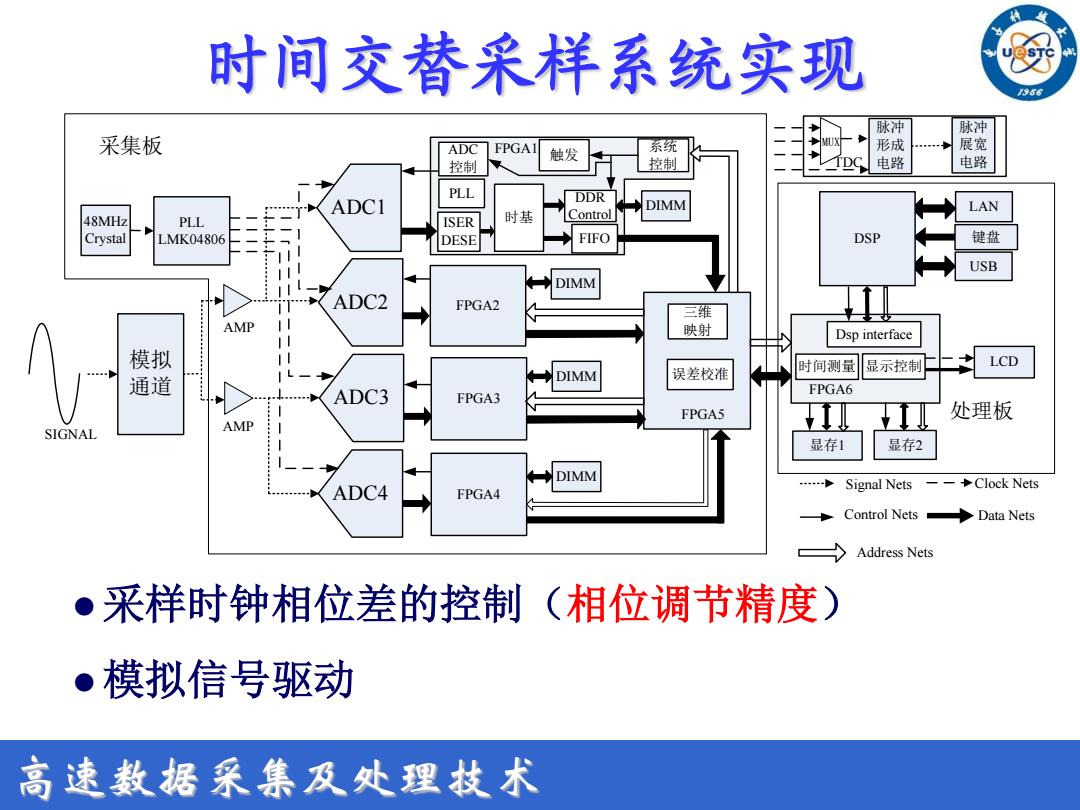

时间交替采样系统实现 脉冲 脉冲 采集板 ADC 触发 系统 形成 展宽 控制 控制 电路 电路 PLL ADCI DDR DIMM LAN 48MHz PLL ISER 时基 Control Crystal LMK04806 DESE FIFO DSP 键盘 USB DIMM T… ADC2 FPGA2 三维 AMP II 映射 11 Dsp interface 模拟 11 时间测量 显示控制 LCD 通道 DIMM 误差校准 …〈ADC3 FPGA6 FPGA3 FPGA5 处理板 SIGNAL AMP 显存1 显存2 DIMM Signal Nets 一一 ADC4 +Clock Nets FPGA4 Control Nets Data Nets Address Nets ·采样时钟相位差的控制(相位调节精度) ·模拟信号驱动 高速数据采集及处理技术

高速数据采集及处理技术 时间交替采样系统实现 Control Nets Data Nets PLL LMK04806 LCD 键盘 USB Clock Nets Address Nets Signal Nets 48MHz Crystal ADC1 LAN 显存1 显存2 显示控制 ADC2 ADC3 ADC4 FPGA6 DSP Dsp interface ISER DESE FIFO DDR Control ADC 控制 系统 控制 FPGA1 时基 DIMM 触发 PLL DIMM DIMM DIMM FPGA5 三维 映射 误差校准 处理板 模拟 通道 SIGNAL AMP AMP 采集板 FPGA2 FPGA3 FPGA4 脉冲 形成 电路 脉冲 展宽 TDC 电路 MUX 时间测量 采样时钟相位差的控制(相位调节精度) 模拟信号驱动

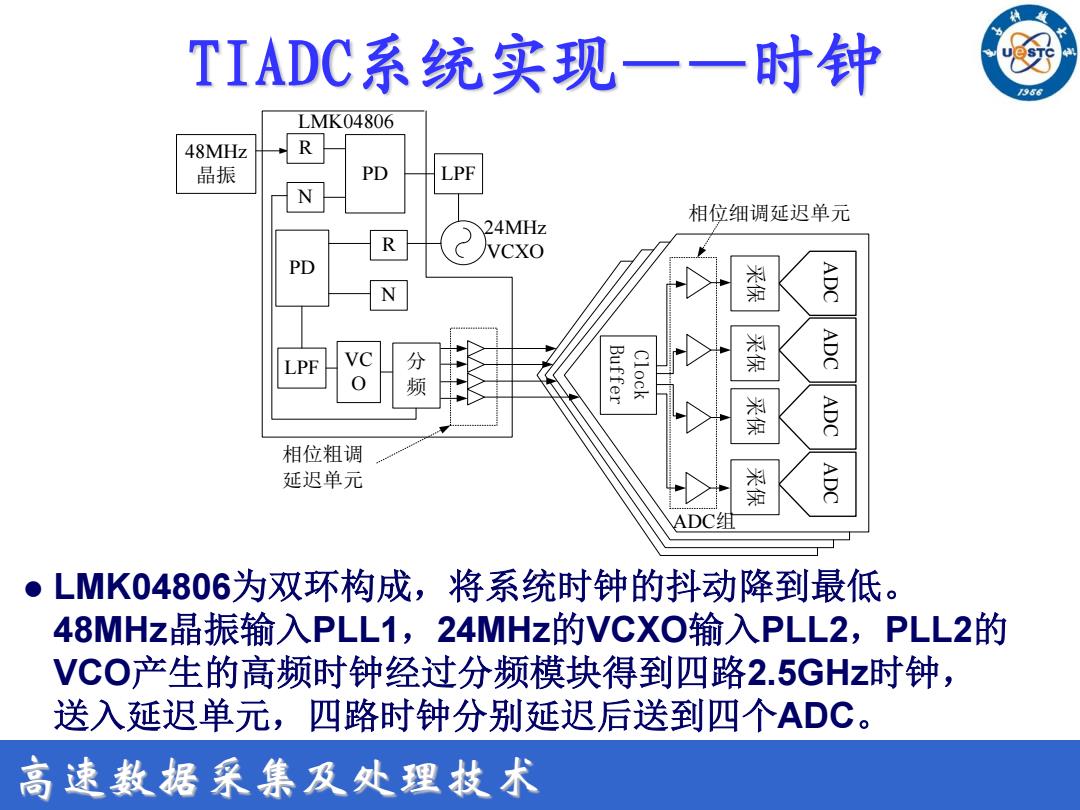

TIADC系统实现一一时钟 /956 LMK04806 48MHz R 晶振 PD LPF 相位细调延迟单元 24MHz R VCXO PD N 萄 ADC 言 频 Buffer Clock 尝 常 相位粗调 延迟单元 霜 ADC ADC组 ●LMK04806为双环构成,将系统时钟的抖动降到最低。 48MHz晶振输入PLL1,24MHz的VCXO输入PLL2,PLL2的 VCO产生的高频时钟经过分频模块得到四路2.5GHz时钟, 送入延迟单元,四路时钟分别延迟后送到四个ADC。 高速数据采集及处理技术

高速数据采集及处理技术 TIADC系统实现——时钟 LMK04806为双环构成,将系统时钟的抖动降到最低。 48MHz晶振输入PLL1,24MHz的VCXO输入PLL2,PLL2的 VCO产生的高频时钟经过分频模块得到四路2.5GHz时钟, 送入延迟单元,四路时钟分别延迟后送到四个ADC。 48MHz 晶振 R N LPF VC O ADC ADC ADC ADC 采保 采保 采保 采保 Clock Buffer 24MHz VCXO 分 频 ADC组 相位细调延迟单元 相位粗调 延迟单元 LMK04806 R PD LPF N PD

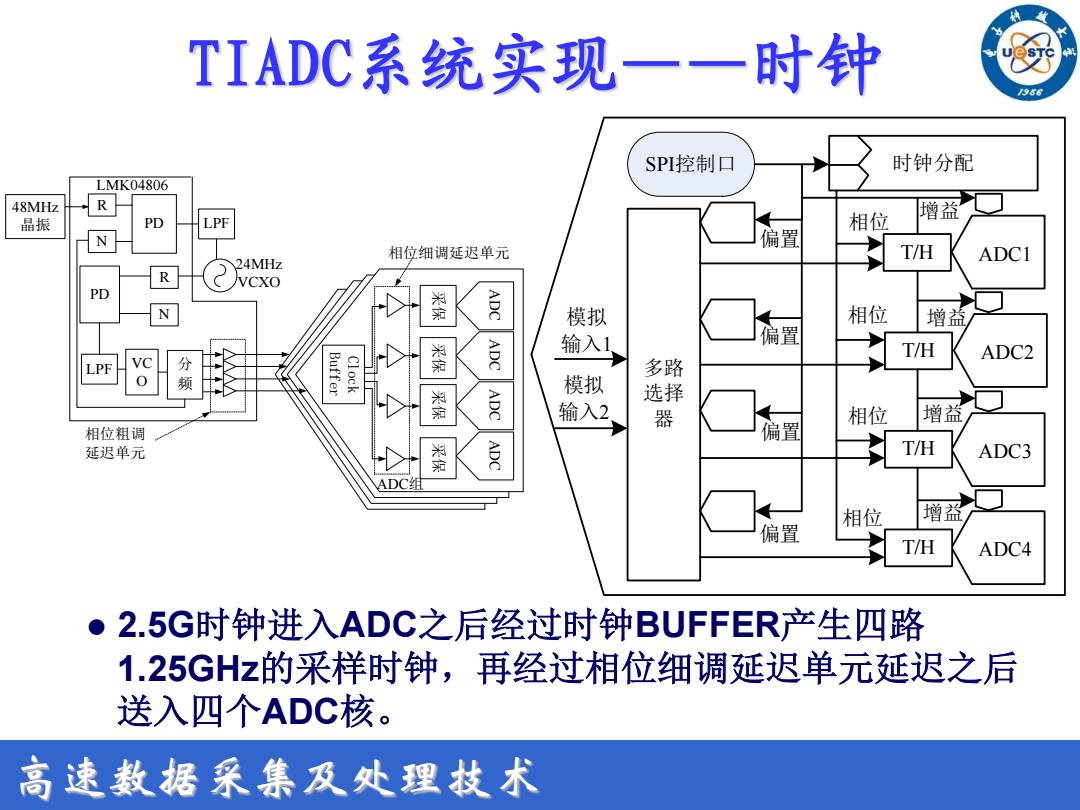

TIADC系统实现一一时钟 /956 SPI控制口 时钟分配 LMK04806 48MHz R 晶振 PD LPF 相位 增益 N 偏置 相位细调延迟单元 T/H ADCI 24MHz VCXO PD 模拟 相位 增益 偏置 ADC 输人 T/H ADC2 多路 模拟 选择 输入2 器 偏置 相位 增益 相位粗调 延迟单元 T/H ADC3 相位 增益 偏置 T/H ADC4 0 2.5G时钟进入ADC之后经过时钟BUFFER产生四路 1.25GHz的采样时钟,再经过相位细调延迟单元延迟之后 送入四个ADC核。 高速数据采集及处理技术

高速数据采集及处理技术 48MHz 晶振 R N LPF VC O ADC ADC ADC ADC 采保 采保 采保 采保 Clock Buffer 24MHz VCXO 分 频 ADC组 相位细调延迟单元 相位粗调 延迟单元 LMK04806 R PD LPF N PD 2.5G时钟进入ADC之后经过时钟BUFFER产生四路 1.25GHz的采样时钟,再经过相位细调延迟单元延迟之后 送入四个ADC核。 T/H ADC1 ADC2 ADC3 ADC4 多路 选择 器 SPI控制口 时钟分配 T/H T/H T/H 偏置 相位 增益 偏置 模拟 输入1 偏置 偏置 相位 相位 相位 增益 增益 增益 模拟 输入2 TIADC系统实现——时钟

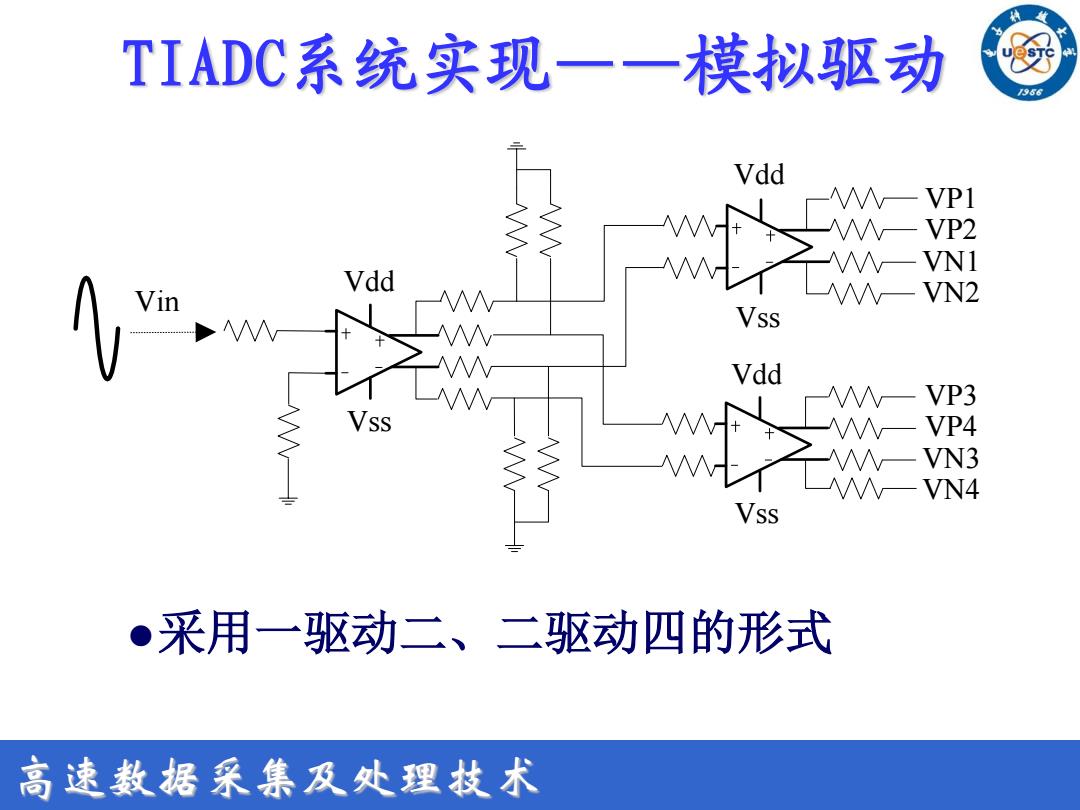

TIADC系统实现一一模拟驱动 Vdd - VP1 VP2 VNI Vdd VN2 Vdd VP3 SS VP4 VN3 VN4 Vss ·采用一驱动二、二驱动四的形式 高速数据采集及处理技术

高速数据采集及处理技术 采用一驱动二、二驱动四的形式 TIADC系统实现——模拟驱动 Vdd Vss Vdd Vss Vdd Vss VP1 VP2 VN1 VN2 VP3 VP4 VN3 VN4 Vin

/956 中国百篇最具影响国内学术论文 (2017) 论文题目: 基于T1ADC的20GS/s高速数据采集系统 来源期刊: 仪器仪表学报,2014,35(04):841-849 论文作者: 杨扩军 所属机构: 电子科技大学 被引次数: 26 经学术计量指标综合评定,该论文荣获2017年度“中国百篇 最具影响国内学术论文”,特此证明 中 城术信 0181 中国等技术信息密 Institute of Scientific Techn nformabon of China ◇ 北京复兴路15号100038 www.istic.ac.cn 高速数据

高速数据采集及处理技术