/986 高速数据采集技术 并行同步技术

高速数据采集技术—— 并行同步技术

高速数据采集技术一并行同步技术 学习要点 >并行同步问题分析 采样同步、数据传输同步、存储处理同步 >并行同步的解决方案 采样时钟分配、多ADC复位同步、多通道数据 传输同步、多通道存储同步

学习要点 高速数据采集技术—并行同步技术 并行同步问题分析 采样同步、数据传输同步、存储处理同步 并行同步的解决方案 采样时钟分配、多ADC复位同步、多通道数据 传输同步、多通道存储同步

高速数据采集技术一并行同步技术 并行同步问题 >高速并行采样系统的特点 > 强实时性:实时采样、实时存储、实时处理和显示 >高并行性: 多ADC阵列、多时钟处理 采样同步 >多处理器:多FPGA、多控制器 传输同步 >误差分散化:并行失配误姜 存储同步

并行同步问题 高速数据采集技术—并行同步技术 高速并行采样系统的特点 强实时性:实时采样、实时存储、实时处理和显示 高并行性:多ADC阵列、多时钟处理 多处理器:多FPGA、多控制器 误差分散化:并行失配误差 采样同步 传输同步 存储同步

高速数据采集技术一并行同步技术 并行同步问题 >并行采样同步 g[n] 1 多路采样时钟需 ADC1 满足特定的相位 P1=0 x(1 g2[n] ADC2 yn] 关系 P2=2π/W 模拟驱动需确保 8w[m] 信号至多个ADC ADCN 的延迟时间一致 N= 2π(N-1)/N 采样时钟产生与分配

并行同步问题 高速数据采集技术—并行同步技术 并行采样同步 ① 多路采样时钟需 满足特定的相位 关系 ② 模拟驱动需确保 信号至多个ADC 的延迟时间一致 x t( ) 1 g n[ ] 2 g n[ ] [ ] g n N ... y n[ ] 信号调理通道 波形重建与显示 ADC1 ADC2 ADCN 数据组合与处理 采样时钟产生与分配 1 0 2 2 / N 2 ( 1) / N N N

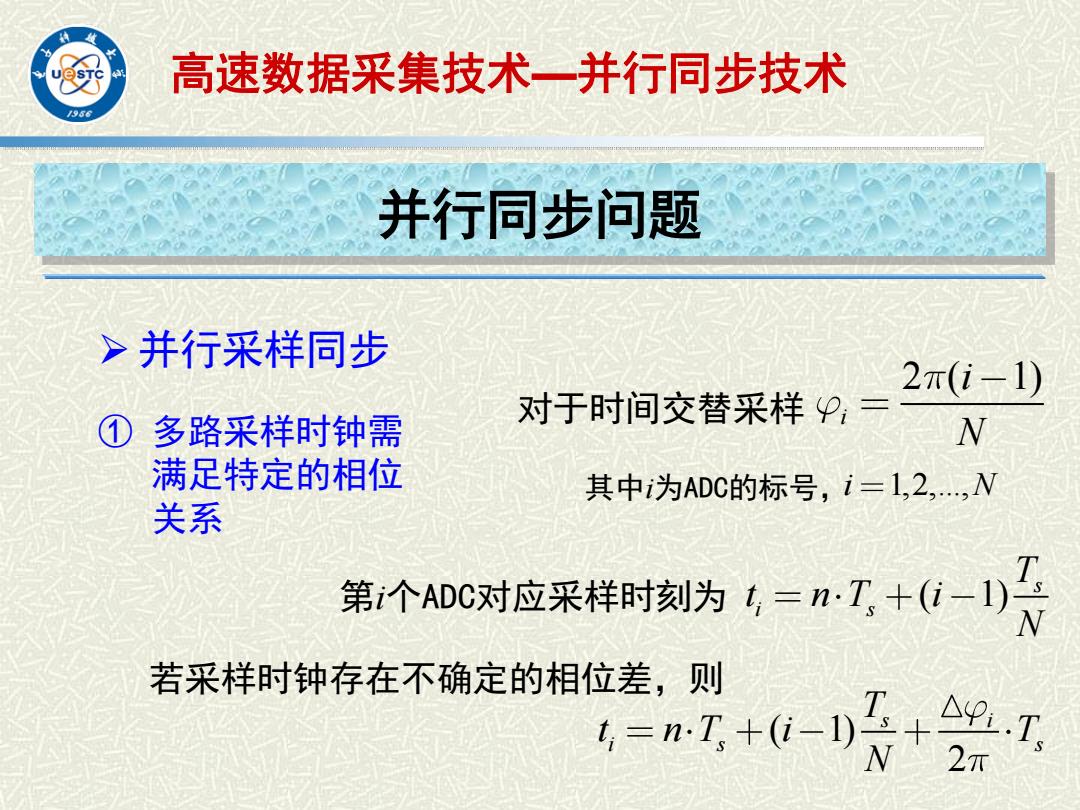

高速数据采集技术一并行同步技术 并行同步问题 >并行采样同步 2π(i-1) 对于时间交替采样P:= ① 多路采样时钟需 W 满足特定的相位 其中为ADC的标号,i=1,2,.,N 关系 个A0G应采为三n:T士- 若采样时钟存在不确定的相位差,则 =n:I+-1+p.1 2π

并行同步问题 高速数据采集技术—并行同步技术 并行采样同步 ① 多路采样时钟需 满足特定的相位 关系 2 ( 1) i i N 对于时间交替采样 其中i为ADC的标号, i N 1,2,..., ( 1) s i s T t n T i N 第i个ADC对应采样时刻为 若采样时钟存在不确定的相位差,则 ( 1) 2 s i i s s T t n T i T N

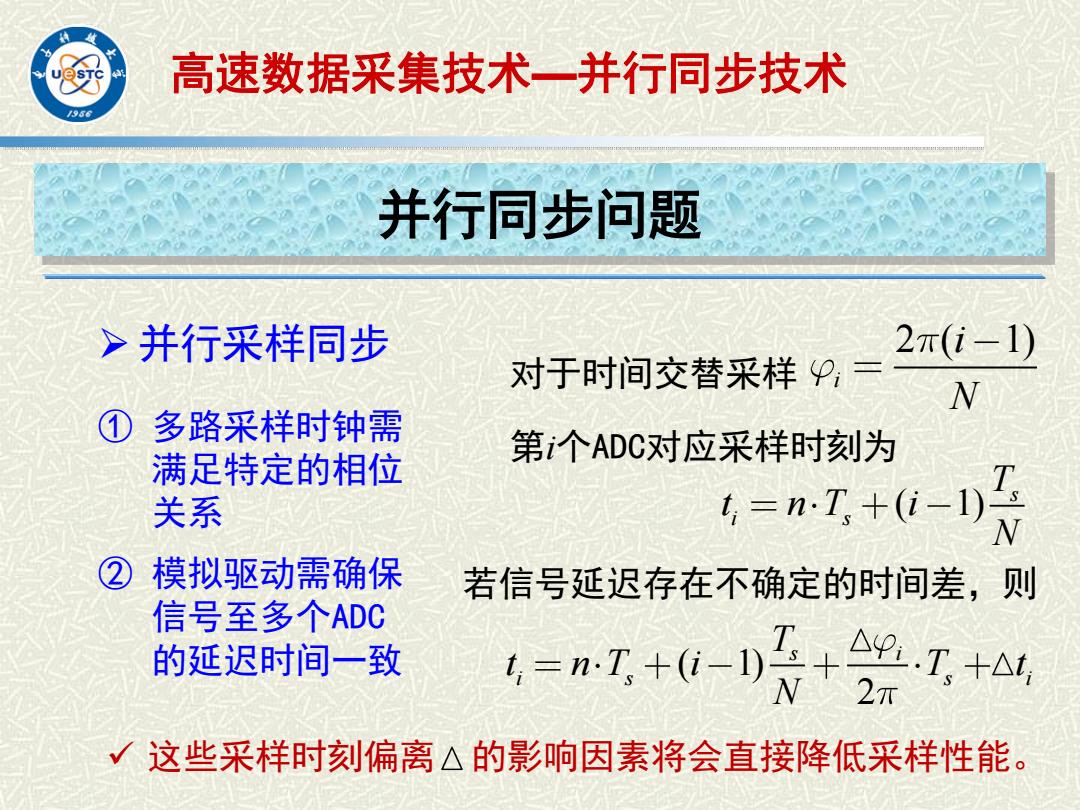

高速数据采集技术一并行同步技术 198 并行同步问题 >并行采样同步 2π(i-1) 对于时间交替采样P, W 多路采样时钟需 第i个ADC对应采样时刻为 满足特定的相位 关系 t,=nT,+(i-1) 2 模拟驱动需确保 若信号延迟存在不确定的时间差,则 信号至多个ADC 的延迟时间一致 三n-1+悦 94.T,+△1 2元 √这些采样时刻偏离△的影响因素将会直接降低采样性能

并行同步问题 高速数据采集技术—并行同步技术 并行采样同步 ① 多路采样时钟需 满足特定的相位 关系 ② 模拟驱动需确保 信号至多个ADC 的延迟时间一致 2 ( 1) i i N 对于时间交替采样 若信号延迟存在不确定的时间差,则 ( 1) s i s T t n T i N ( 1) 2 s i i s s i T t n T i T t N 这些采样时刻偏离 的影响因素将会直接降低采样性能。 第i个ADC对应采样时刻为

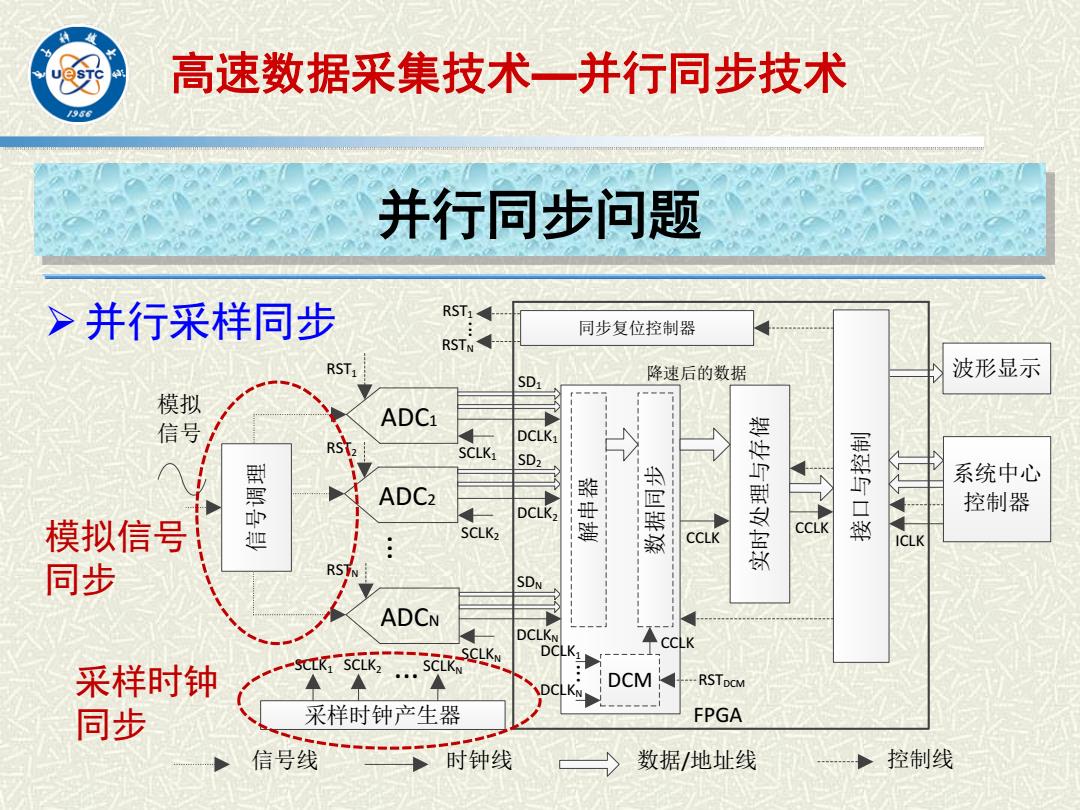

高速数据采集技术一并行同步技术 并行同步问题 >并行采样同步 RST1 同步复位控制器 RSTN RST1 降速后的数据 波形显示 SDi 模拟 ADC1 信号 DCLK RS SCLK1 SD2 系统中心 ADC2 DCLK2 控制器 模拟信号 SCLK2 ICLK 同步 RSTN SDN ADCN DCLK SCTK:SCLK, DCLK] CCLK 采样时钟 DCL DCM RSTDCM 同步 采样时钟产生器 FPGA 信号线 时钟线 数据/地址线 控制线

并行同步问题 高速数据采集技术—并行同步技术 并行采样同步 ADC1 ADC2 采样时钟产生器 SCLK1 SCLK2 模拟 信号 信号线 时钟线 数据/地址线 实时处理与存 DCLK1 储 DCLK2 SD1 SD2 降速后的数据 同步复位控制器 ADCN SCLKN SDN ... CCLK DCLKN ... 系统中心 控制器 接口与控制 ICLK FPGA 控制线 SCLK1 SCLK2 SCLKN DCM RSTN RST2 RST1 CCLK RST1 RSTN ... 解串器 数据同步 波形显示 信号调理 RSTDCM CCLK DCLK1 DCLKN .. 采样时钟 . 同步 模拟信号 同步

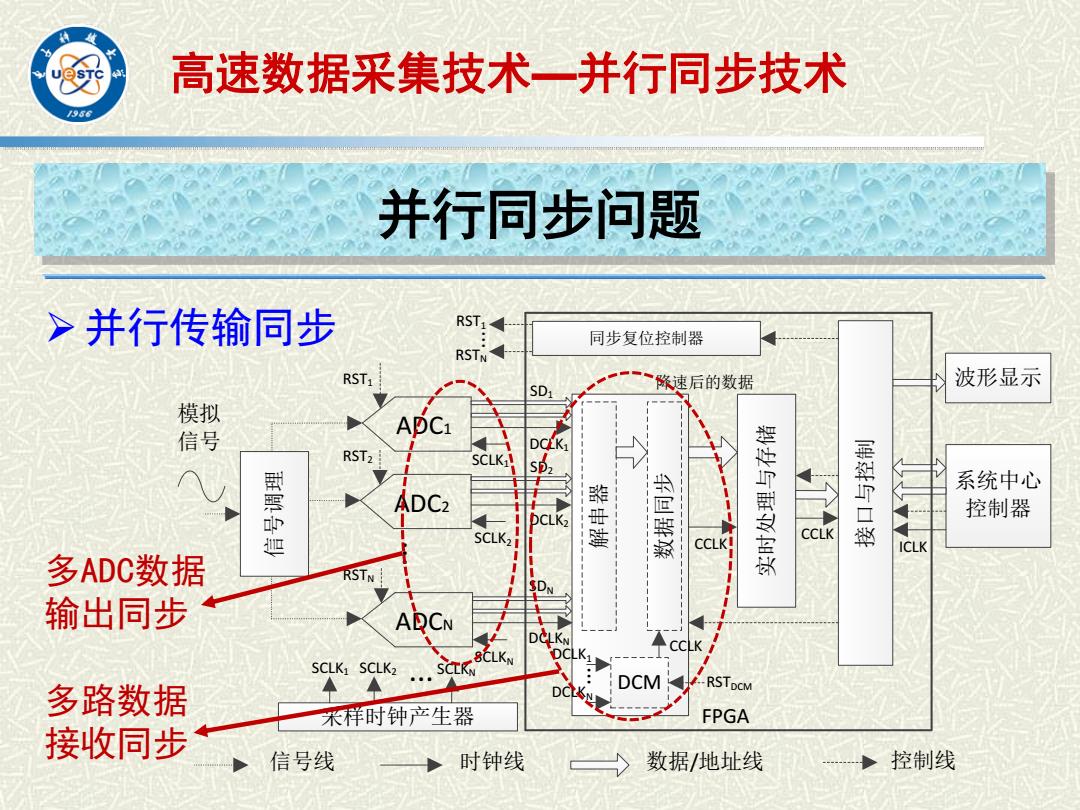

高速数据采集技术一并行同步技术 并行同步问题 >并行传输同步 RST1 同步复位控制器 RSTN RST 除速后的数据 波形显示 SD 模拟 ApCi 信号 RST2 LK 系统中心 ADC2 控制器 CCLK CCLK ICLK 多ADC数据 RSTN 输出同步 ADCN 8CLKN SCLK:SCLK2 DCM 多路数据 RSTDCM 米样时钟产生器 FPGA 接收同步 信号线 时钟线 数据/地址线 控制线

并行同步问题 高速数据采集技术—并行同步技术 并行传输同步 ADC1 ADC2 采样时钟产生器 SCLK1 SCLK2 模拟 信号 信号线 时钟线 数据/地址线 实时处理与存 DCLK1 储 DCLK2 SD1 SD2 降速后的数据 同步复位控制器 ADCN SCLKN SDN ... CCLK DCLKN ... 系统中心 控制器 接口与控制 ICLK FPGA 控制线 SCLK1 SCLK2 SCLKN DCM RSTN RST2 RST1 CCLK RST1 RSTN ... 解串器 数据同步 波形显示 信号调理 RSTDCM CCLK DCLK1 DCLKN ... 多ADC数据 输出同步 多路数据 接收同步

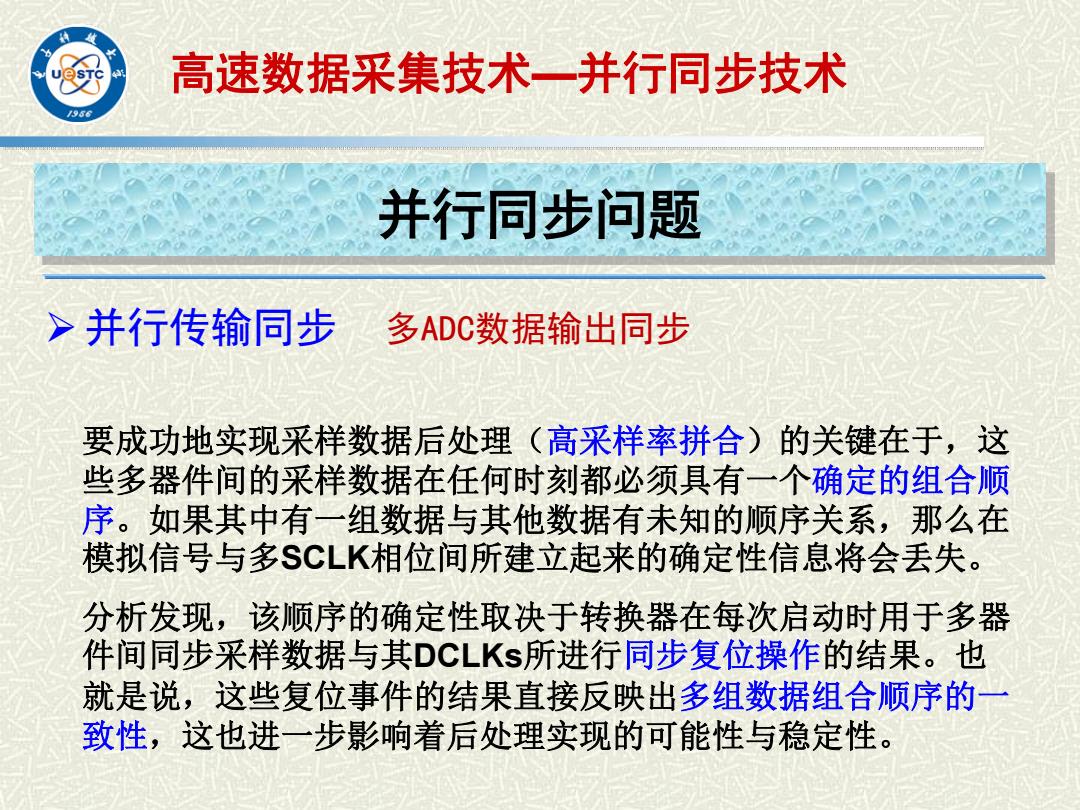

高速数据采集技术一并行同步技术 /96 并行同步问题 >并行传输同步 多ADC数据输出同步 要成功地实现采样数据后处理(高采样率拼合)的关键在于,这 些多器件间的采样数据在任何时刻都必须具有一个确定的组合顺 序。如果其中有一组数据与其他数据有未知的顺序关系,那么在 模拟信号与多SCLK相位间所建立起来的确定性信息将会丢失。 分析发现,该顺序的确定性取决于转换器在每次启动时用于多器 件间同步采样数据与其DCLKs所进行同步复位操作的结果。也 就是说,这些复位事件的结果直接反映出多组数据组合顺序的 致性,这也进一步影响着后处理实现的可能性与稳定性

并行同步问题 高速数据采集技术—并行同步技术 并行传输同步 多ADC数据输出同步 要成功地实现采样数据后处理(高采样率拼合)的关键在于,这 些多器件间的采样数据在任何时刻都必须具有一个确定的组合顺 序。如果其中有一组数据与其他数据有未知的顺序关系,那么在 模拟信号与多SCLK相位间所建立起来的确定性信息将会丢失。 分析发现,该顺序的确定性取决于转换器在每次启动时用于多器 件间同步采样数据与其DCLKs所进行同步复位操作的结果。也 就是说,这些复位事件的结果直接反映出多组数据组合顺序的一 致性,这也进一步影响着后处理实现的可能性与稳定性

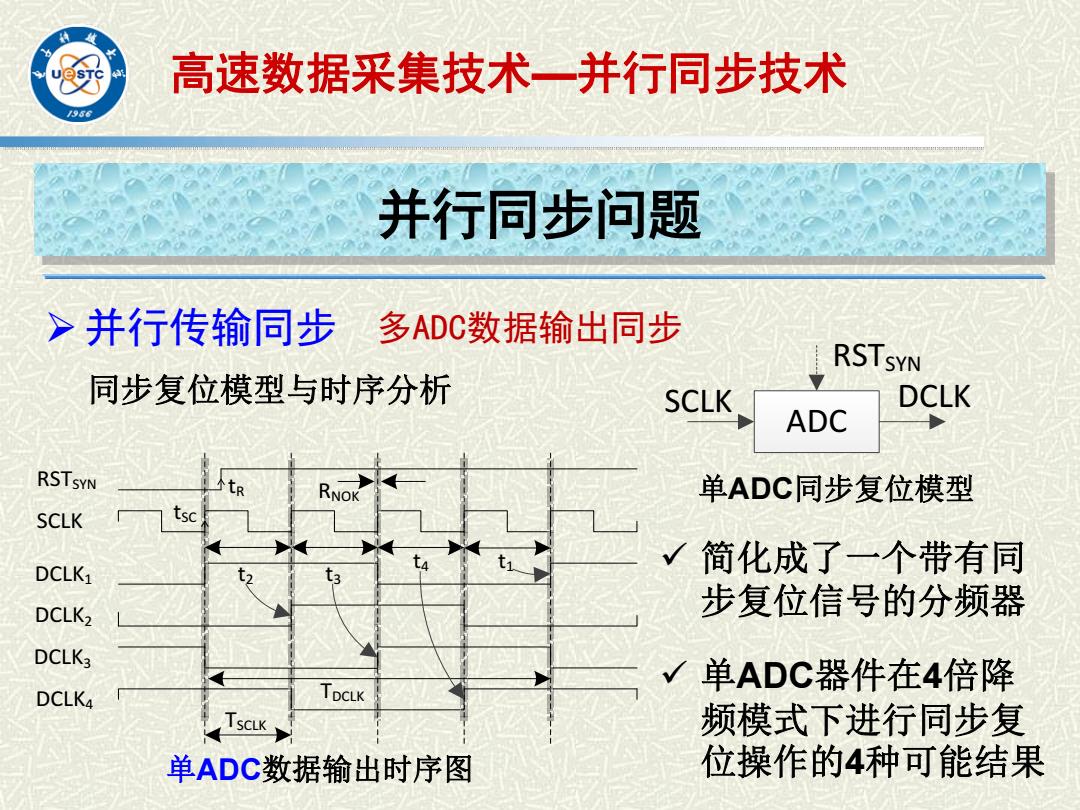

高速数据采集技术一并行同步技术 并行同步问题 >并行传输同步 多ADC数据输出同步 RSTSYN 同步复位模型与时序分析 SCLK DCLK ADC RSTsYN 单ADC同步复位模型 SCLK DCLK1 简化成了一个带有同 DCLK2 步复位信号的分频器 DCLK3 单ADC器件在4倍降 DCLK4 TDCLK SCLK 频模式下进行同步复 单ADC数据输出时序图 位操作的4种可能结果

并行同步问题 高速数据采集技术—并行同步技术 并行传输同步 多ADC数据输出同步 单ADC同步复位模型 ADC SCLK DCLK RSTSYN 同步复位模型与时序分析 SCLK RSTSYN DCLK1 DCLK2 TSCLK TDCLK tR tSC DCLK3 DCLK4 t1 t2 t3 t4 RNOK 单ADC数据输出时序图 单ADC器件在4倍降 频模式下进行同步复 位操作的4种可能结果 简化成了一个带有同 步复位信号的分频器