电子科皮女学 University of Electrsic Science and Technology China 高速数据朵集 及处理技术 第五章 数据传输与处理技术

第五章 数据传输与处理技术 高速数据采集 及处理技术

前言 >抽样率转换问题 为什么要作抽样率转换? >1、信号原来的抽样频率不合适。 如抽样频率过高,数据量太大: 存储量大,计算负担重,传输时需要大的带宽。 >2、实际数字系统中,不同的处理环节需求不同的 抽样频率

前言 抽样率转换问题 一、为什么要作抽样率转换? 1、信号原来的抽样频率不合适。 如抽样频率过高,数据量太大: 存储量大,计算负担重,传输时需要大的带宽。 2、实际数字系统中,不同的处理环节需求不同的 抽样频率

7 例如: 在音频世界里,就存在着多种抽样频率。得到 立体声信号(Studio work)所有的抽样频率是 48kHz,CD产品用的抽样率是44.1kHz,而数字音频 广播用的是32kHz。 同一首音乐,从录音、制作成CD唱盘到数字音 频广播,抽样频率要多次变化。 再例如: 当需要将数字信号在两个或多个具有独立时钟 的数字系统之间传递时,则要求该数字信号的抽样率 要能根据时钟的不同而转换

例如: 在音频世界里,就存在着多种抽样频率。得到 立体声信号(Studio work)所有的抽样频率是 48kHz,CD产品用的抽样率是44.1kHz,而数字音频 广播用的是32kHz。 同一首音乐,从录音、制作成CD唱盘到数字音 频广播,抽样频率要多次变化。 再例如: 当需要将数字信号在两个或多个具有独立时钟 的数字系统之间传递时,则要求该数字信号的抽样率 要能根据时钟的不同而转换

66 >二、如何实现抽样率的转换 >1、对原来的模拟信号重新抽样; >20m→D/4→0→A/D→x(m)2 >3、基于原数学信号,用信号处理的方法实现抽样 率转换一抽取(Decimation)/插值 (Interpolation)

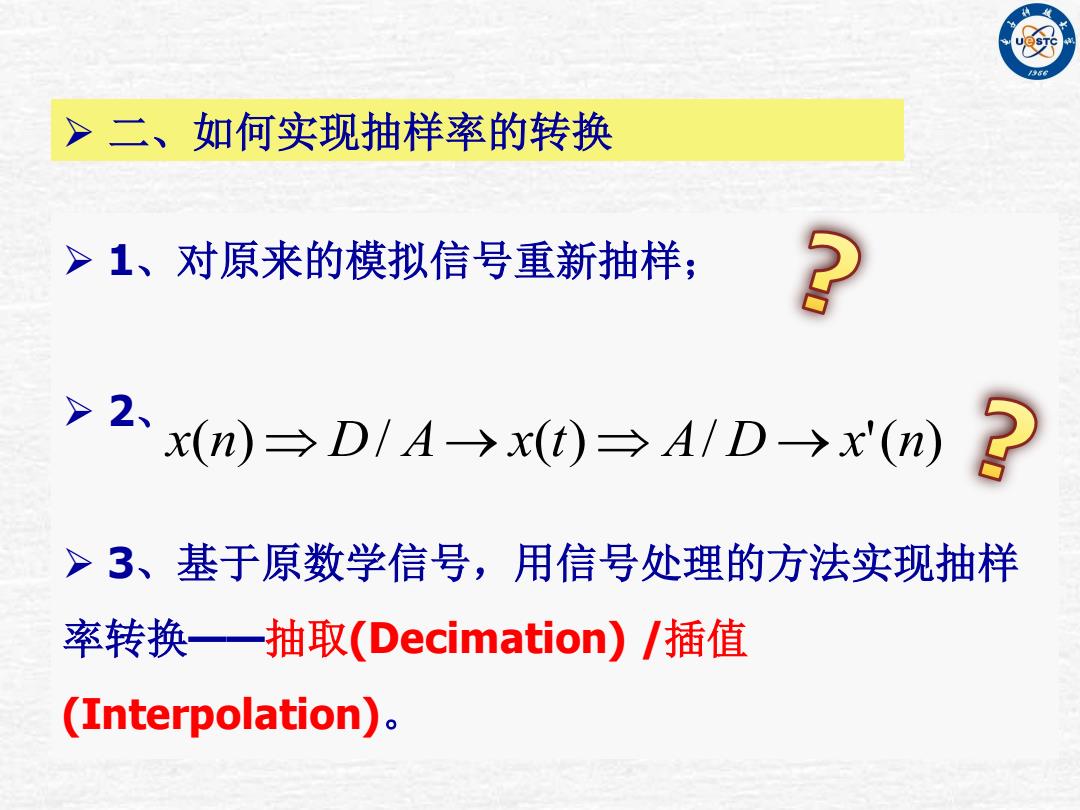

二、如何实现抽样率的转换 1、对原来的模拟信号重新抽样; 2、 3、基于原数学信号,用信号处理的方法实现抽样 率转换——抽取(Decimation) /插值 (Interpolation)。 x(n) D/ A x(t) A/ D x'(n)

信号的抽取 >抽取: ,→f,/M 抽样频率减少M倍 x(n y(n IM Down-Sampler 最简单的方法是将()中每M个点中抽取一个,一 次组成一个新的序列,即: y(n)=x(Mn)

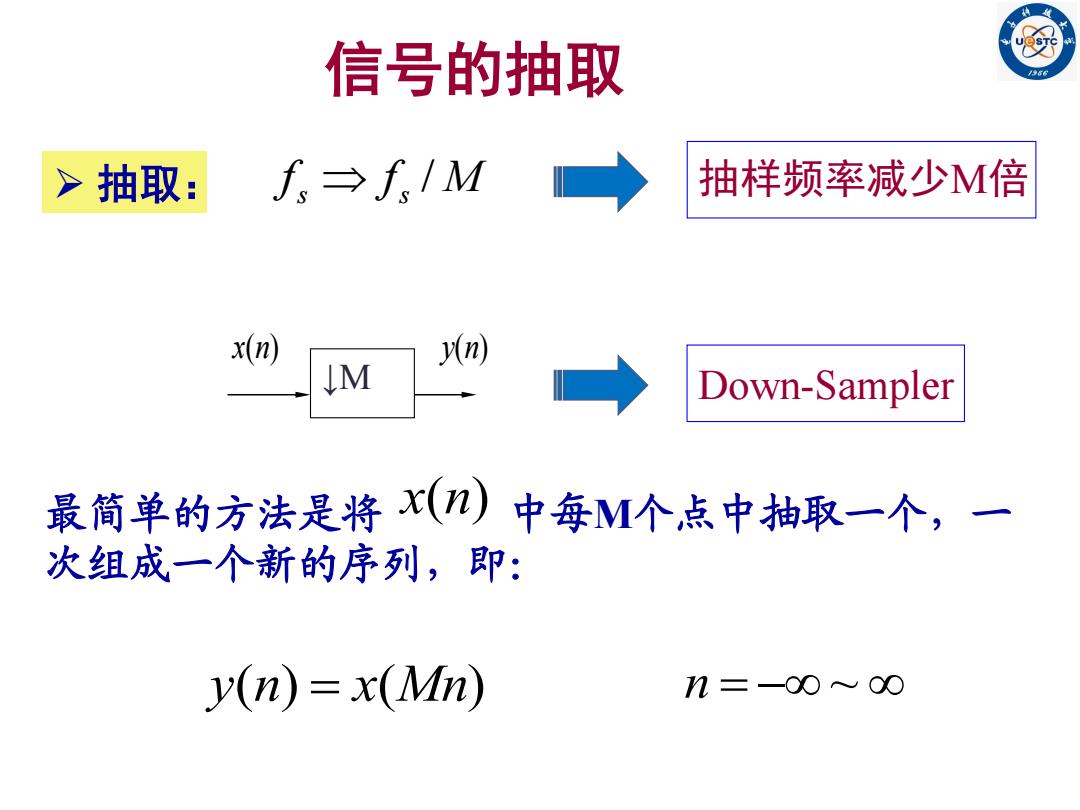

信号的抽取 抽取: f s f s / M 抽样频率减少M倍 ↓M x(n) y(n) Down-Sampler 最简单的方法是将 中每M个点中抽取一个,一 次组成一个新的序列,即: x(n) y(n) x(Mn) n ~

y(n)=x(Mn) n三-00~00 M=3 y(0)=x(0) y1①=x(3) y(2)=x(6 y(3)=x(9) 舍弃了(M-1)M部分的数据

y(n) x(Mn) n ~ M 3 y(0) x(0) y(1) x(3) y(2) x(6) y(3) x(9) 舍弃了(M-1)/M部分的数据 . . .

抽取的实现 抽取的实现 ()串行数据抽取的实现 (2)并行数据抽取的实现 -非均匀抽取产生的原因 一均匀抽取的实现

抽取的实现 抽取的实现 ⑴串行数据抽取的实现 ⑵并行数据抽取的实现 -非均匀抽取产生的原因 -均匀抽取的实现

串行数据抽取的实现 采用控制FIFO写使能的方式进行抽点 ADC 输出数据 ①X2X3X4X⑤X6X⑦X8X9X0X2X3X4X151617X18 FIFO 写使能 FIFO 实际存储 1 10 13 16 数据

串行数据抽取的实现 采用控制FIFO写使能的方式进行抽点 ADC 输出数据 FIFO 写使能 FIFO 实际存储 数据 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 ... 1 4 7 10 13 16

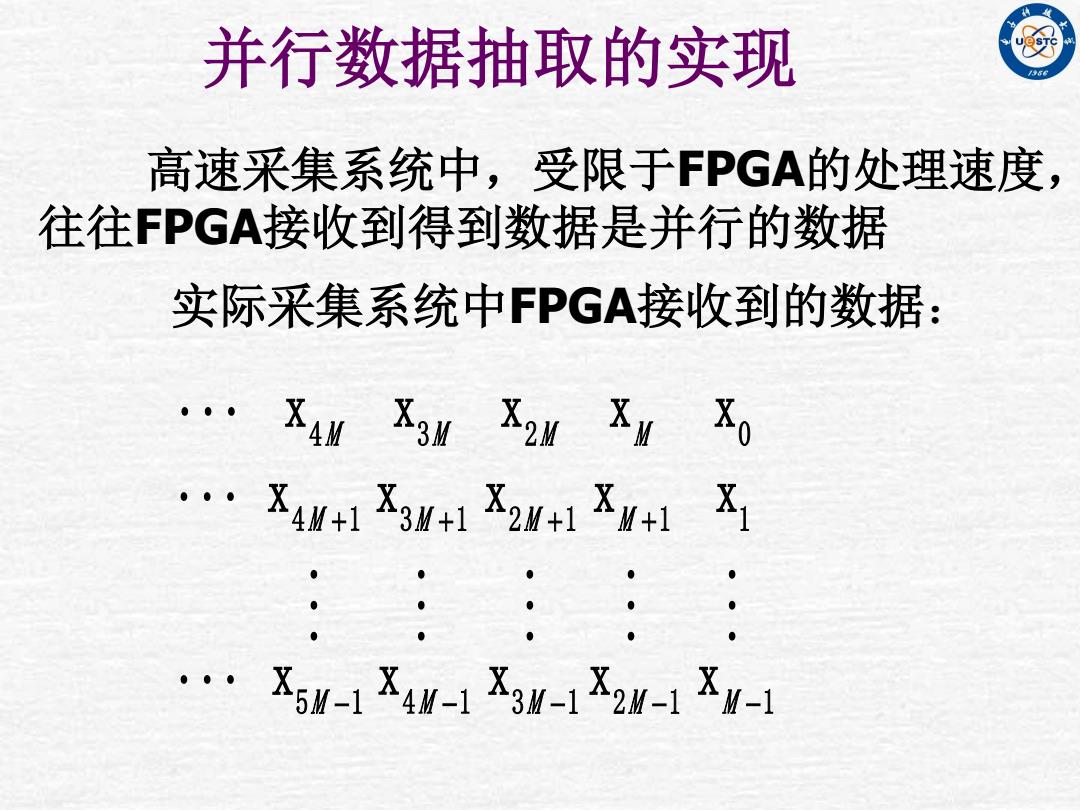

并行数据抽取的实现 高速采集系统中,受限于FPGA的处理速度, 往往FPGA接收到得到数据是并行的数据 实际采集系统中FPGA接收到的数据: X2M Xo ·X4W+1X3M+1X2M+1XM+181 ·: : -1X4M-1X3M-1X2M-1XM-1

高速采集系统中,受限于FPGA的处理速度, 往往FPGA接收到得到数据是并行的数据 实际采集系统中FPGA接收到的数据: 0 x x 2 M x 3 M x 4 M x M ... 1 x 1 x 2 1 M x 3 1 M x 4 1 M x M ... ... ... ... ... ... 1 x 2 1 M x 3 1 M x 4 1 M x 5 1 M x M ... 并行数据抽取的实现

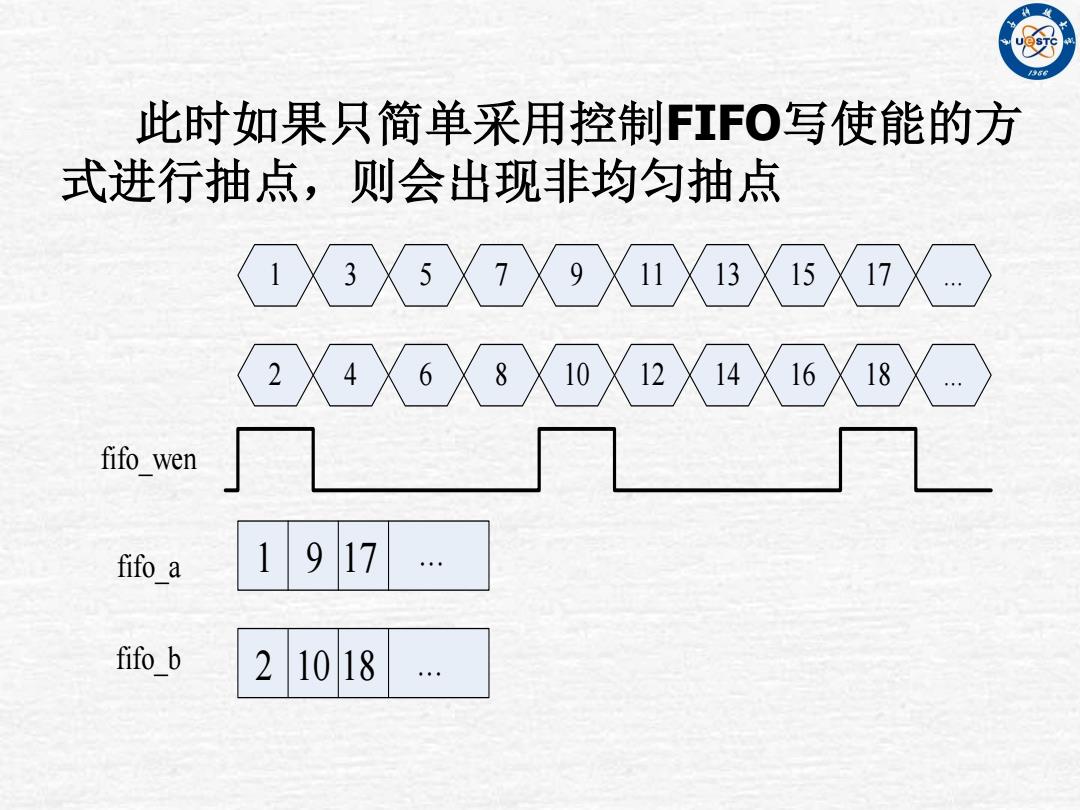

此时如果只简单采用控制FIFO写使能的方 式进行抽点,则会出现非均匀抽点 ①X3X5X⑦X9 XHB 17 2X4 8 10 12 14 16 18 fifo wen fifo a 1917 fifo b 21018

此时如果只简单采用控制FIFO写使能的方 式进行抽点,则会出现非均匀抽点 1 3 5 7 9 11 13 15 2 4 6 8 10 12 14 16 1 9 2 10 17 18 ... ... 17 18 ... ... fifo_wen fifo_a fifo_b