正在加载图片...

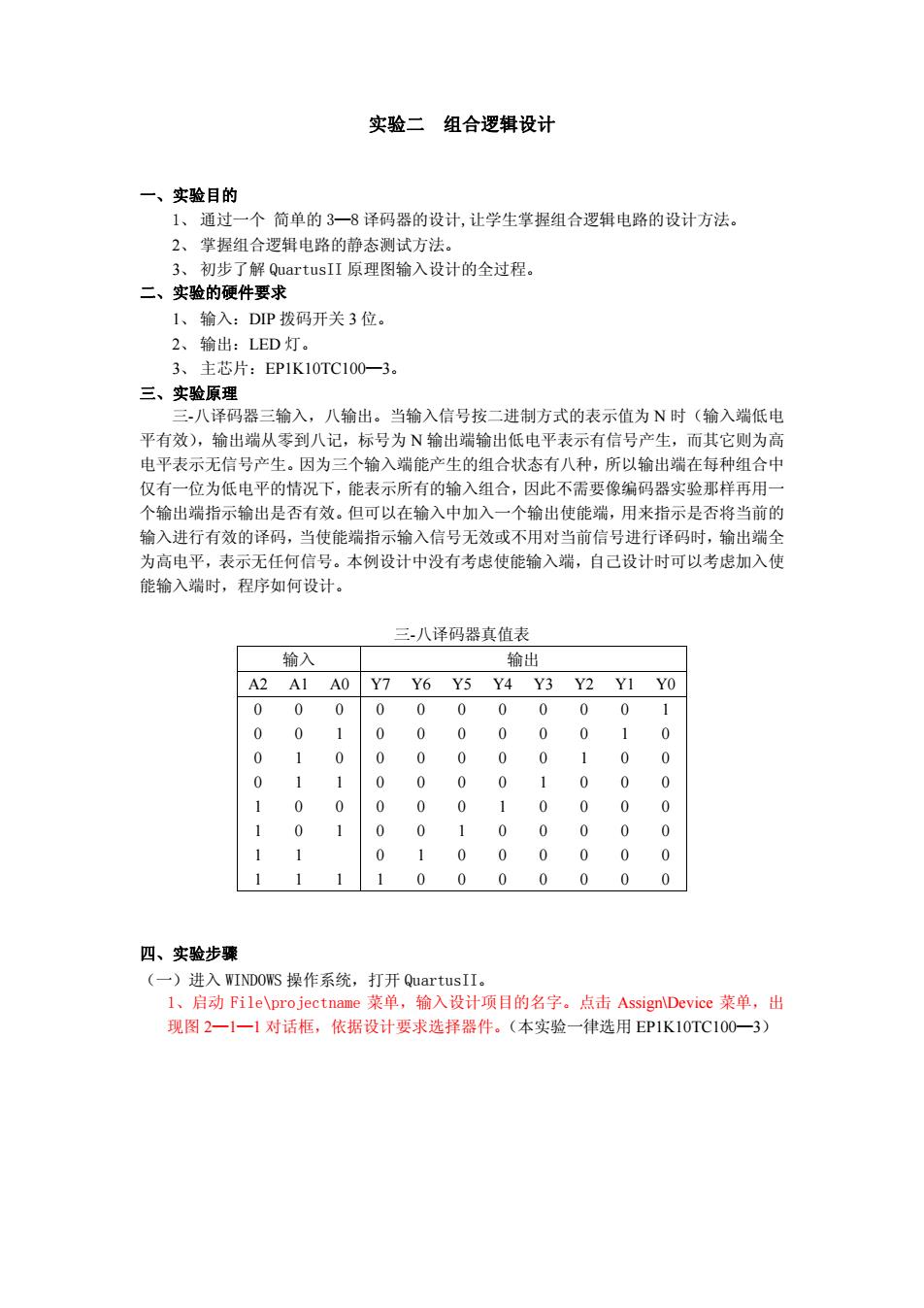

实验二组合逻辑设计 一、实验目的 1、通过一个简单的3一8译码器的设计,让学生掌握组合逻辑电路的设计方法。 2、掌握组合逻辑电路的静态测试方法。 3、初步了解QuartusII原理图输入设计的全过程。 二、实验的硬件要求 1、输入:DP拨码开关3位。 2、输出:LED灯。 3、主芯片:EP1K10TC100一3。 三、实验原理 三-八译码器三输入,八输出。当输入信号按二进制方式的表示值为N时(输入端低电 平有效),输出端从零到八记,标号为N输出端输出低电平表示有信号产生,而其它则为高 电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中 仅有一位为低电平的情况下,能表示所有的输入组合,因此不需要像编码器实验那样再用一 个输出端指示输出是否有效。但可以在输入中加入一个输出使能端,用来指示是否将当前的 输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全 为高电平,表示无任何信号。本例设计中没有考虑使能输入端,自己设计时可以考虑加入使 能输入端时,程序如何设计。 三-八译码器真值表 输入 输出 A2Al A0 Y7 Y6 Y5 Y4 Y3 Y2 YI YO 00 0 00000001 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 000 四、实验步骤 (一)进入WINDOWS操作系统,打开QuartusII。 1、启动File\projectname菜单,输入设计项目的名字。点击Assign\Device菜单,出 现图2一1一1对话框,依据设计要求选择器件。(本实验一律选用EP1K10TC100一3)实验二 组合逻辑设计 一、实验目的 1、 通过一个 简单的 3—8 译码器的设计,让学生掌握组合逻辑电路的设计方法。 2、 掌握组合逻辑电路的静态测试方法。 3、 初步了解 QuartusII 原理图输入设计的全过程。 二、实验的硬件要求 1、 输入:DIP 拨码开关 3 位。 2、 输出:LED 灯。 3、 主芯片:EP1K10TC100—3。 三、实验原理 三-八译码器三输入,八输出。当输入信号按二进制方式的表示值为 N 时(输入端低电 平有效),输出端从零到八记,标号为 N 输出端输出低电平表示有信号产生,而其它则为高 电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中 仅有一位为低电平的情况下,能表示所有的输入组合,因此不需要像编码器实验那样再用一 个输出端指示输出是否有效。但可以在输入中加入一个输出使能端,用来指示是否将当前的 输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全 为高电平,表示无任何信号。本例设计中没有考虑使能输入端,自己设计时可以考虑加入使 能输入端时,程序如何设计。 三-八译码器真值表 输入 输出 A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 1 1 0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 四、实验步骤 (一)进入 WINDOWS 操作系统,打开 QuartusII。 1、启动 File\projectname 菜单,输入设计项目的名字。点击 Assign\Device 菜单,出 现图 2—1—1 对话框,依据设计要求选择器件。(本实验一律选用 EP1K10TC100—3)