实验二组合逻辑设计 一、实验目的 1、通过一个简单的3一8译码器的设计,让学生掌握组合逻辑电路的设计方法。 2、掌握组合逻辑电路的静态测试方法。 3、初步了解QuartusII原理图输入设计的全过程。 二、实验的硬件要求 1、输入:DP拨码开关3位。 2、输出:LED灯。 3、主芯片:EP1K10TC100一3。 三、实验原理 三-八译码器三输入,八输出。当输入信号按二进制方式的表示值为N时(输入端低电 平有效),输出端从零到八记,标号为N输出端输出低电平表示有信号产生,而其它则为高 电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中 仅有一位为低电平的情况下,能表示所有的输入组合,因此不需要像编码器实验那样再用一 个输出端指示输出是否有效。但可以在输入中加入一个输出使能端,用来指示是否将当前的 输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全 为高电平,表示无任何信号。本例设计中没有考虑使能输入端,自己设计时可以考虑加入使 能输入端时,程序如何设计。 三-八译码器真值表 输入 输出 A2Al A0 Y7 Y6 Y5 Y4 Y3 Y2 YI YO 00 0 00000001 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 000 四、实验步骤 (一)进入WINDOWS操作系统,打开QuartusII。 1、启动File\projectname菜单,输入设计项目的名字。点击Assign\Device菜单,出 现图2一1一1对话框,依据设计要求选择器件。(本实验一律选用EP1K10TC100一3)

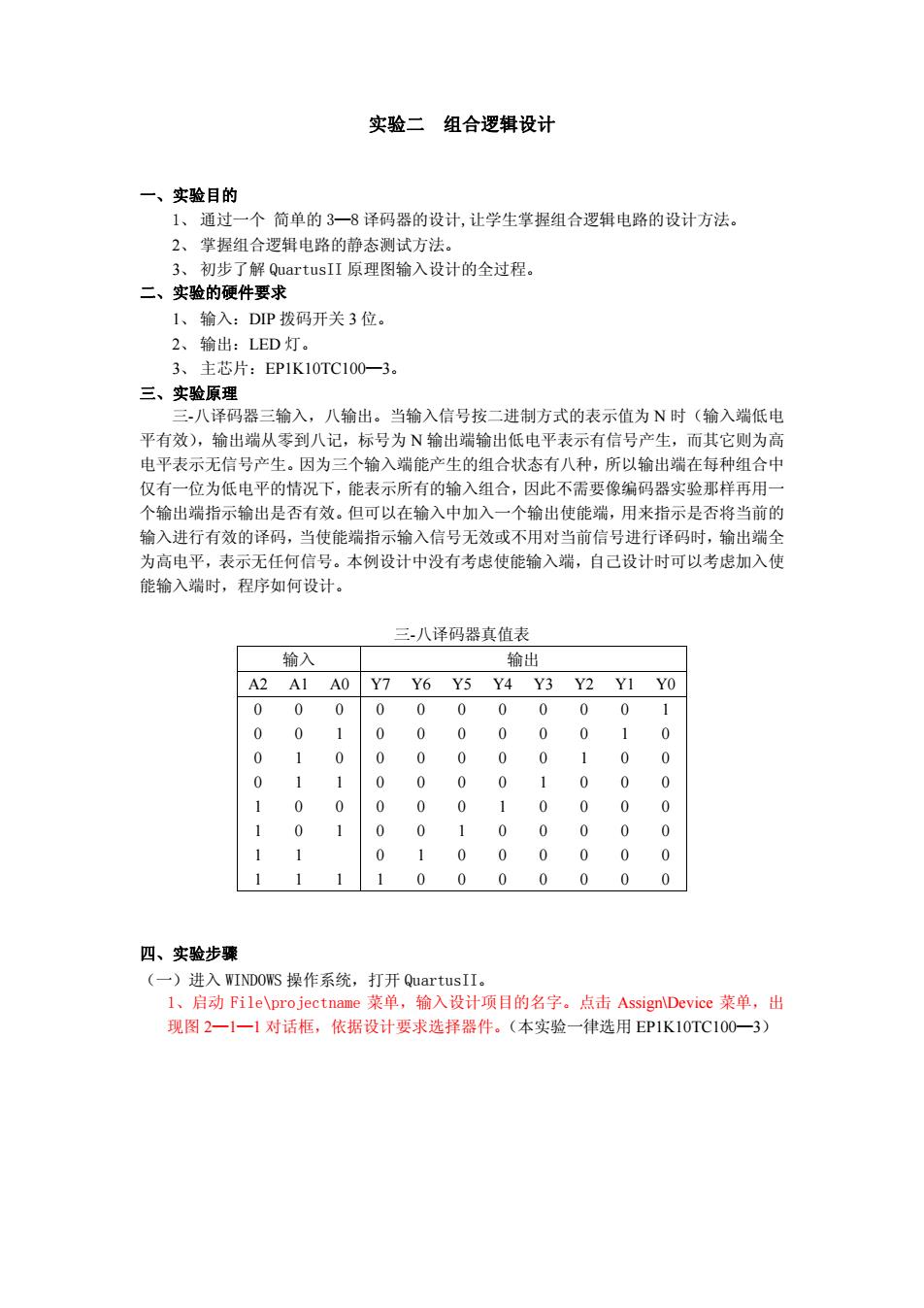

实验二 组合逻辑设计 一、实验目的 1、 通过一个 简单的 3—8 译码器的设计,让学生掌握组合逻辑电路的设计方法。 2、 掌握组合逻辑电路的静态测试方法。 3、 初步了解 QuartusII 原理图输入设计的全过程。 二、实验的硬件要求 1、 输入:DIP 拨码开关 3 位。 2、 输出:LED 灯。 3、 主芯片:EP1K10TC100—3。 三、实验原理 三-八译码器三输入,八输出。当输入信号按二进制方式的表示值为 N 时(输入端低电 平有效),输出端从零到八记,标号为 N 输出端输出低电平表示有信号产生,而其它则为高 电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中 仅有一位为低电平的情况下,能表示所有的输入组合,因此不需要像编码器实验那样再用一 个输出端指示输出是否有效。但可以在输入中加入一个输出使能端,用来指示是否将当前的 输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全 为高电平,表示无任何信号。本例设计中没有考虑使能输入端,自己设计时可以考虑加入使 能输入端时,程序如何设计。 三-八译码器真值表 输入 输出 A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 1 1 0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 四、实验步骤 (一)进入 WINDOWS 操作系统,打开 QuartusII。 1、启动 File\projectname 菜单,输入设计项目的名字。点击 Assign\Device 菜单,出 现图 2—1—1 对话框,依据设计要求选择器件。(本实验一律选用 EP1K10TC100—3)

图2一1一1 2、启动菜单File\New,选择Graphic Editor File,打开原理图编辑器,进行原理图设计 输入如图2一1一2。 图2一1一2 (二)设计输入 1、放置一个器件在原理图上。 在原理图的空白处双击鼠标左键,出现图2一1一3: 图2一1一3 在光标处输入元件名称或用鼠标点击元件,按下OK即可。 如果安放相同元件,只要按住CTL键,同时用鼠标拖动该元件。 图2一1一4为元件安放结果。 aA二 ▣一装 3

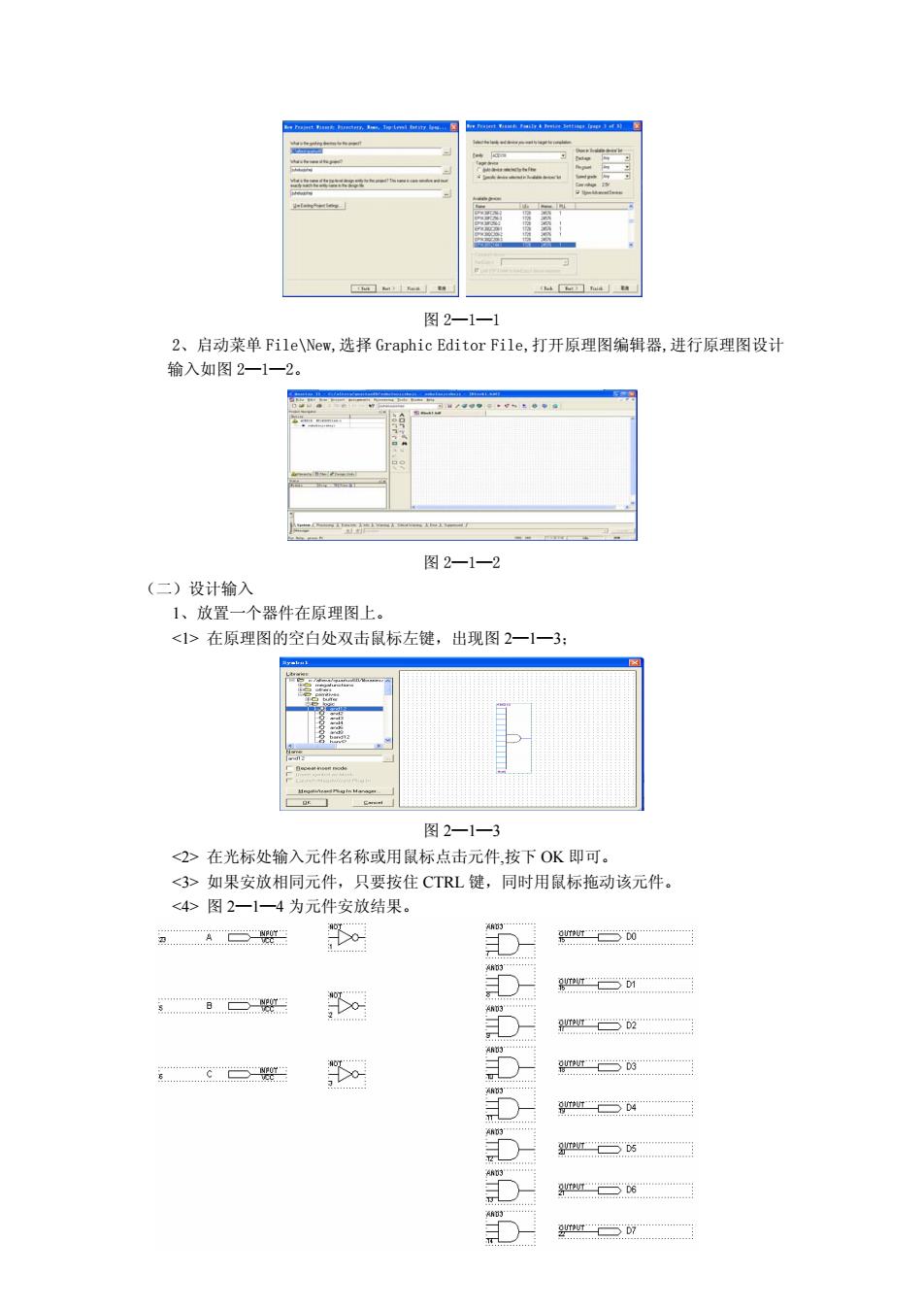

图 2—1—1 2、启动菜单 File\New,选择 Graphic Editor File,打开原理图编辑器,进行原理图设计 输入如图 2—1—2。 图 2—1—2 (二)设计输入 1、放置一个器件在原理图上。 在原理图的空白处双击鼠标左键,出现图 2—1—3; 图 2—1—3 在光标处输入元件名称或用鼠标点击元件,按下 OK 即可。 如果安放相同元件,只要按住 CTRL 键,同时用鼠标拖动该元件。 图 2—1—4 为元件安放结果

图2一1一4 2、添加连线到器件的管脚上。 把鼠标移到引脚附近,则鼠标光标自动由箭头变位十字,按住鼠标左键拖动,即可画出 连线.如图2一1一5示 滴制0的4 2A 0r例rSD0 1 BUTPUT D1 B “的中: 0 训0的 00r5D2 圳的 0rr二D3 钢的 0rr二D4 的” UTUrD6 0的 ouTur D7 图2一1一5 3、保存原理图 单击保存按扭,对于第一次输入的新原理图,出现类似文件管理器的图框,选择合适目 录,合适名称保存刚才输入的原理图2一1一5原理图的扩展名为.gdf,本实验取名test1gdf。 (三)完成了原理图的输入后,我们就可以用第二部分介绍的软件的使用方法,对程序进行 管脚的定义、编译、仿真、下载,完成整个实验的设计。 五、实验电路连接与实验结果 用拨码开关的低三位代表译码器的输入(A,B,C),将之与EP1K10TC100一3的管脚 相连:用LED灯来表示译码器的输出(D0~D7),将之与EP1K10TC100一3芯片的管脚相 连。拨动拨档开关,可以观察发光二极管与输入状态的对应关系同真值表中所描述的情况是 一致的。 六、实验报告与思考 1)在输入端加入使能端后应如何设计。 2)输入信号是按格雷码方式的编码时,译码器如何设计。 3)设计与T1138功能类似的数据分配器。 附:用硬件描述语言完成译码器的设计: (1)、生成设计项目文件。 (2)、启动File\New菜单命令,如图2一1一10:

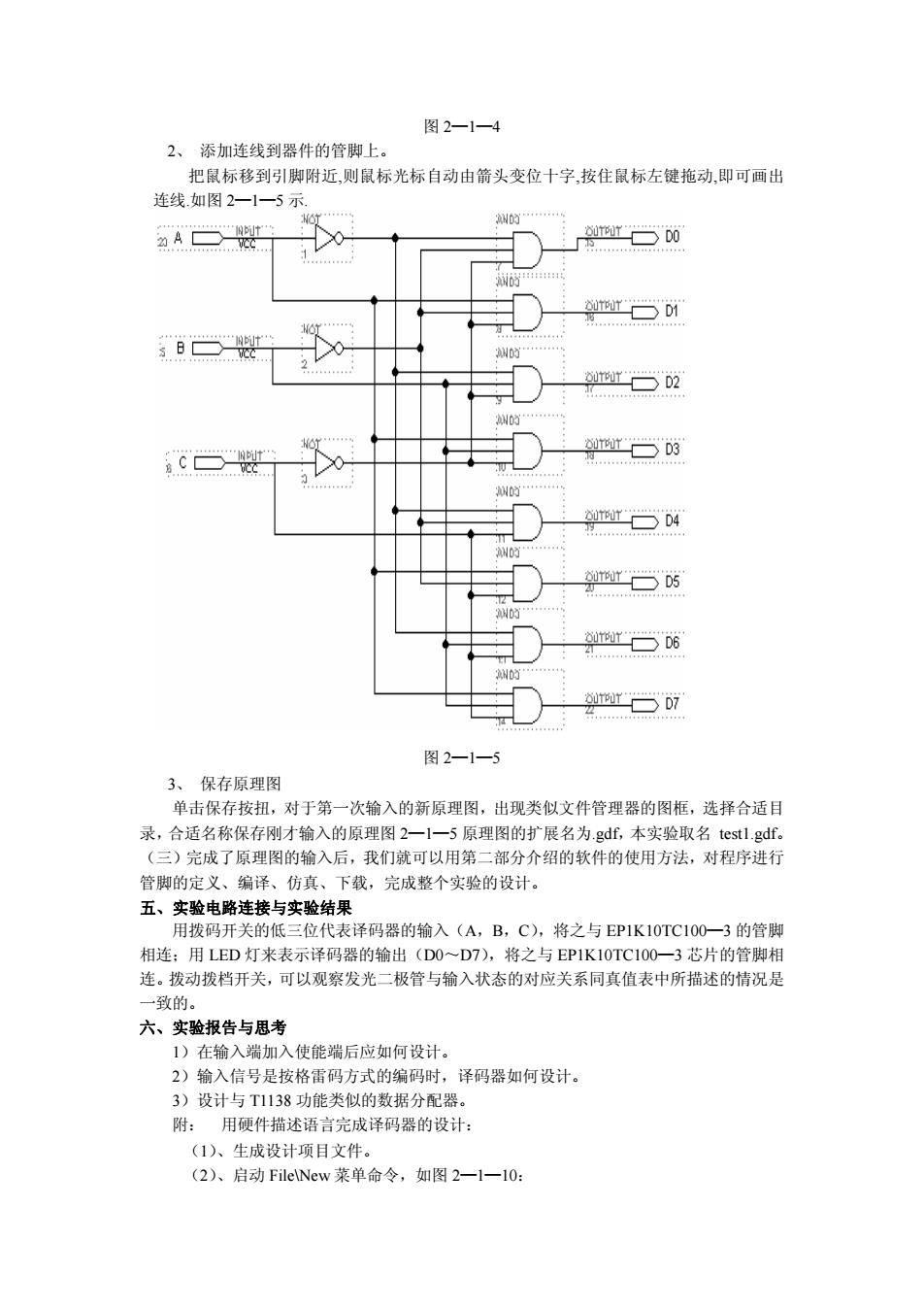

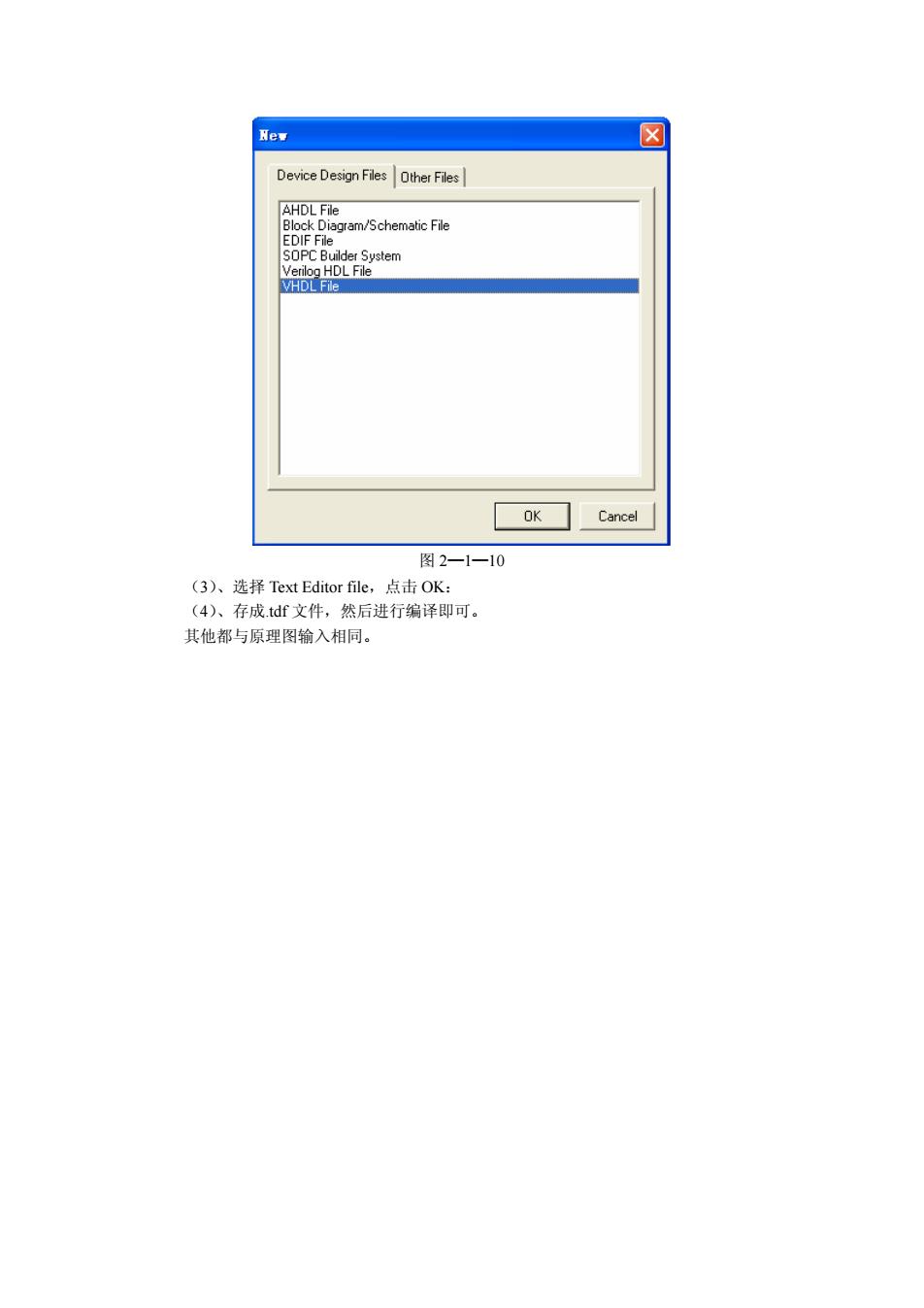

图 2—1—4 2、 添加连线到器件的管脚上。 把鼠标移到引脚附近,则鼠标光标自动由箭头变位十字,按住鼠标左键拖动,即可画出 连线.如图 2—1—5 示. 图 2—1—5 3、 保存原理图 单击保存按扭,对于第一次输入的新原理图,出现类似文件管理器的图框,选择合适目 录,合适名称保存刚才输入的原理图 2—1—5 原理图的扩展名为.gdf,本实验取名 test1.gdf。 (三)完成了原理图的输入后,我们就可以用第二部分介绍的软件的使用方法,对程序进行 管脚的定义、编译、仿真、下载,完成整个实验的设计。 五、实验电路连接与实验结果 用拨码开关的低三位代表译码器的输入(A,B,C),将之与 EP1K10TC100—3 的管脚 相连;用 LED 灯来表示译码器的输出(D0~D7),将之与 EP1K10TC100—3 芯片的管脚相 连。拨动拨档开关,可以观察发光二极管与输入状态的对应关系同真值表中所描述的情况是 一致的。 六、实验报告与思考 1)在输入端加入使能端后应如何设计。 2)输入信号是按格雷码方式的编码时,译码器如何设计。 3)设计与 T1138 功能类似的数据分配器。 附: 用硬件描述语言完成译码器的设计: (1)、生成设计项目文件。 (2)、启动 File\New 菜单命令,如图 2—1—10:

Nev ☒ Device Design Files Other Files AHDL File Block Diagram/Schematic File EDIF File SOPC Builder System Verilog HDL File VHDL File OK Cancel 图2一1一10 (3)、选择Text Editor file,点击OK: (4)、存成.tdf文件,然后进行编译即可。 其他都与原理图输入相同

图 2—1—10 (3)、选择 Text Editor file,点击 OK: (4)、存成.tdf 文件,然后进行编译即可。 其他都与原理图输入相同