实验十三步进电机控制实验 一、实验目的 1、了解步进电机的工作原理。 2、掌握用FPGA产生驱动步进电机的时序。 3、掌握用FPGA来控制步进电机转动的整个过程。 二、硬件要求 1、步进电机。 2、主芯片FPGA EP1K10TC1003. 3、8个按键和一个拨挡开关。 4、可变时钟源。 三、实验原理 步进电机是工业过程控制及仪表中常用的控制元件之一,例如在机械装置中可以用丝杆 把角度变为直线位移,也可以用步进电机带动螺旋电位器,调节电压或电源,从而实现对执 行机械的控制。步进电机可以直接用数字信号驱动,使用非常方便。步进电机还具有快速启 停、精确步进和定位等特点,因而在数控机床、绘图仪、打印机以及光学仪器中得到广泛的 应用。 步进电机是工业控制及仪表中常用的控制元件之一,例如在机械装置中可以精确控制 机械装置的旋转角度、移动距离等。步进电机可以直接用数字信号来驱动,使用非常方便。 另外步进电机还具有快速起停、精确步进和定位的特点。 步进电机实际上是一个数据/角度转换器,三相步进电机的结构原理如下图所示: 三相步进电机的结构示意图 从图中可以看出,电机的定子有六个等分的磁极,A、A'、B、B’、C、C',相邻的 两个磁极之间夹角为60°,相对的两个磁极组成一组(A一A’,B一B',C一C'),当某一 绕组有电流通过时,该绕组相应的两个磁极形成N极和S极,每个磁极上各有五个均分布 的矩形小齿,电机的转子上有40个矩形小齿均匀地分布在圆周上,相邻两个齿之间夹角为 9°。 ()当某一相绕组通电时,对应的磁极就产生磁场,并与转子转动一定的角度,使转子和 定子的齿相互对齐。由此可见,错齿是促使步进电机旋转的原因。 例如在三相三拍控制方式中,若A相通电,B、C相都不通电,在磁场作用下使转子齿 和A相的定子齿对齐,我们以此作为初始状态。设与A相磁极中心线对齐的转子的齿为0 号齿,由于B相磁极与A相磁极相差120°不是9°的整数倍(120÷9=132/3),所以此时 转子齿没有与B相定子的齿对应,只是第13号小齿靠近B相磁极的中心线,与中心线相差 3°,如果此时突然变为B相通电,A、C相不通电,则B相磁极迫使13号转子齿与之对齐, 转子就转动3°,这样使电机转子一步。如果按照A一AB一B一BC一C一CA一A次序通电

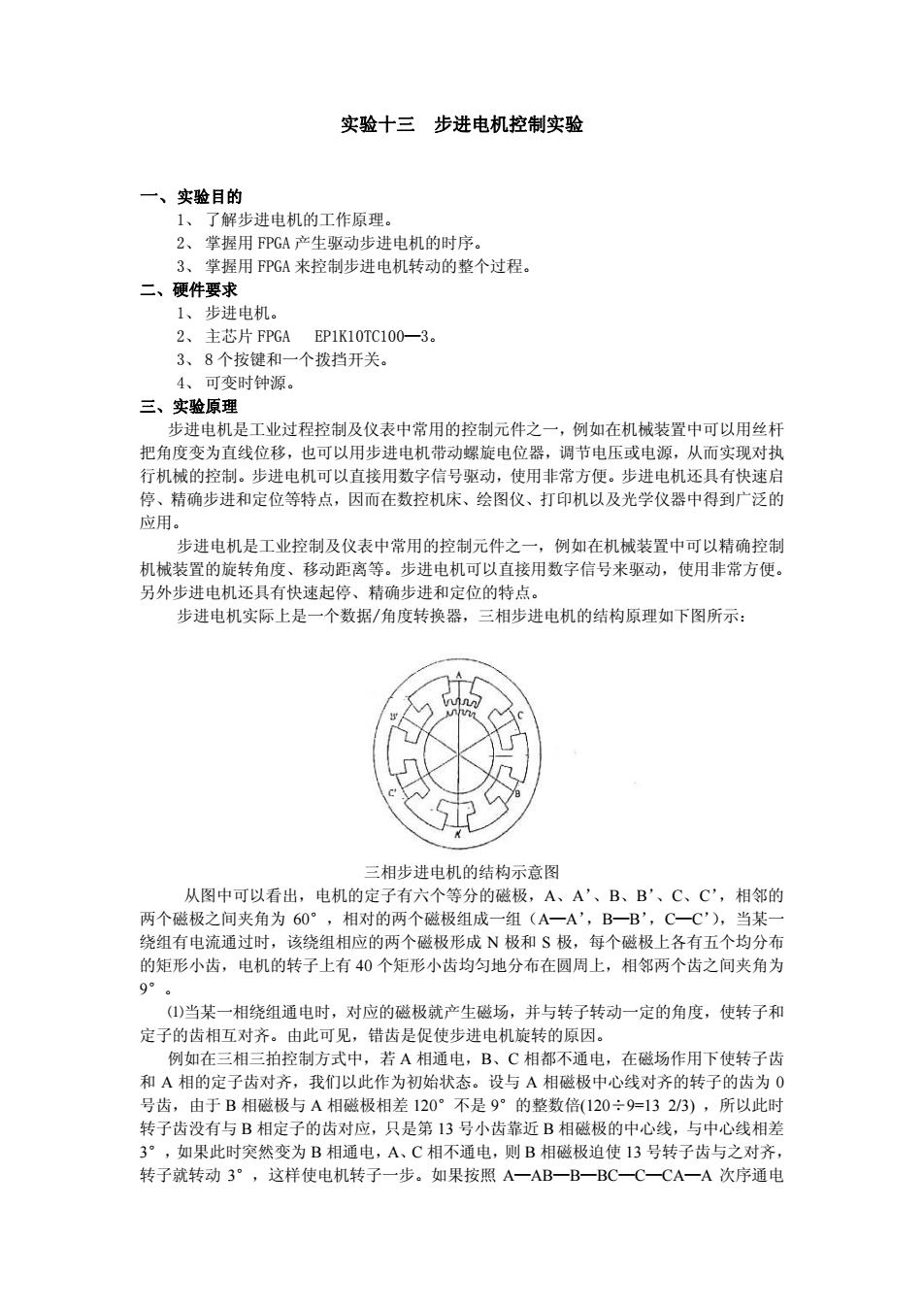

实验十三 步进电机控制实验 一、实验目的 1、 了解步进电机的工作原理。 2、 掌握用 FPGA 产生驱动步进电机的时序。 3、 掌握用 FPGA 来控制步进电机转动的整个过程。 二、硬件要求 1、 步进电机。 2、 主芯片 FPGA EP1K10TC100—3。 3、 8 个按键和一个拨挡开关。 4、 可变时钟源。 三、实验原理 步进电机是工业过程控制及仪表中常用的控制元件之一,例如在机械装置中可以用丝杆 把角度变为直线位移,也可以用步进电机带动螺旋电位器,调节电压或电源,从而实现对执 行机械的控制。步进电机可以直接用数字信号驱动,使用非常方便。步进电机还具有快速启 停、精确步进和定位等特点,因而在数控机床、绘图仪、打印机以及光学仪器中得到广泛的 应用。 步进电机是工业控制及仪表中常用的控制元件之一,例如在机械装置中可以精确控制 机械装置的旋转角度、移动距离等。步进电机可以直接用数字信号来驱动,使用非常方便。 另外步进电机还具有快速起停、精确步进和定位的特点。 步进电机实际上是一个数据/角度转换器,三相步进电机的结构原理如下图所示: 三相步进电机的结构示意图 从图中可以看出,电机的定子有六个等分的磁极,A、A’、B、B’、C、C’,相邻的 两个磁极之间夹角为 60°,相对的两个磁极组成一组(A—A’,B—B’,C—C’),当某一 绕组有电流通过时,该绕组相应的两个磁极形成 N 极和 S 极,每个磁极上各有五个均分布 的矩形小齿,电机的转子上有 40 个矩形小齿均匀地分布在圆周上,相邻两个齿之间夹角为 9°。 ⑴当某一相绕组通电时,对应的磁极就产生磁场,并与转子转动一定的角度,使转子和 定子的齿相互对齐。由此可见,错齿是促使步进电机旋转的原因。 例如在三相三拍控制方式中,若 A 相通电,B、C 相都不通电,在磁场作用下使转子齿 和 A 相的定子齿对齐,我们以此作为初始状态。设与 A 相磁极中心线对齐的转子的齿为 0 号齿,由于 B 相磁极与 A 相磁极相差 120°不是 9°的整数倍(120÷9=13 2/3) ,所以此时 转子齿没有与 B 相定子的齿对应,只是第 13 号小齿靠近 B 相磁极的中心线,与中心线相差 3°,如果此时突然变为 B 相通电,A、C 相不通电,则 B 相磁极迫使 13 号转子齿与之对齐, 转子就转动 3°,这样使电机转子一步。如果按照 A—AB—B—BC—C—CA—A 次序通电

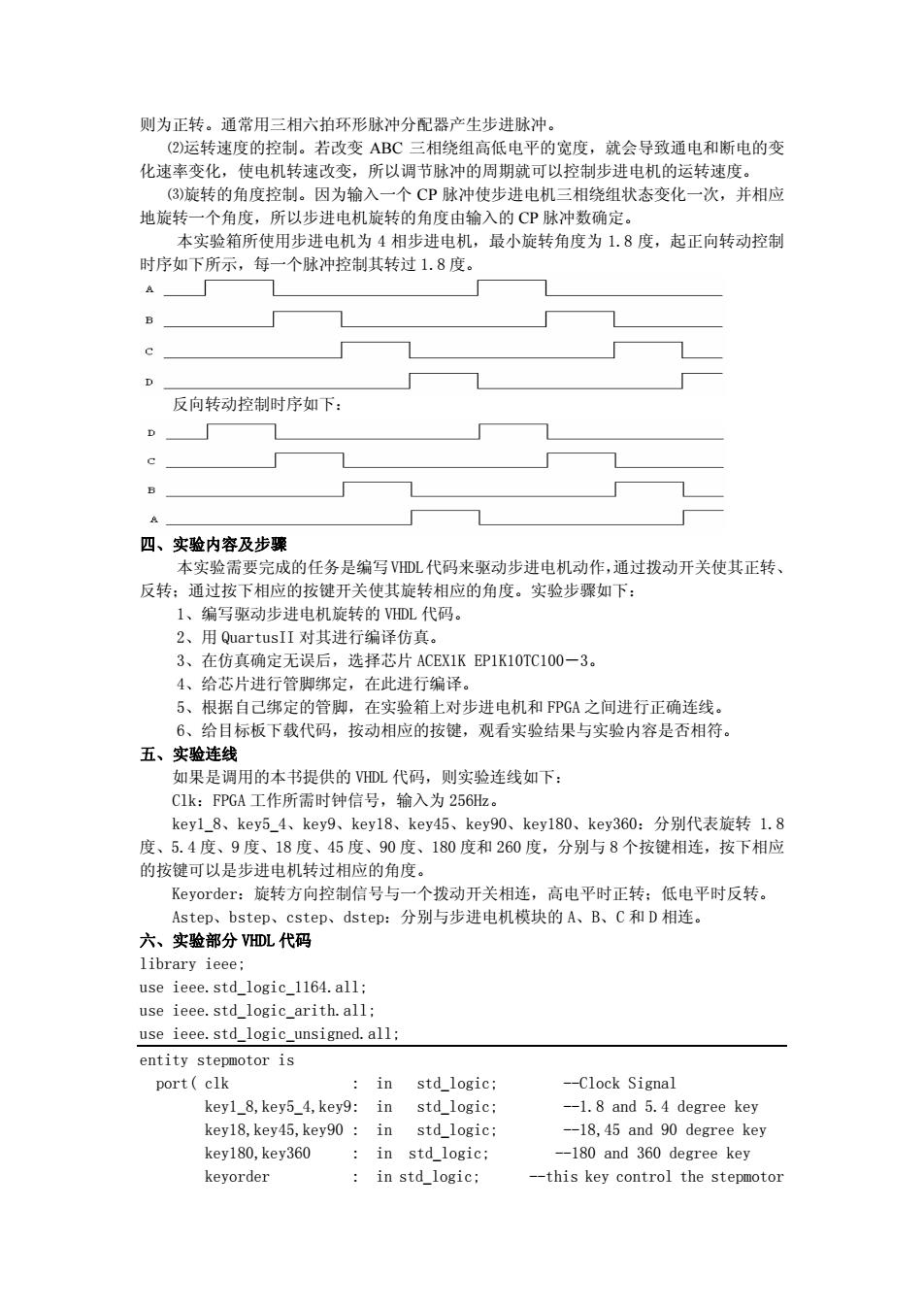

则为正转。通常用三相六拍环形脉冲分配器产生步进脉冲。 (2)运转速度的控制。若改变ABC三相绕组高低电平的宽度,就会导致通电和断电的变 化速率变化,使电机转速改变,所以调节脉冲的周期就可以控制步进电机的运转速度。 (3)旋转的角度控制。因为输入一个CP脉冲使步进电机三相绕组状态变化一次,并相应 地旋转一个角度,所以步进电机旋转的角度由输入的CP脉冲数确定。 本实验箱所使用步进电机为4相步进电机,最小旋转角度为1.8度,起正向转动控制 时序如下所示,每一个脉冲控制其转过1.8度。 B 反向转动控制时序如下: 四、实验内容及步骤 本实验需要完成的任务是编写VDL代码来驱动步进电机动作,通过拨动开关使其正转、 反转:通过按下相应的按键开关使其旋转相应的角度。实验步骤如下: 1、编写驱动步进电机旋转的VHDL代码。 2、用QuartusII对其进行编译仿真。 3、在仿真确定无误后,选择芯片ACEX1KEP1K10TC100-3。 4、给芯片进行管脚绑定,在此进行编译。 5、根据自己绑定的管脚,在实验箱上对步进电机和FPGA之间进行正确连线。 6、给目标板下载代码,按动相应的按键,观看实验结果与实验内容是否相符。 五、实验连线 如果是调用的本书提供的DL代码,则实验连线如下: C1k:FPGA工作所需时钟信号,输入为256Hz。 key1_8、key5_4、key9、key18、key45、key90、key180、key360:分别代表旋转1.8 度、5.4度、9度、18度、45度、90度、180度和260度,分别与8个按键相连,按下相应 的按键可以是步进电机转过相应的角度。 Keyorder:旋转方向控制信号与一个拨动开关相连,高电平时正转;低电平时反转。 Astep、bstep、cstep、dstep:分别与步进电机模块的A、B、C和D相连。 六、实验部分DL代码 library ieee; use ieee.std logic 1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity stepmotor is port(clk in std logic; --Clock Signal keyl_8,key5_4,key9:in std_logic; --1.8 and 5.4 degree key key18,key45,key90 in std_logic; --18,45 and 90 degree key key180,key360 in std_logic; --180 and 360 degree key keyorder in std_logic; --this key control the stepmotor

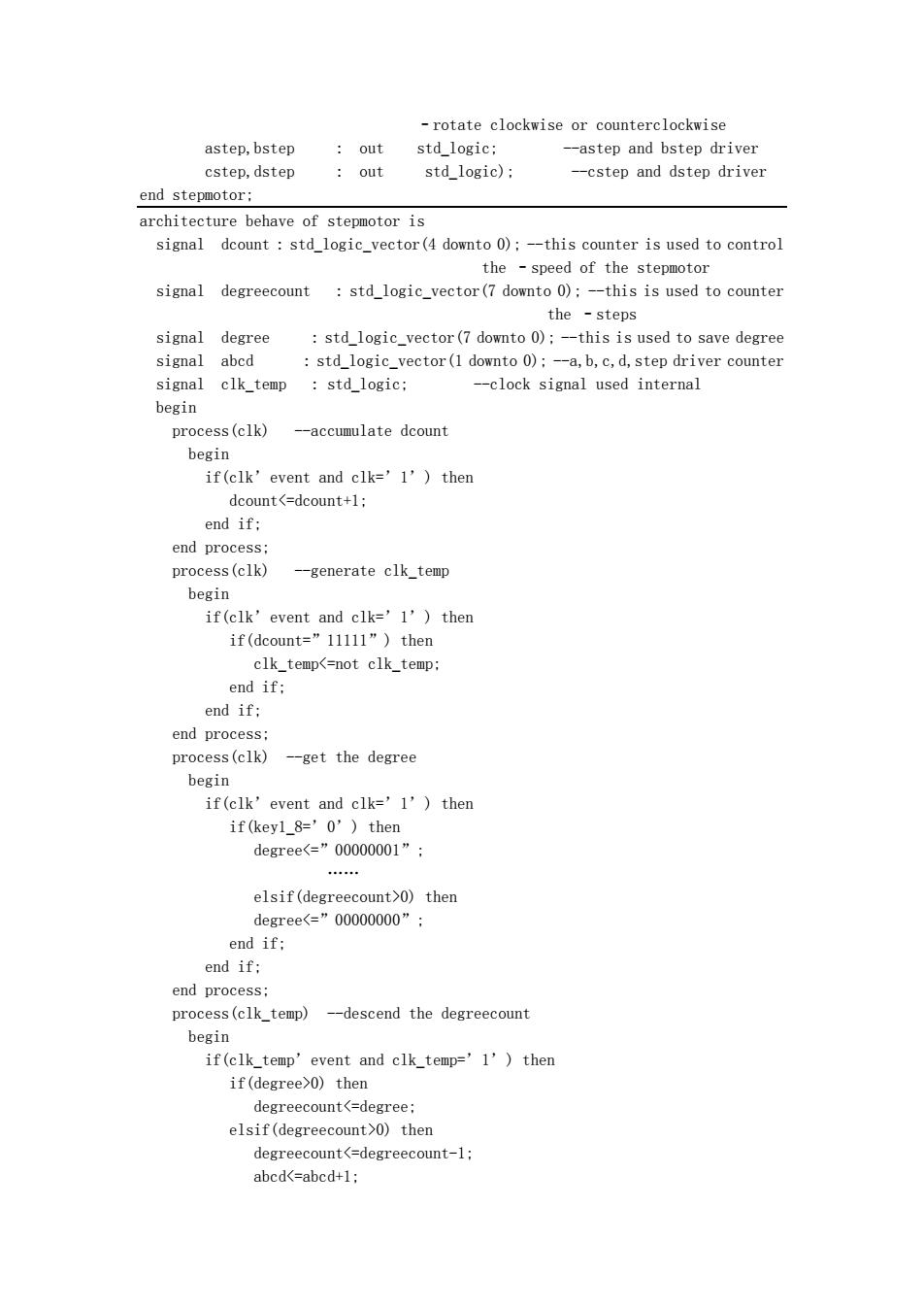

则为正转。通常用三相六拍环形脉冲分配器产生步进脉冲。 ⑵运转速度的控制。若改变 ABC 三相绕组高低电平的宽度,就会导致通电和断电的变 化速率变化,使电机转速改变,所以调节脉冲的周期就可以控制步进电机的运转速度。 ⑶旋转的角度控制。因为输入一个 CP 脉冲使步进电机三相绕组状态变化一次,并相应 地旋转一个角度,所以步进电机旋转的角度由输入的 CP 脉冲数确定。 本实验箱所使用步进电机为 4 相步进电机,最小旋转角度为 1.8 度,起正向转动控制 时序如下所示,每一个脉冲控制其转过 1.8 度。 反向转动控制时序如下: 四、实验内容及步骤 本实验需要完成的任务是编写 VHDL代码来驱动步进电机动作,通过拨动开关使其正转、 反转;通过按下相应的按键开关使其旋转相应的角度。实验步骤如下: 1、编写驱动步进电机旋转的 VHDL 代码。 2、用 QuartusII 对其进行编译仿真。 3、在仿真确定无误后,选择芯片 ACEX1K EP1K10TC100-3。 4、给芯片进行管脚绑定,在此进行编译。 5、根据自己绑定的管脚,在实验箱上对步进电机和 FPGA 之间进行正确连线。 6、给目标板下载代码,按动相应的按键,观看实验结果与实验内容是否相符。 五、实验连线 如果是调用的本书提供的 VHDL 代码,则实验连线如下: Clk:FPGA 工作所需时钟信号,输入为 256Hz。 key1_8、key5_4、key9、key18、key45、key90、key180、key360:分别代表旋转 1.8 度、5.4 度、9 度、18 度、45 度、90 度、180 度和 260 度,分别与 8 个按键相连,按下相应 的按键可以是步进电机转过相应的角度。 Keyorder:旋转方向控制信号与一个拨动开关相连,高电平时正转;低电平时反转。 Astep、bstep、cstep、dstep:分别与步进电机模块的 A、B、C 和 D 相连。 六、实验部分 VHDL 代码 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity stepmotor is port( clk : in std_logic; --Clock Signal key1_8,key5_4,key9: in std_logic; --1.8 and 5.4 degree key key18,key45,key90 : in std_logic; --18,45 and 90 degree key key180,key360 : in std_logic; --180 and 360 degree key keyorder : in std_logic; --this key control the stepmotor

-rotate clockwise or counterclockwise astep,bstep out std_logic; -astep and bstep driver cstep,dstep out std_logic); -cstep and dstep driver end stepmotor; architecture behave of stepmotor is signal dcount std_logic_vector(4 downto 0);--this counter is used to control the -speed of the stepmotor signal degreecount std_logic_vector(7 downto 0):--this is used to counter the -steps signal degree std_logic_vector(7 downto 0);--this is used to save degree signal abcd std_logic_vector(1 downto 0);--a,b,c,d,step driver counter signal clk_temp:std_logic; --clock signal used internal begin process(clk) --accumulate dcount begin if(clk'event and clk='1')then dcount0)then degree0)then degreecount0)then degreecount<=degreecount-1: abcd<=abcd+1;

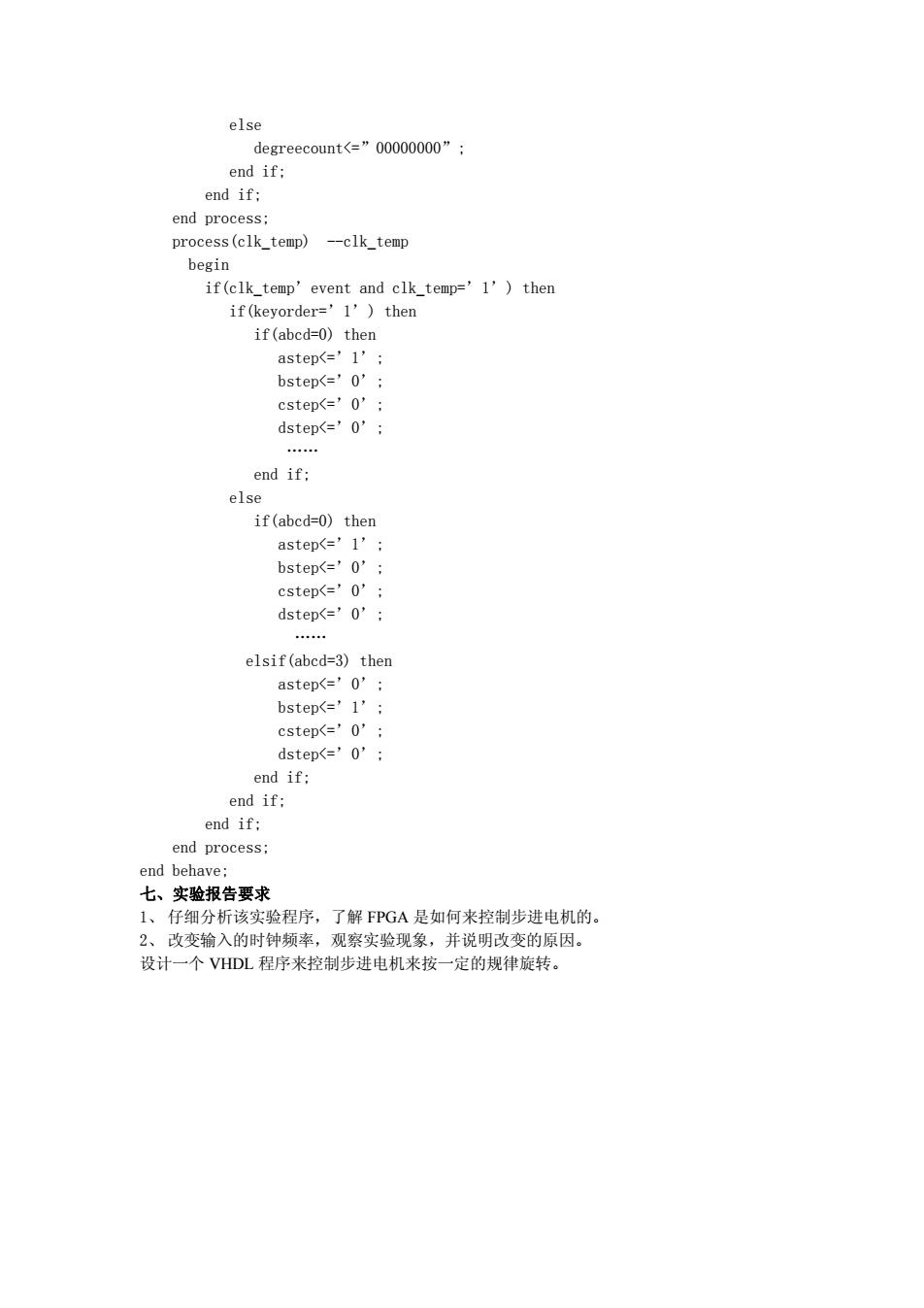

–rotate clockwise or counterclockwise astep,bstep : out std_logic; --astep and bstep driver cstep,dstep : out std_logic); --cstep and dstep driver end stepmotor; architecture behave of stepmotor is signal dcount : std_logic_vector(4 downto 0); --this counter is used to control the –speed of the stepmotor signal degreecount : std_logic_vector(7 downto 0); --this is used to counter the –steps signal degree : std_logic_vector(7 downto 0); --this is used to save degree signal abcd : std_logic_vector(1 downto 0); --a,b,c,d,step driver counter signal clk_temp : std_logic; --clock signal used internal begin process(clk) --accumulate dcount begin if(clk’event and clk=’1’) then dcount0) then degree0) then degreecount0) then degreecount<=degreecount-1; abcd<=abcd+1;

else degreecount<=”00000000”; end if; end if; end process; process(clk_temp)--clk_temp begin if(clk_temp'event and clk_temp='1')then if(keyorder='1')then if(abcd=0)then astep<=’1’: bstep<=’0': cstep<=’0': dstep='0'; … end if; else if(abcd=0)then astep<=’1’: bstep<=’0': cstep<='0'; dstep<='0'; … elsif(abcd=3)then astep<=’0': bstep<=’1’: cstep<='0'; dstep<=’0'; end if; end if; end if; end process; end behave: 七、实验报告要求 1、仔细分析该实验程序,了解FPGA是如何来控制步进电机的。 2、改变输入的时钟频率,观察实验现象,并说明改变的原因。 设计一个VHDL程序来控制步进电机来按一定的规律旋转

else degreecount<=”00000000”; end if; end if; end process; process(clk_temp) --clk_temp begin if(clk_temp’event and clk_temp=’1’) then if(keyorder=’1’) then if(abcd=0) then astep<=’1’; bstep<=’0’; cstep<=’0’; dstep<=’0’; …… end if; else if(abcd=0) then astep<=’1’; bstep<=’0’; cstep<=’0’; dstep<=’0’; …… elsif(abcd=3) then astep<=’0’; bstep<=’1’; cstep<=’0’; dstep<=’0’; end if; end if; end if; end process; end behave; 七、实验报告要求 1、 仔细分析该实验程序,了解 FPGA 是如何来控制步进电机的。 2、 改变输入的时钟频率,观察实验现象,并说明改变的原因。 设计一个 VHDL 程序来控制步进电机来按一定的规律旋转