实验五计数器及时序电路 一、实验目的 1、了解时序电路的经典设计方法(D触发器和K触发器和一般逻辑门组成的时序逻 辑电路)。 2、了解通用同步计数器,异步计数器的使用方法。 3、了解用同步计数器通过清零阻塞法和预显数法得到循环任意进制计数器的方法。 4、理解时许电路和同步计数器加译码电路的联系,设计任意编码计数器。 5、了解同步芯片和异步芯片的区别。 二、硬件需求 主芯片:EP1K10TC100一3,时钟源,4位七段数码管。 三、实验内容 1、用D触发器设计异步四位二进制加法计数器。 2、用K触发器设计异步二一十进制减法计数器。 3、用74LS161两个宏连接成八位二进制同步计数器。 4、用74LS390两个宏连接成八位二一十进制异步计数器。 5、用74LS161清零和置数法组成六进制和十二进制计数器。 6、分别用D触发器和同步计数器加译码电路的方法构成7进制电路实现如下编码:0, 2,5,3,4,6,1。 四、实验原理及连线 实验内容中的6个实验均要通过实验四的“扫描显示电路”内容进行显示,具体连线根 据每个实验内容完成时的管脚化分和定义,同相应的输入、输出接口功能模块相连,扫描模 块的连接参考实验四。 1、实验内容1的参考图2一5一1: 2、实验内容2的参考图2一5一2: 3、实验内容3的参考图2一5一3: 4、实验内容4的参考图2一5一4 5、实验内容5的参考图2一5一5: 6、实验内容6的参考图2一5一6:

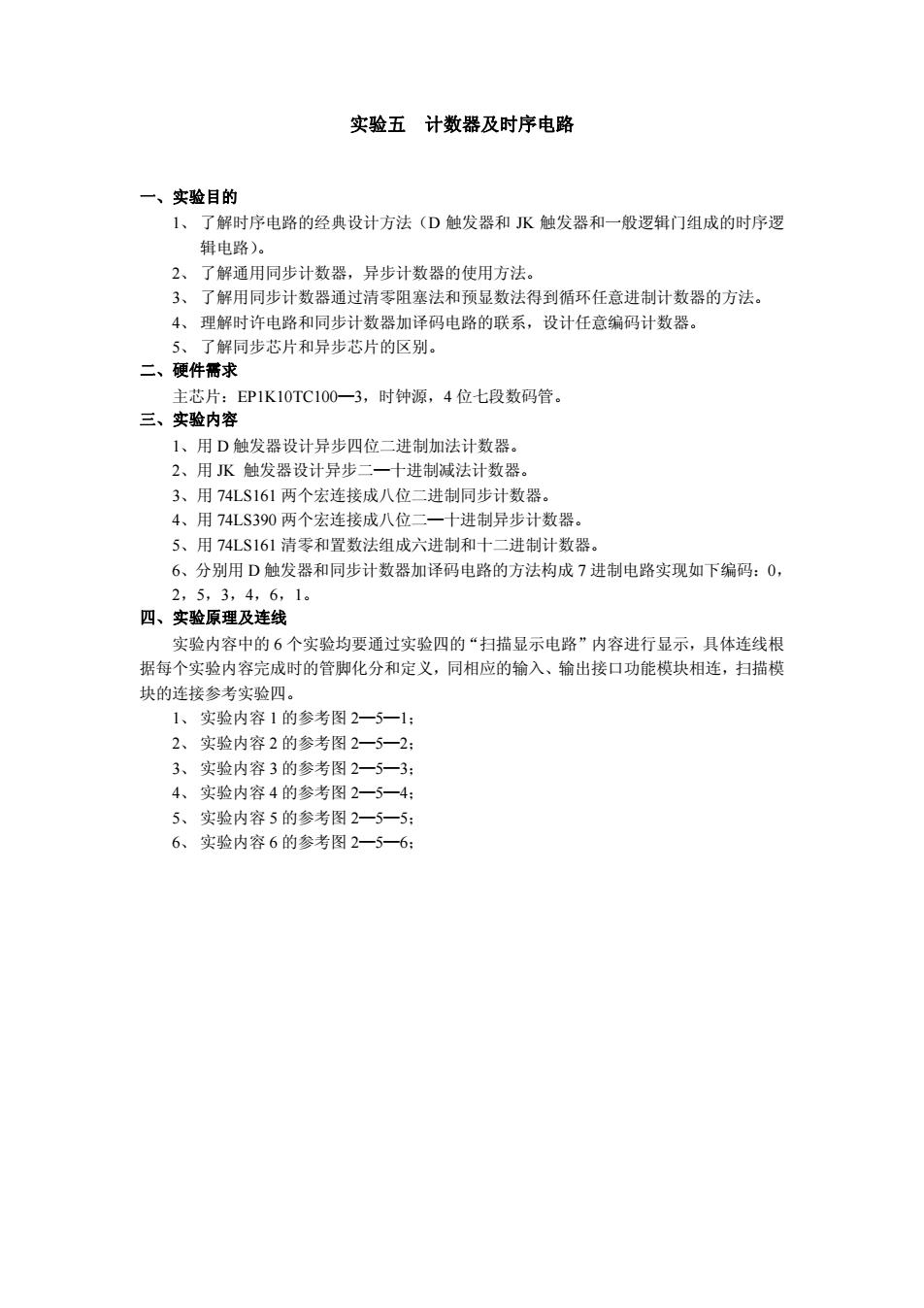

实验五 计数器及时序电路 一、实验目的 1、 了解时序电路的经典设计方法(D 触发器和 JK 触发器和一般逻辑门组成的时序逻 辑电路)。 2、 了解通用同步计数器,异步计数器的使用方法。 3、 了解用同步计数器通过清零阻塞法和预显数法得到循环任意进制计数器的方法。 4、 理解时许电路和同步计数器加译码电路的联系,设计任意编码计数器。 5、 了解同步芯片和异步芯片的区别。 二、硬件需求 主芯片:EP1K10TC100—3,时钟源,4 位七段数码管。 三、实验内容 1、用 D 触发器设计异步四位二进制加法计数器。 2、用 JK 触发器设计异步二—十进制减法计数器。 3、用 74LS161 两个宏连接成八位二进制同步计数器。 4、用 74LS390 两个宏连接成八位二—十进制异步计数器。 5、用 74LS161 清零和置数法组成六进制和十二进制计数器。 6、分别用 D 触发器和同步计数器加译码电路的方法构成 7 进制电路实现如下编码:0, 2,5,3,4,6,1。 四、实验原理及连线 实验内容中的 6 个实验均要通过实验四的“扫描显示电路”内容进行显示,具体连线根 据每个实验内容完成时的管脚化分和定义,同相应的输入、输出接口功能模块相连,扫描模 块的连接参考实验四。 1、 实验内容 1 的参考图 2—5—1; 2、 实验内容 2 的参考图 2—5—2; 3、 实验内容 3 的参考图 2—5—3; 4、 实验内容 4 的参考图 2—5—4; 5、 实验内容 5 的参考图 2—5—5; 6、 实验内容 6 的参考图 2—5—6;

D。D0 。:D1 成:D2 。D3 0 CLRN CLRN CLRN RESET 5 74161 $0 LDN SEL2 6 2 C 08 DELED ac OUTAUT'" ENT QD .. ENP RCO D3.01 以 OUTPUT CLRN NUM[3..0] 6 UTAUT CLK OUTPUT' COUNTER G 4 20 图2一5一1 说明: 计数时钟频率clk40Hz: 四位D触发器接成异步计数器: SEL0~SEL2为扫描地址(控制八位数码管的扫描顺序和速度): A.G为显示译码输出,代表数码管的七个段位(a,b,c,d,e,fg), 八位数码管同时顺序显示0~F。 妆:D3 6203 N: 7416 520啊 0Ut“ t51@5 QA 5200 图 ac DELED OUTUT 52@4 ENT QD 00 520的 P RCO 0兰 5100 CLRN 03.01 NUM[3..0] D 52070 CLK 0Ut“ 510的 COUNTER 52 0 5207 图2一5-2

图 2—5—1 说明: 计数时钟频率 clk<1Hz; 扫描时钟频率 ckdsp>40Hz; 四位 D 触发器接成异步计数器; SEL0~SEL2 为扫描地址(控制八位数码管的扫描顺序和速度); A…G 为显示译码输出,代表数码管的七个段位(a,b,c,d,e,f,g), 八位数码管同时顺序显示 0~F。 图 2—5—2

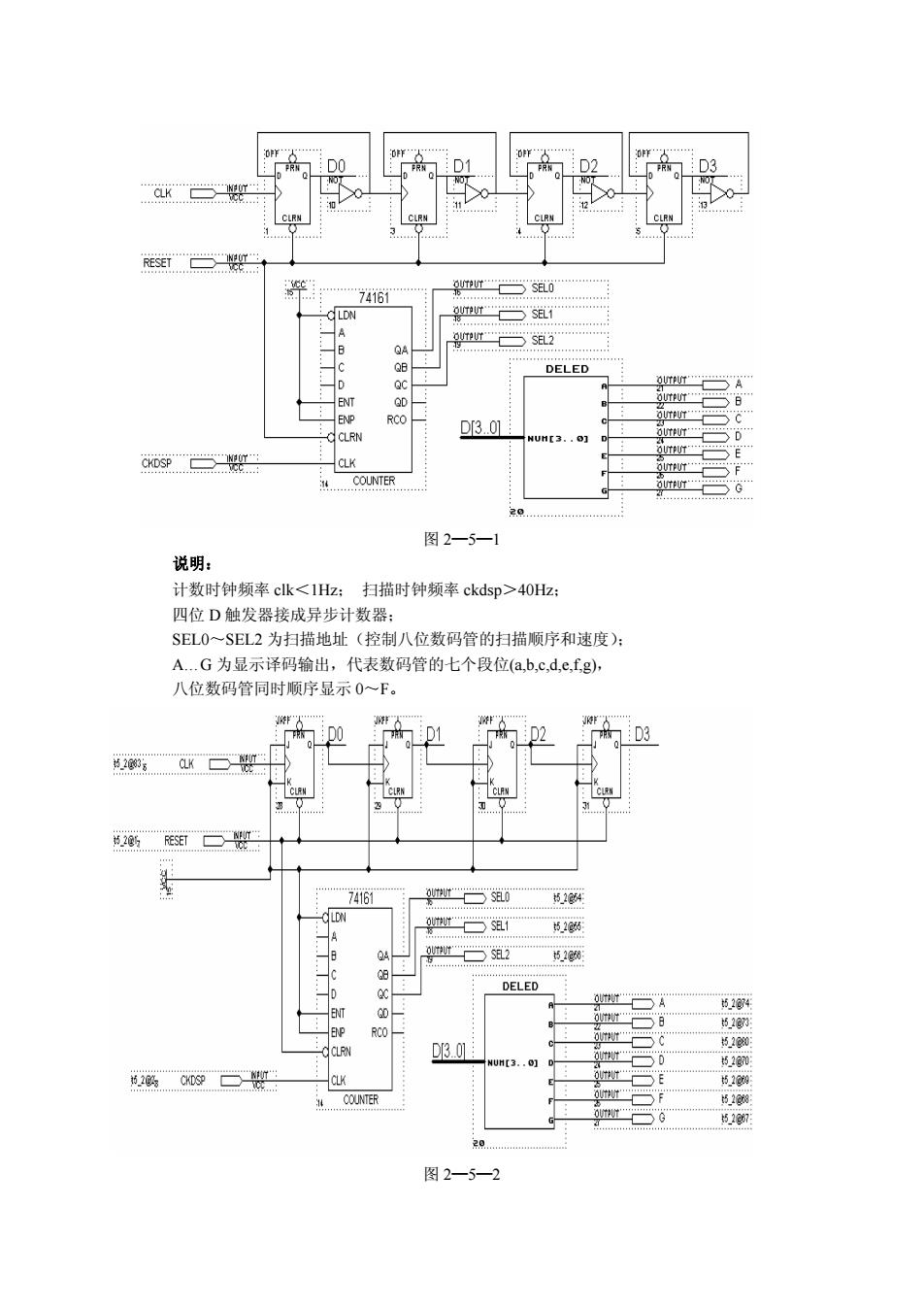

说明基本同上: 减法计数只需对上图稍加处理。 :…74161 LDN Select high 4 bit or low. 4 bit with SEL QA DAD ;A1 QB DA2 DAI7..0 D ENT :DA3 SEL 合H8_4 ENP RCO d CLRN CKCNT CLK ..COUNTER DELED 74161 NUME3.0] OUU OUTPUT-. 0A4 QA ... DA5 D Qc ENT DA7 ENP RCO dCLRN CLK 点.COUNTER 图2一5一3 说明: 计数时钟频率CKCNT4OHz: 两个74LS161串接成典型的同步计数器; SH84块完成扫描数据的切换: SEL0,A..G说明同前: 两位数码管同时顺序显示00~FF。 Select high 4 bit or low 4 bit with SEL DELED 9Ur“ .. DA7..0 DAC7.0] SEL Q[3..01 MUM[3..0] SH8_4 eur... G G …"74390 :DAO 1CLR 1QA DA1 ICLKA 1g8 DA2 CLKB 1Q0 :DA3 1QD DAA 2QA :DA5 2CLR 2Q8 2CLKA 200 DA6 :DA7 2CLKB 2QD nDUAL COUNTER RESET CKDSP 图2一5一4

说明基本同上; 减法计数只需对上图稍加处理。 图 2—5—3 说明: 计数时钟频率 CKCNT<4Hz,扫描时钟频率 CKDSP>40Hz; 两个 74LS161 串接成典型的同步计数器; SH8_4 块完成扫描数据的切换; SEL0,A…G 说明同前; 两位数码管同时顺序显示 00~FF。 图 2—5—4

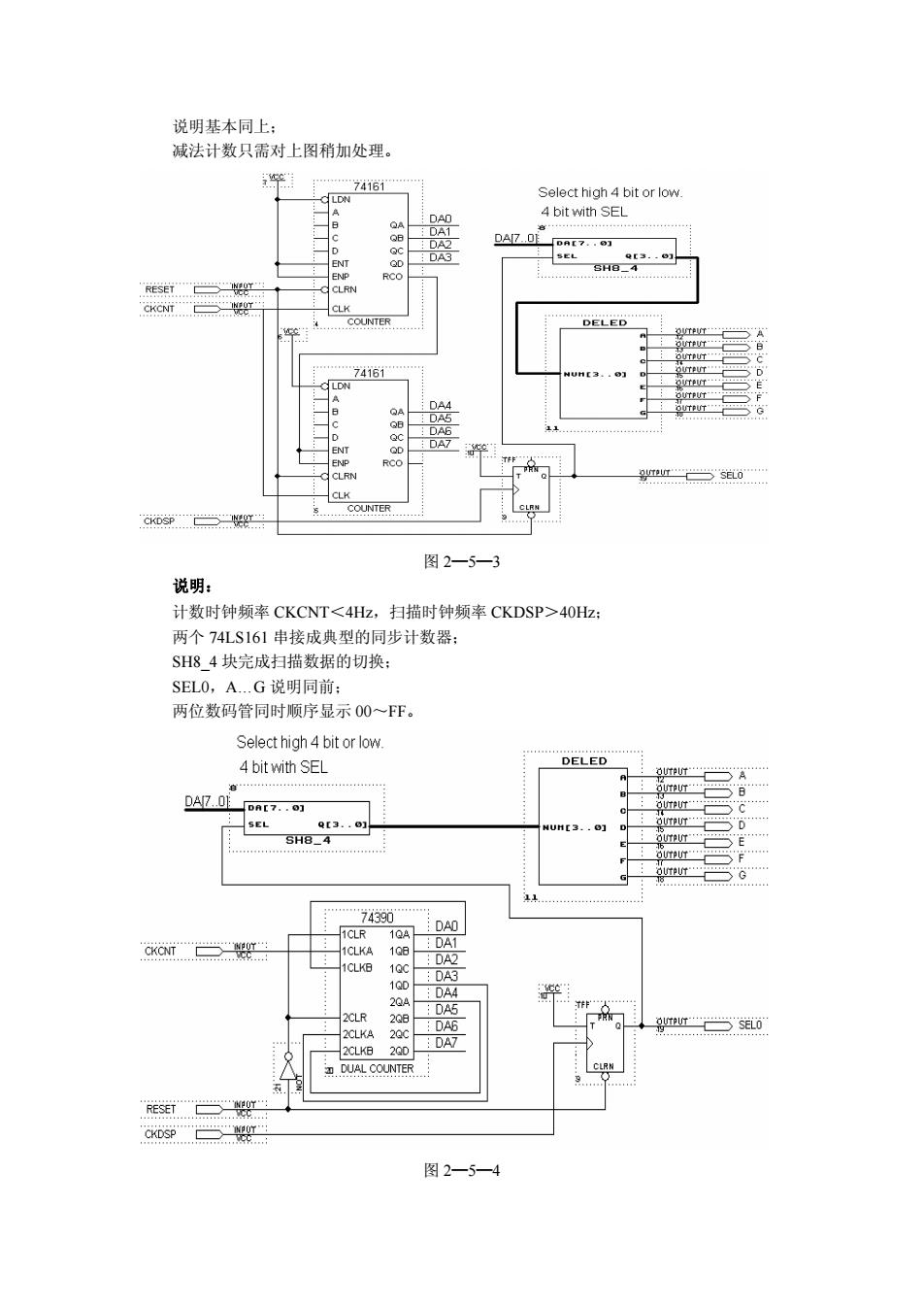

说明基本同前: 两位数码管同时顺序显示十进制00~99。 图2一5一5说明: 计数时钟频率CKCNT4OHZ: 清零法分别完成0~4、0~B的顺序计数: 置位法分别完成3一9、3~F的顺序计数: 用八位数码管显示四个计数状态。 T·pm UT DE3-.93 UP 01t:1 b就3:a OUT BE3 .03 3:。◆1 …纲 t5:,◇1 cLt1-4◆】 , T帆m ............ .m 7点 台 图2一5一5

说明基本同前; 两位数码管同时顺序显示十进制 00~99。 图 2—5—5 说明: 计数时钟频率 CKCNT<0.5HZ,扫描时钟频率 CKDSP>40HZ; 清零法分别完成 0~4、0~B 的顺序计数; 置位法分别完成 3~9、3~F 的顺序计数; 用八位数码管显示四个计数状态。 图 2—5—5

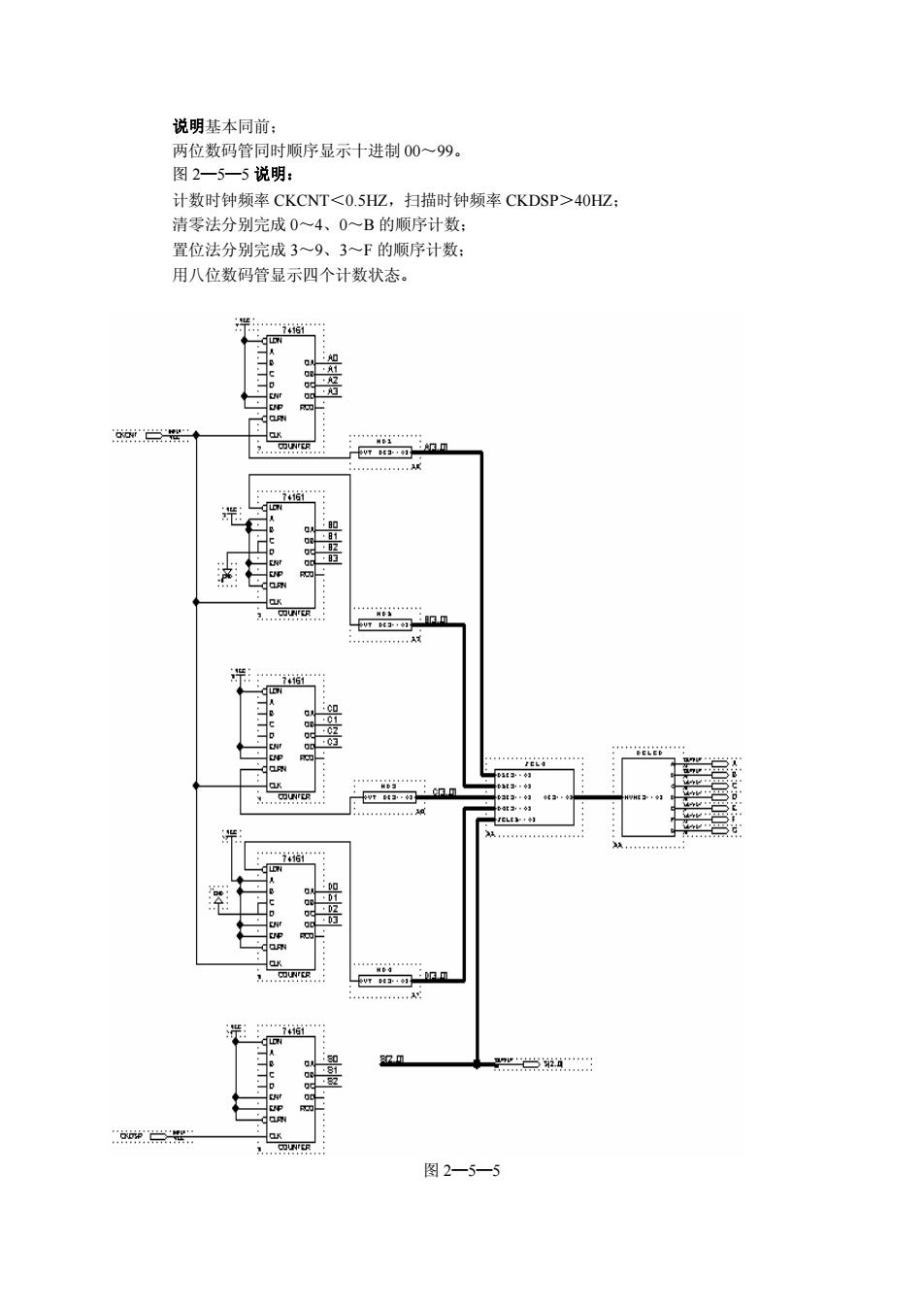

746 115115145111110411444401, hb1 [2.01q2.0]1 D2[2.01 0 01[2.0】Q[2.0], M2.O1 GA 23 A G hb4 cH g0- R00 24 0[2.01 DELED OUTPUT' ESET COUNTER hb2 NUM3.01 NUM[3..0] hb3 CLK Q[2.0] 13 RESET OKDSP wr: CLRM 图2一5—6 说明:计数时钟频率CLK4OHZ; 这是按0,2,5,3,4,6,1变化的七进制计数器:图中包括两个独立的实现方法,一 种为异步清零,一种为同步清零,两种方法同时显示: 5.1.6.gdf用74LS161计数器加译码的方法实现异步清零七进制计数器的设计;同时用状态机 的方法实现同步清零七进制计数器的设计

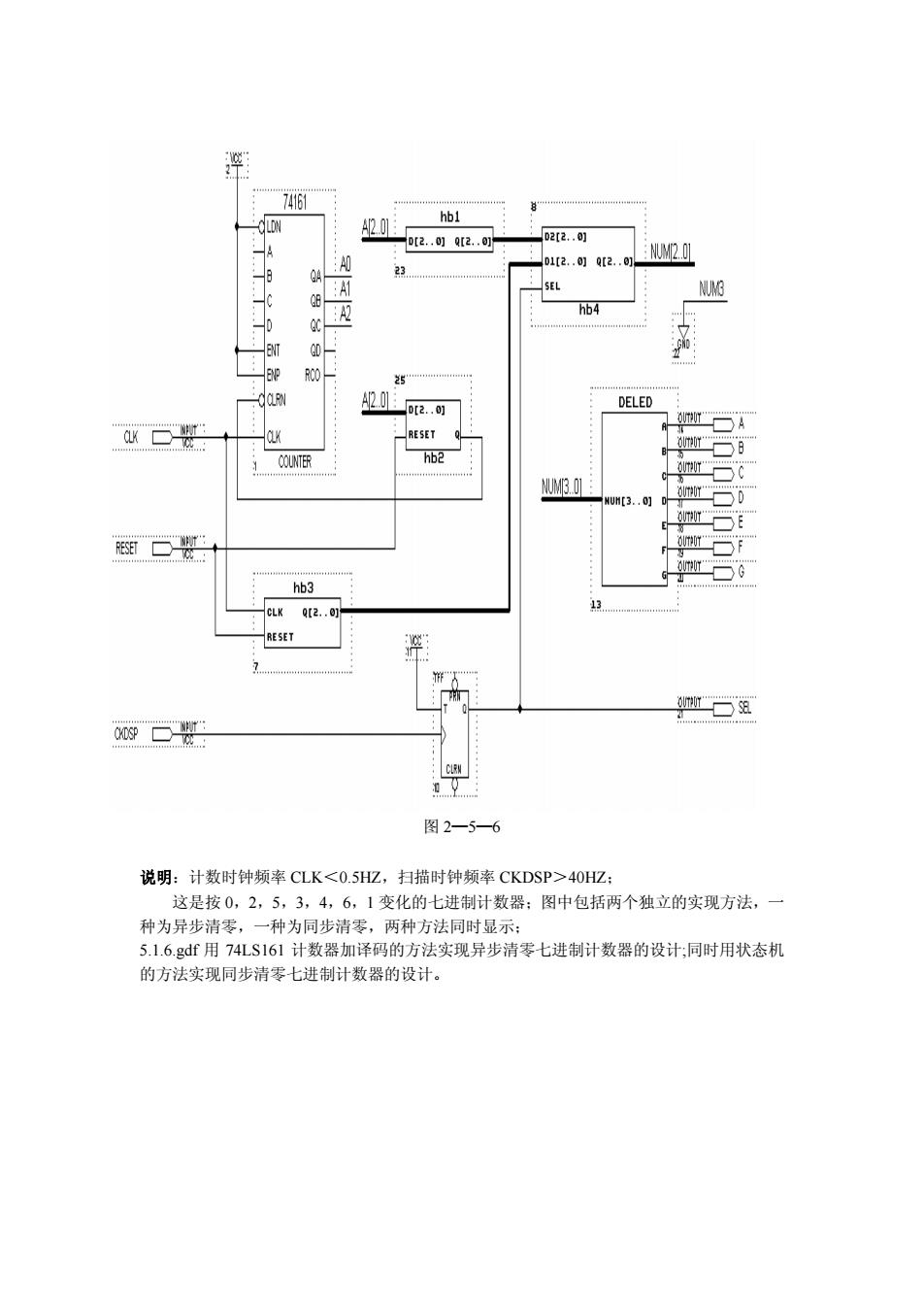

图 2—5—6 说明:计数时钟频率 CLK<0.5HZ,扫描时钟频率 CKDSP>40HZ; 这是按 0,2,5,3,4,6,1 变化的七进制计数器;图中包括两个独立的实现方法,一 种为异步清零,一种为同步清零,两种方法同时显示; 5.1.6.gdf 用 74LS161 计数器加译码的方法实现异步清零七进制计数器的设计;同时用状态机 的方法实现同步清零七进制计数器的设计