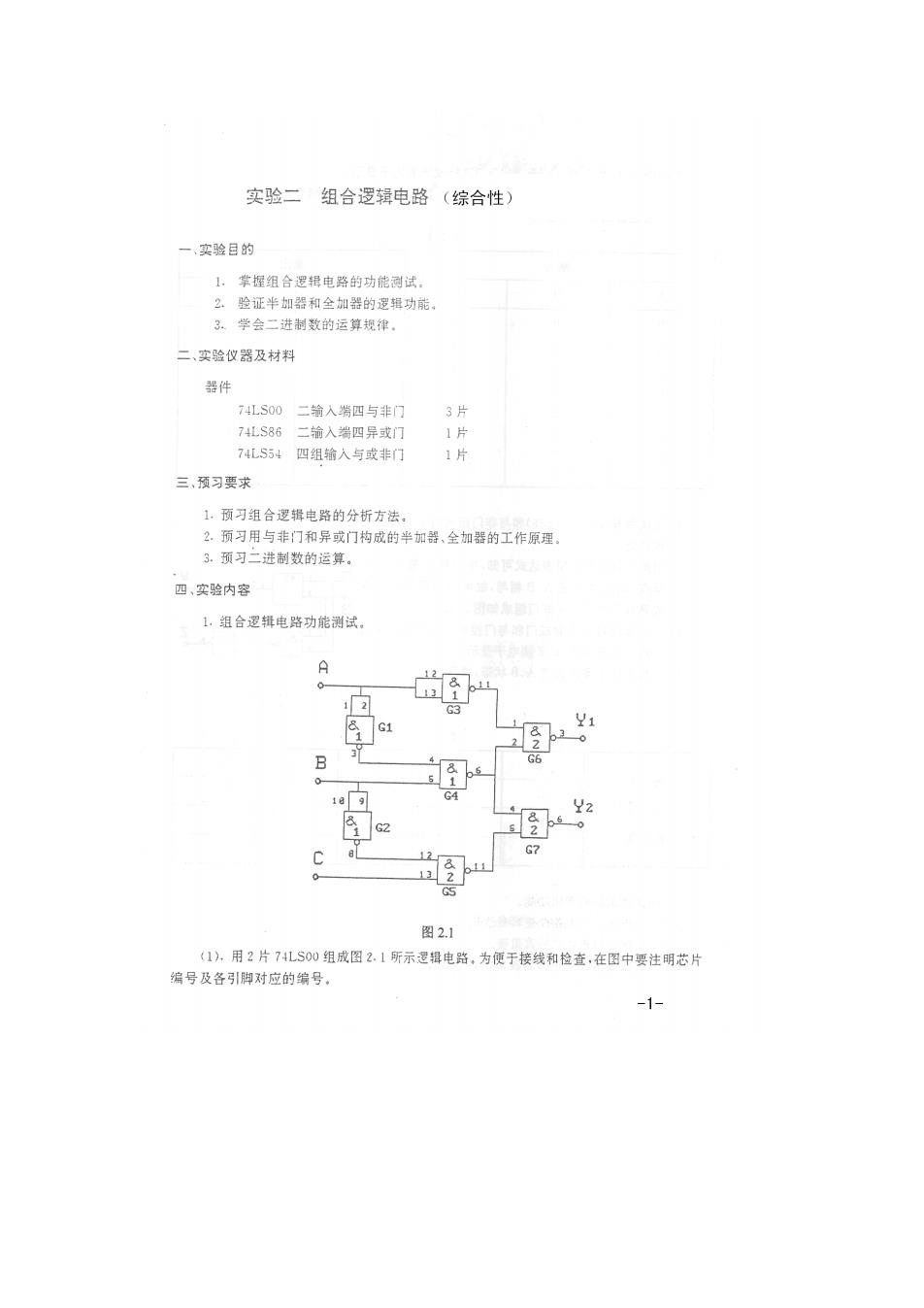

实验二组合逻辑电路(综合性) 一、实验目的 1.掌握组合逻辑电路的功能测试。 2.验证半如器和全加器的逻辑功能。 3.学会二进制数的运算规律, 二、实验仪器及材料 器件 74LS00二输入端四与非门 3片 74LS86二输入端四异或门 1片 74LS54四组输入与或非门 1片 三、预习要求 1.预习组合逻辑电路的分析方法。 2.预习用与非门和异或门构成的半加器、全加器的工作原理。 3.预习二进制数的运算。 四、实验内容 1.组合逻辑电路功能测试。 A 128 131 12 G3 G1 B G6 G4 86 c? 12 图2.1 (1),用2片74LS00组成图2.1所示逻辑电路,为便于接线和检查,在图中要注明芯片 编号及各引脚对应的编号。 -1

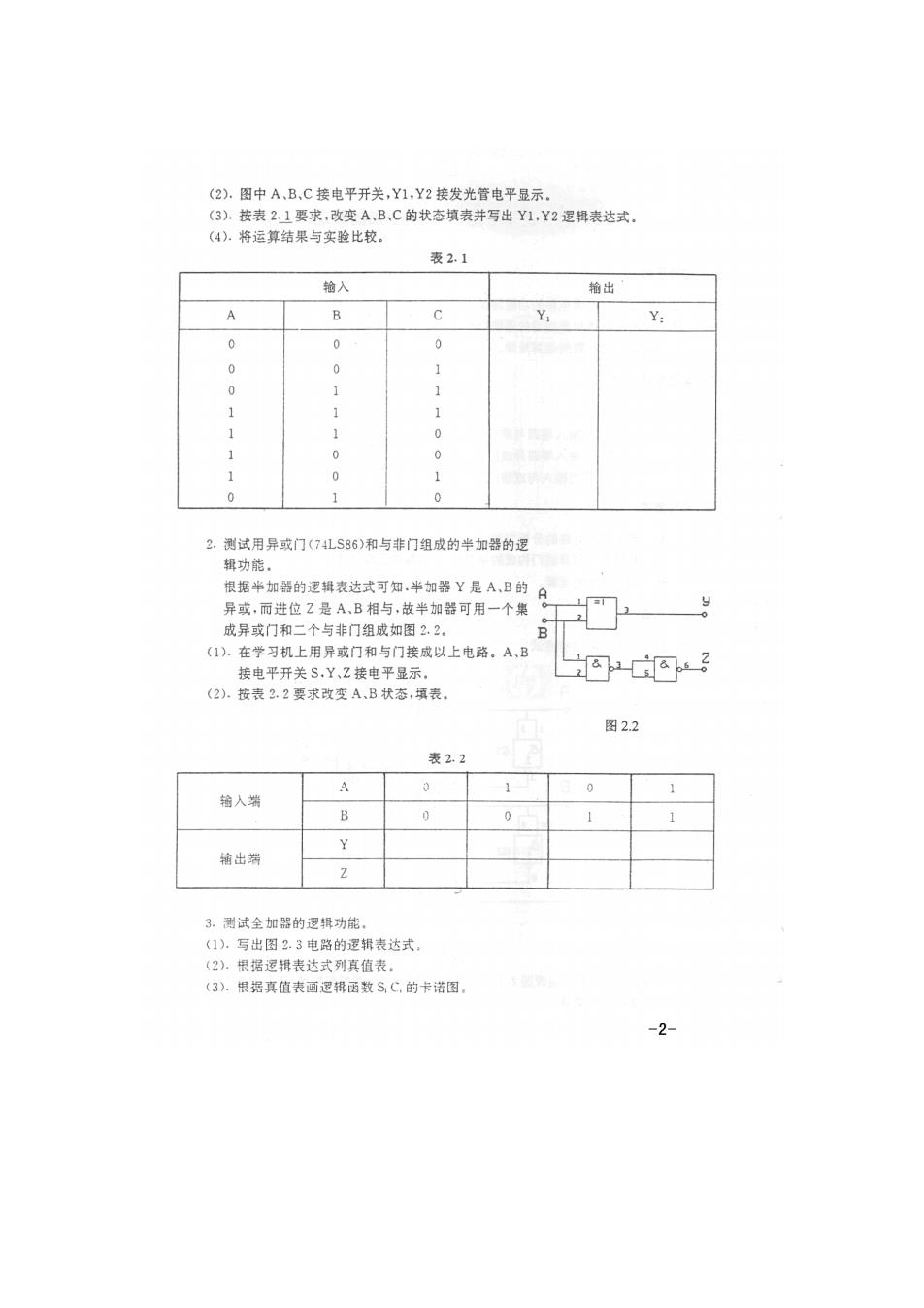

(2).图中A,B,C接电平开关,Y1,Y2接发光管电平显示。 (3).按表2.1要求,改变A、B、C的状态填表并写出Y1,Y2逻辑表达式. (4).将运算结果与实验比较。 表2.1 输入 输出 B C Y 0 0 0 0 0 1 0 1 1 1 1 1 1 1 0 1 0 0 1 0 0 2.测试用异或门(74LS86)和与非门组成的半加器的逻 辑功能。 根据半加器的逻辑表达式可知,半加器Y是A、B的 异或,而进位Z是A,B相与,故半加器可用一个集 成异或门和二个与非门组成如图2.2. B (1).在学习机上用异或门和与门接成以上电路。A,B 接电平开关S,Y、Z接电平显示, (2).按表2.2要求改变A、B状态,填表, 图2.2 表2.2 0 1 0 1 输入端 B 0 0 1 1 Y 输出端 3.测试全加器的逻辑功能 (1).写出图2.3电路的逻辑表达式 (2).根据运辑表达式列真值表。 (3).根据真值表画逻辑西数S,C,的卡诺图。 -2-

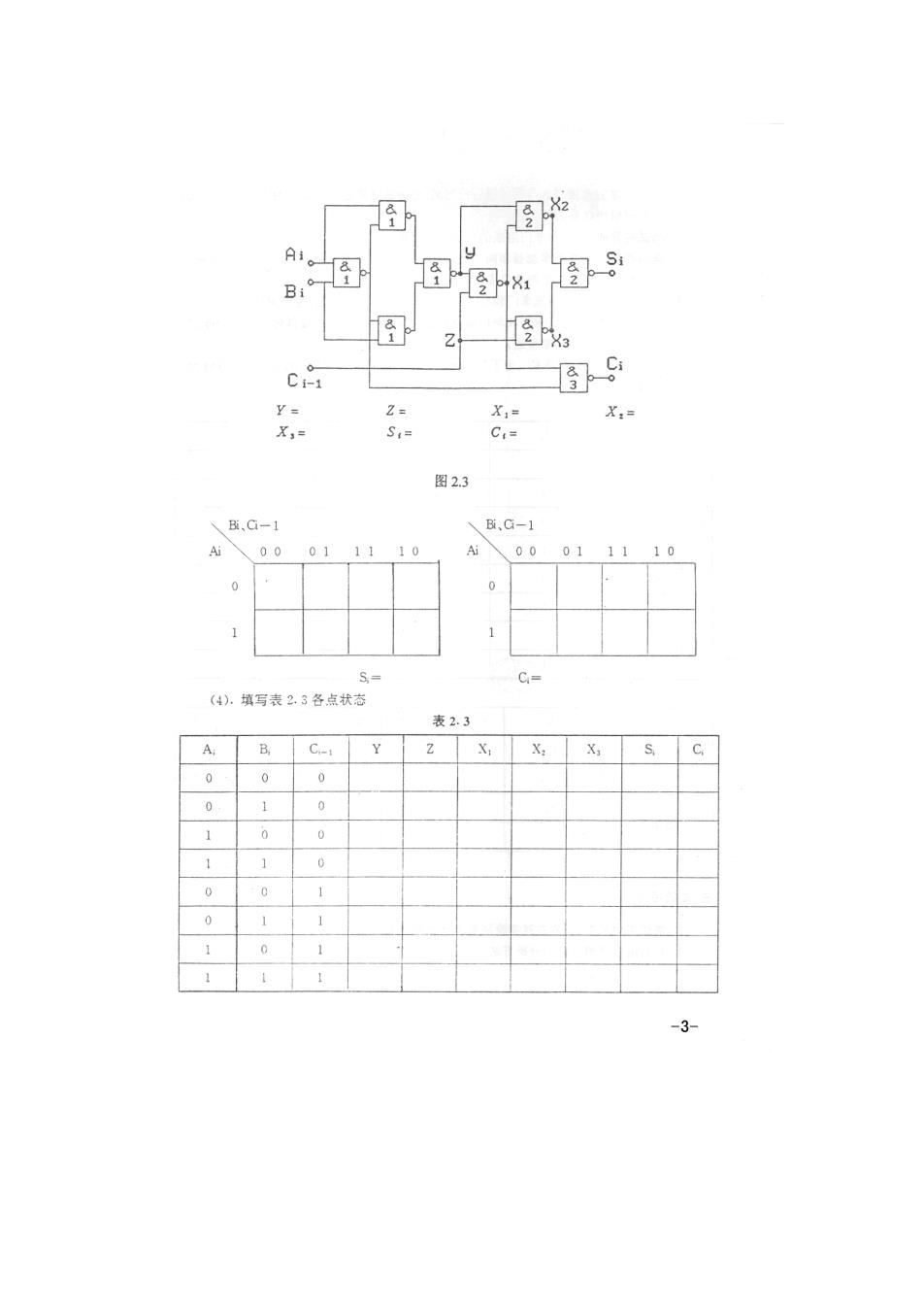

8 Bi 图囹 3S Z C-1 y= 2= X:= X:= X,= S,= C,= 图2.3 、Bi、C-1 、BE、G-1 Ai 00 011110 00011110 0 1 S= C= (4).填写表2.3各点状态 表2.3 A B C-1 X: X: X S 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 1 1 -3-

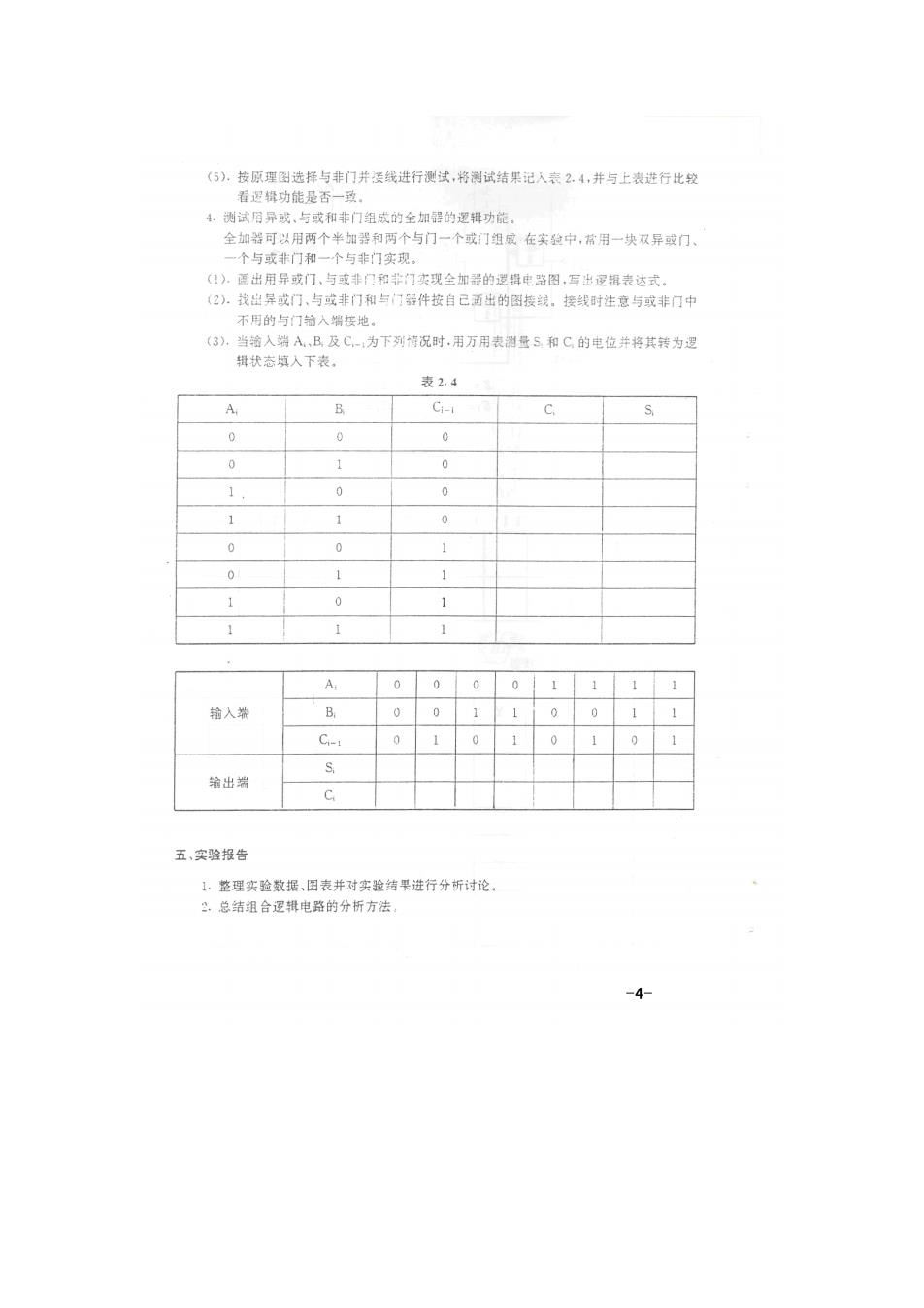

(5).按原理图选择与非门并接线进行测试,将测试结果记入表2.4,并与上表进行比较 看迟辑功能是否一政。 4.测试用异或、与或和非门组成的全加静的逻辑功能, 全如器可以用两个半如器和两个与门一个或门组成在实验中,常用一块双异或门、 一个与或非门和一个与非门实现。 (1).画出用异或门,与或非门和非门实现全加器的逻辑电路图,写出宠相表达式 (2).找出异或门,与或非门和与门器件按自已酒出的图接线。接线时注意与或非门中 不用的与门输入端按地。 (3),当输入端A,B,及C-:为下列情况时,用万用表测量5和C,的电位并将其转为逻 辑状态填入下装, 表2.4 A B C-1 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 1 0 1 1 1 1 A 0 0 0 0 输入端 B 0 C- 0 0 1 输出端 五、实验报告 1,整理实验数据,图表并对实验结果进行分析讨论, :.总结组合逻辑电路的分析方法, -4