实验六数字钟实验 一、实验目的 1、掌握多位计数器相连的设计方法。 2、掌握十进制、六十进制、二十四进制计数器的设计方法。 3、继续巩固多位共阴极扫描显示数码管的驱动及编码。 4、了解和掌握分频电路实现的方法。 5、掌握扬声器的驱动。 6、LED灯的花样显示。 7、掌握CPLD技术的层次化设计方法。 二、设计要求 1、具有时、分、秒计数显示功能,以24小时循环计时。 2、具有清零,调节小时、分钟功能。 3、具有整点报时功能,整点报时的同时LED灯花样显示。 三、硬件要求 1、主芯片EP1K10TC100一3。 2、8个LED灯。 3、扬声器。 4、8位七段扫描共阴极数码显示管。 5、三个按键开关(清零,调小时,调分钟)。 四、实验原理 在同一块CPLD芯片EP1K10TC100一3上集成了如下电路模块: 1、时钟计数: 秒一60进制BCD码计数: 分一60进制BCD码计数: 时一24进制BCD码计数: 同时整个计数器有清零,调分,调时功能。在接近整点时能提供报时信号。 2、有驱动8位七段共阴极扫描数码管的片选驱动信号输出和七段字行译码输出。编码 和扫描可参照“实验四”。 3、扬声器在整点时有报时驱动信号产生。 4、LED灯按个人要求在整点时有花样显示信号产生。 五、实验内容及步骤 1、根据电路特点,可在教师指导下用层次设计概念,将此设计任务分成若干模块,规 定每一模块的功能和各模块之间的接口。让几个学生分做和调试其中之一,然后再 将各模块合起来联试。以培养学生间的合作精神,同时加深层次化设计概念。 2、了解软件的元件管理深层含义,以及模块元件之间的连接概念,对于不同目录下的 同一设计,如何熔合

实验六 数字钟实验 一、实验目的 1、 掌握多位计数器相连的设计方法。 2、 掌握十进制、六十进制、二十四进制计数器的设计方法。 3、 继续巩固多位共阴极扫描显示数码管的驱动及编码。 4、 了解和掌握分频电路实现的方法。 5、 掌握扬声器的驱动。 6、 LED 灯的花样显示。 7、 掌握 CPLD 技术的层次化设计方法。 二、设计要求 1、具有时、分、秒计数显示功能,以 24 小时循环计时。 2、具有清零,调节小时、分钟功能。 3、具有整点报时功能,整点报时的同时 LED 灯花样显示。 三、硬件要求 1、 主芯片 EP1K10TC100—3。 2、 8 个 LED 灯。 3、 扬声器。 4、 8 位七段扫描共阴极数码显示管。 5、 三个按键开关(清零,调小时,调分钟)。 四、实验原理 在同一块 CPLD 芯片 EP1K10TC100—3 上集成了如下电路模块: 1、 时钟计数: 秒——60 进制 BCD 码计数; 分——60 进制 BCD 码计数; 时——24 进制 BCD 码计数; 同时整个计数器有清零,调分,调时功能。在接近整点时能提供报时信号。 2、 有驱动 8 位七段共阴极扫描数码管的片选驱动信号输出和七段字行译码输出。编码 和扫描可参照“实验四”。 3、 扬声器在整点时有报时驱动信号产生。 4、 LED 灯按个人要求在整点时有花样显示信号产生。 五、实验内容及步骤 1、 根据电路特点,可在教师指导下用层次设计概念,将此设计任务分成若干模块,规 定每一模块的功能和各模块之间的接口。让几个学生分做和调试其中之一,然后再 将各模块合起来联试。以培养学生间的合作精神,同时加深层次化设计概念。 2、 了解软件的元件管理深层含义,以及模块元件之间的连接概念,对于不同目录下的 同一设计,如何熔合

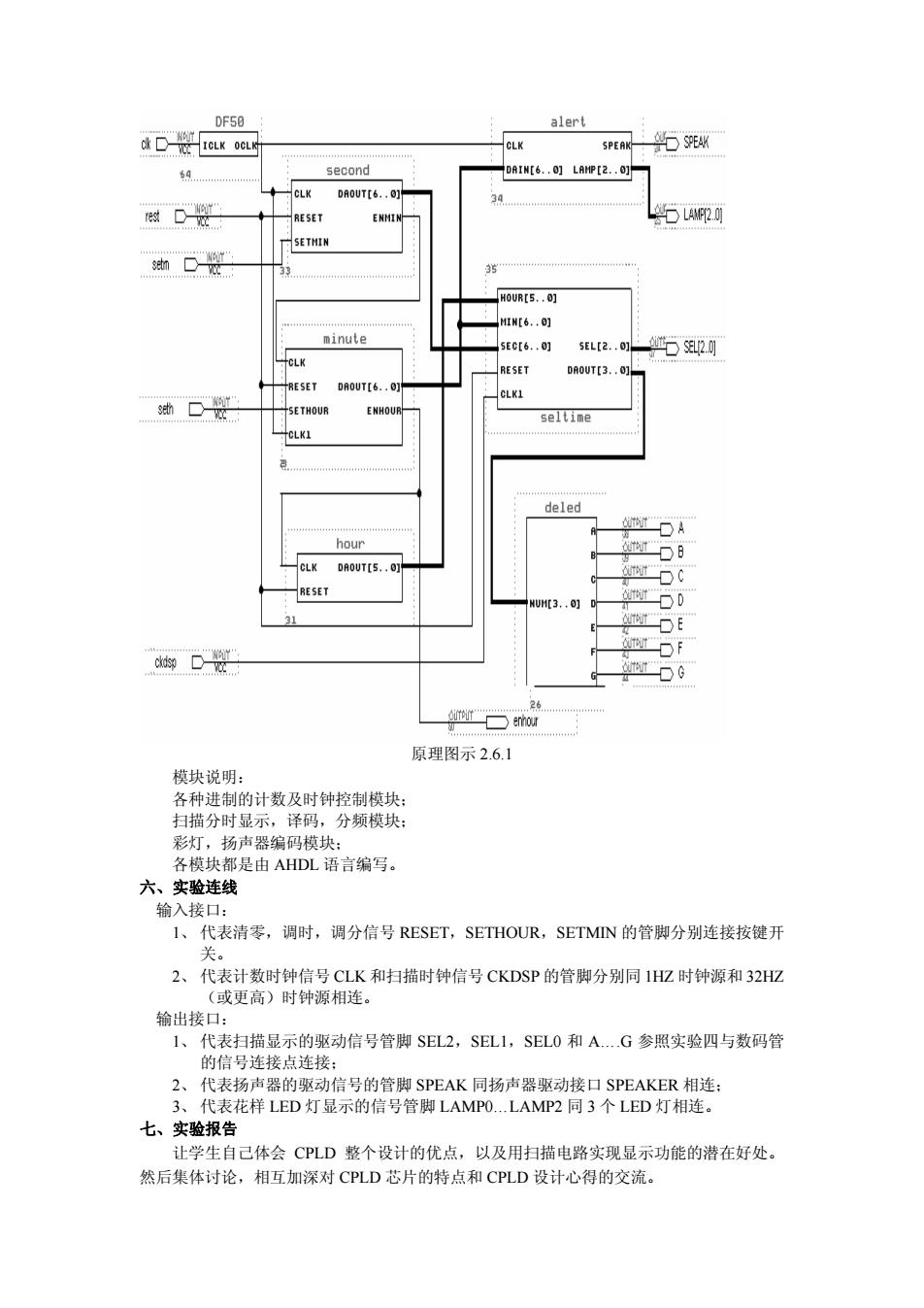

DF50: alert dteur ou CLK SPEAK SPEAK g second DAIN[6..0]LAMP[2..0] CLK DAOUT[6..0] 34 RESET ENMIN 5LAM2.可 SETHIN 33 H0UR[5.,0] MM[6,,O] minute 5EC[6..0] sELt2..01 SEL2.0 CLK RESET 0A0UT[3..0] TRESET DAOUT[6..0] CLK1 SETHOUR ENHOUR- seltime TCLKI deled OUTHUITA hour MD日 CLK DAOUT[5..0] CUTHIC RESET MUM[3..0] 0 UTAUTD 31 CUTITE 蝴D cusutF CUTTG 原理图示2.6.1 模块说明: 各种进制的计数及时钟控制模块: 扫描分时显示,译码,分频模块: 彩灯,扬声器编码模块: 各模块都是由AHDL语言编写。 六、实验连线 输入接口: I、代表清零,调时,调分信号RESET,SETHOUR,SETMIN的管脚分别连接按键开 关。 2、代表计数时钟信号CLK和扫描时钟信号CKDSP的管脚分别同1HZ时钟源和32H☑ (或更高)时钟源相连。 输出接口: 1、代表扫描显示的驱动信号管脚SEL2,SEL1,SEL0和A..G参照实验四与数码管 的信号连接点连接: 2、 代表扬声器的驱动信号的管脚SPEAK同扬声器驱动接口SPEAKER相连: 3、代表花样LED灯显示的信号管脚LAMPO..LAMP2同3个LED灯相连。 七、实验报告 让学生自己体会CPLD整个设计的优点,以及用扫描电路实现显示功能的潜在好处。 然后集体讨论,相互加深对CPLD芯片的特点和CPLD设计心得的交流

原理图示 2.6.1 模块说明: 各种进制的计数及时钟控制模块; 扫描分时显示,译码,分频模块; 彩灯,扬声器编码模块; 各模块都是由 AHDL 语言编写。 六、实验连线 输入接口: 1、 代表清零,调时,调分信号 RESET,SETHOUR,SETMIN 的管脚分别连接按键开 关。 2、 代表计数时钟信号 CLK 和扫描时钟信号 CKDSP 的管脚分别同 1HZ 时钟源和 32HZ (或更高)时钟源相连。 输出接口: 1、 代表扫描显示的驱动信号管脚 SEL2,SEL1,SEL0 和 A….G 参照实验四与数码管 的信号连接点连接; 2、 代表扬声器的驱动信号的管脚 SPEAK 同扬声器驱动接口 SPEAKER 相连; 3、 代表花样 LED 灯显示的信号管脚 LAMP0…LAMP2 同 3 个 LED 灯相连。 七、实验报告 让学生自己体会 CPLD 整个设计的优点,以及用扫描电路实现显示功能的潜在好处。 然后集体讨论,相互加深对 CPLD 芯片的特点和 CPLD 设计心得的交流