正在加载图片...

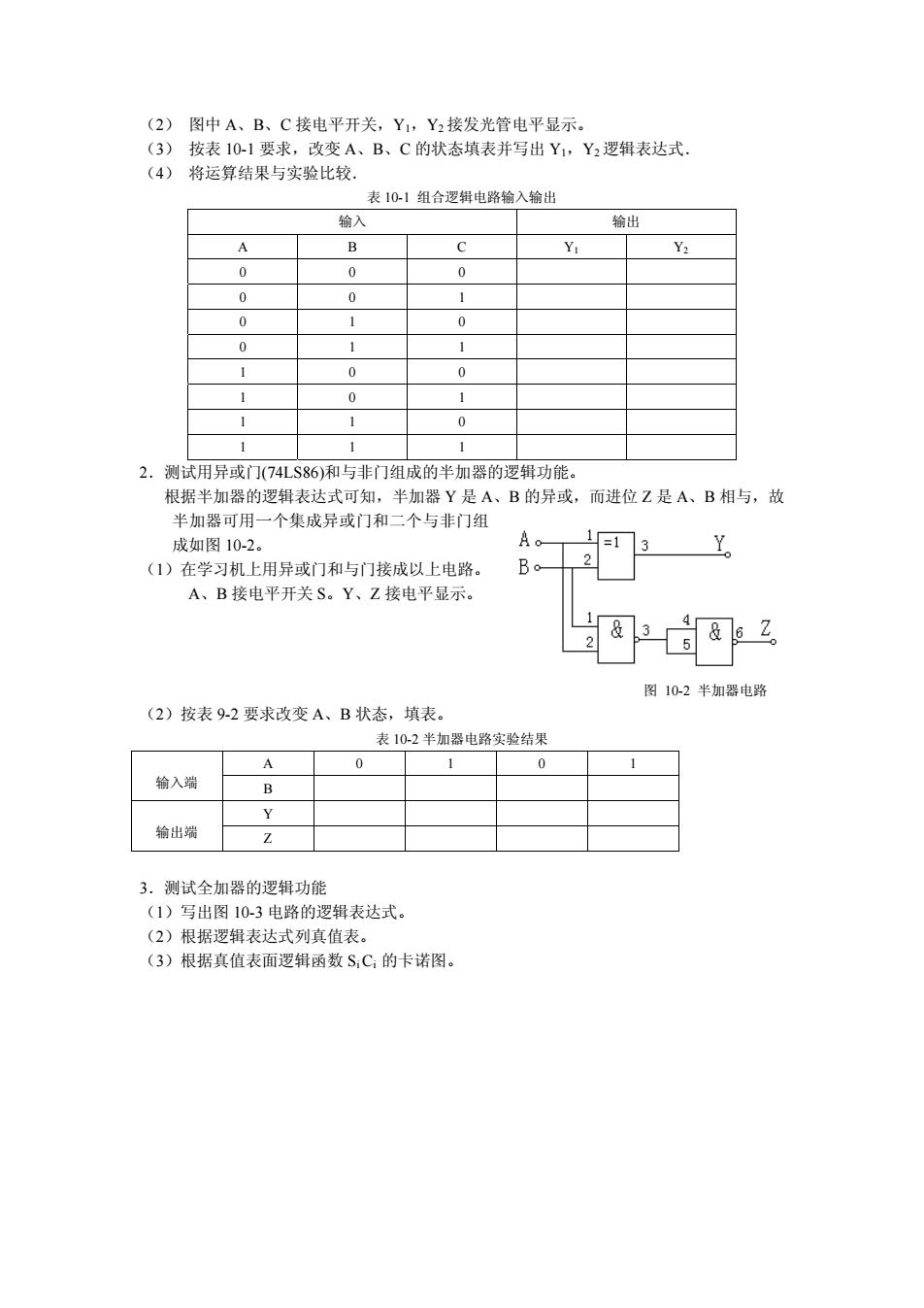

(2)图中A、B、C接电平开关,Y1,Y2接发光管电平显示。 (3)按表10-1要求,改变A、B、C的状态填表并写出Y1,Y2逻辑表达式. (4)将运算结果与实验比较 表10-1组合逻辑电路输入输出 输入 输出 A 0 Y Y2 0 0 0 0 0 1 0 1 0 0 1 1 0 0 1 0 1 1 0 1 2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。 根据半加器的逻辑表达式可知,半加器Y是A、B的异或,而进位Z是A、B相与,故 半加器可用一个集成异或门和二个与非门组 成如图10-2。 =13 2 (1)在学习机上用异或门和与门接成以上电路。 B。 A、B接电平开关S。Y、Z接电平显示。 图10-2半加器电路 (2)按表9-2要求改变A、B状态,填表。 表10-2半加器电路实验结果 A 0 输入端 B 输出端 Z 3.测试全加器的逻辑功能 (1)写出图10-3电路的逻辑表达式。 (2)根据逻辑表达式列真值表。 (3)根据真值表面逻辑函数SC:的卡诺图。(2) 图中 A、B、C 接电平开关,Y1,Y2 接发光管电平显示。 (3) 按表 10-1 要求,改变 A、B、C 的状态填表并写出 Y1,Y2 逻辑表达式. (4) 将运算结果与实验比较. 表 10-1 组合逻辑电路输入输出 输入 输出 A B C Y1 Y2 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。 根据半加器的逻辑表达式可知,半加器 Y 是 A、B 的异或,而进位 Z 是 A、B 相与,故 半加器可用一个集成异或门和二个与非门组 成如图 10-2。 (1)在学习机上用异或门和与门接成以上电路。 A、B 接电平开关 S。Y、Z 接电平显示。 图 10-2 半加器电路 (2)按表 9-2 要求改变 A、B 状态,填表。 表 10-2 半加器电路实验结果 A 0 1 0 1 输入端 B Y 输出端 Z 3.测试全加器的逻辑功能 (1)写出图 10-3 电路的逻辑表达式。 (2)根据逻辑表达式列真值表。 (3)根据真值表面逻辑函数 Si Ci 的卡诺图