正在加载图片...

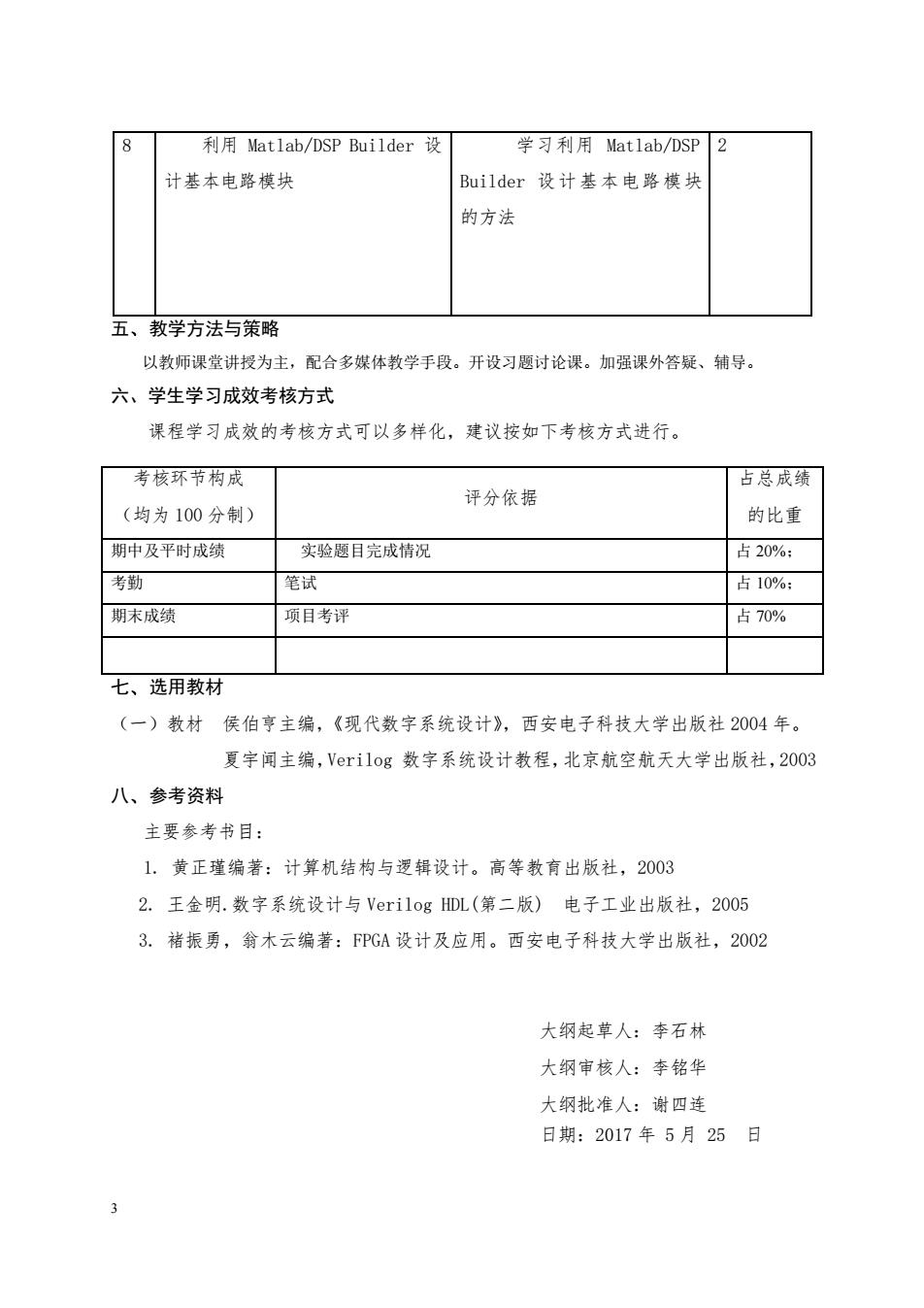

利用Matlab/DSP Builder设 学习利用Matlab/DsP2 计基本电路模块 Builder设计基本电路模块 的方法 五、教学方法与策略 以教师课堂讲授为主,配合多媒体教学手段。开设习题讨论课。加强课外答疑、辅导。 六、学生学习成效考核方式 课程学习成效的考核方式可以多样化,建议按如下考核方式进行。 考核环节构成 占总成绩 评分依据 (均为100分制) 的比重 期中及平时成绩 实验题目完成情况 占20%: 考勒 笔试 占10%: 期末成绩 项目考评 占70% 七、选用教材 (一)教材侯伯亨主编,《现代数字系统设计》,西安电子科技大学出版社2004年。 夏宇闻主编,Verilog数字系统设计教程,北京航空航天大学出版社,2003 八、参考资料 主要参考书目: 1.黄正瑾编著:计算机结构与逻辑设计。高等教育出版社,2003 2.王金明.数字系统设计与Verilog HDL(第二版)电子工业出版社,2005 3.褚振勇,翁木云编著:FPGA设计及应用。西安电子科技大学出版社,2002 大钢起草人:李石林 大纲审核人:李铭华 大纲批准人:谢四连 日期:2017年5月25日 3 8 利用 Matlab/DSP Builder 设 计基本电路模块 学习利用 Matlab/DSP Builder 设计基本电路模块 的方法 2 五、教学方法与策略 以教师课堂讲授为主,配合多媒体教学手段。开设习题讨论课。加强课外答疑、辅导。 六、学生学习成效考核方式 课程学习成效的考核方式可以多样化,建议按如下考核方式进行。 七、选用教材 (一)教材 侯伯亨主编,《现代数字系统设计》,西安电子科技大学出版社 2004 年。 夏宇闻主编,Verilog 数字系统设计教程,北京航空航天大学出版社,2003 八、参考资料 主要参考书目: 1. 黄正瑾编著:计算机结构与逻辑设计。高等教育出版社,2003 2. 王金明.数字系统设计与 Verilog HDL(第二版) 电子工业出版社,2005 3. 褚振勇,翁木云编著:FPGA 设计及应用。西安电子科技大学出版社,2002 大纲起草人:李石林 大纲审核人:李铭华 大纲批准人:谢四连 日期:2017 年 5 月 25 日 考核环节构成 (均为 100 分制) 评分依据 占总成绩 的比重 期中及平时成绩 实验题目完成情况 占 20%; 考勤 笔试 占 10%; 期末成绩 项目考评 占 70%